实验要求

模块功能应包括二进制码计数器的产生、由二进制码产生格雷码、所产生的格雷码再次转换为二进制码等逻辑部分。

该项目由一个功能模块和一个testbench组成。其中功能模块的端口信号如下表所示

格雷码表

| 二进制 | 格雷码 |

|---|---|

| 0000 | 0000 |

| 0001 | 0001 |

| 0010 | 0011 |

| 0011 | 0010 |

| 0100 | 0110 |

| 0101 | 0111 |

| 0110 | 0101 |

| 0111 | 0100 |

| 1000 | 1100 |

| 1001 | 1101 |

| 1010 | 1111 |

| 1011 | 1110 |

| 1100 | 1010 |

| 1101 | 1011 |

| 1110 | 1001 |

| 1111 | 1000 |

GrayCounter

module GrayCounter(

input clk_50M,

input rst_n,

output reg[3:0]gray_dout,

output reg[3:0]gray_count

);

always@(posedge clk_50M or negedge rst_n)

if(!rst_n) begin

gray_dout <= 4'b0000;

gray_count <= 4'b0000; // 复位计数器

end

else begin

case(gray_dout)

4'b0000 : begin

gray_dout <= 4'b0001;

gray_count <=4'b0001;

end

4'b0001 : begin

gray_dout <= 4'b0011;

gray_count <=4'b0010;

end

4'b0011 : begin

gray_dout <= 4'b0010;

gray_count <=4'b0011;

end

4'b0010 : begin

gray_dout <= 4'b0110;

gray_count <=4'b0100;

end

4'b0110 : begin

gray_dout <= 4'b0111;

gray_count <=4'b0101;

end

4'b0111 : begin

gray_dout <= 4'b0101;

gray_count <=4'b0110;

end

4'b0101 : begin

gray_dout <= 4'b0100;

gray_count <=4'b0111;

end

4'b0100 : begin

gray_dout <= 4'b1100;

gray_count <=4'b1000;

end

4'b1100 : begin

gray_dout <= 4'b1101;

gray_count <=4'b1001;

end

4'b1101 : begin

gray_dout <= 4'b1111;

gray_count <=4'b1010;

end

4'b1111 : begin

gray_dout <= 4'b1110;

gray_count <=4'b1011;

end

4'b1110 : begin

gray_dout <= 4'b1010;

gray_count <=4'b1100;

end

4'b1010 : begin

gray_dout <= 4'b1011;

gray_count <=4'b1101;

end

4'b1011 : begin

gray_dout <= 4'b1001;

gray_count <=4'b1110;

end

4'b1001 : begin

gray_dout <= 4'b1000;

gray_count <=4'b1111;

end

4'b1000 : begin

gray_dout <= 4'b0000;

gray_count <=4'b1111;

end

default:begin

gray_dout <= 4'bx;

gray_count <= 4'bx;

end

endcase

end

endmodule

GrayCounter_tb

`timescale 1 ns/ 1 ns

module GrayCounter_tb();

reg clk_50M;

reg rst_n;

wire [3:0] gray_dout;

wire [3:0] gray_count;

GrayCounter i1 (

.clk_50M(clk_50M),

.gray_dout(gray_dout),

.rst_n(rst_n),

.gray_count(gray_count)

);

initial

begin

rst_n = 0;

clk_50M = 0;

#5 rst_n = 1;

#100 $stop;

end

always #5 clk_50M = ~clk_50M;

initial $monitor($time,"-> \t now state of gray is : %b,now state of bin_count is:%b",gray_dout,gray_count);

endmodule

输出结果

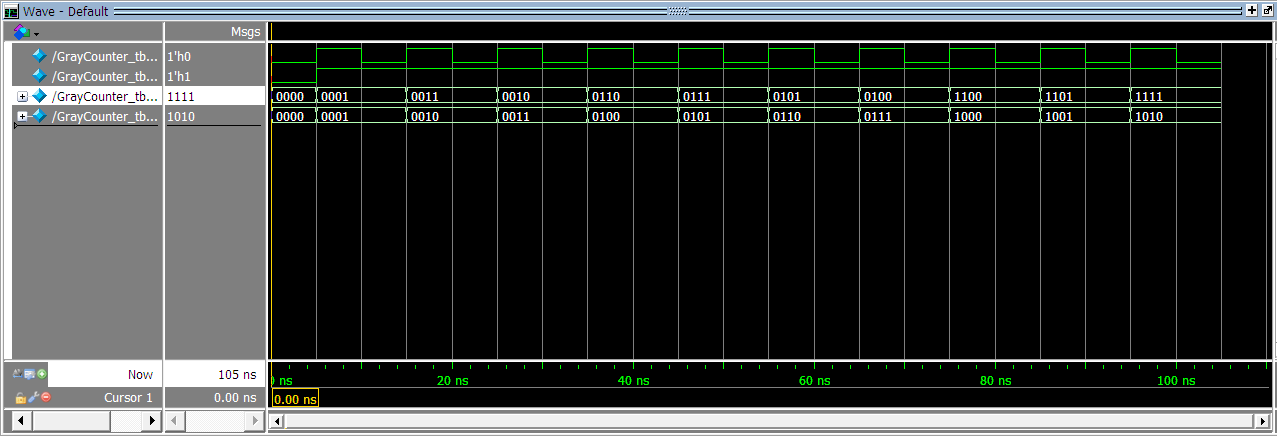

整体波形

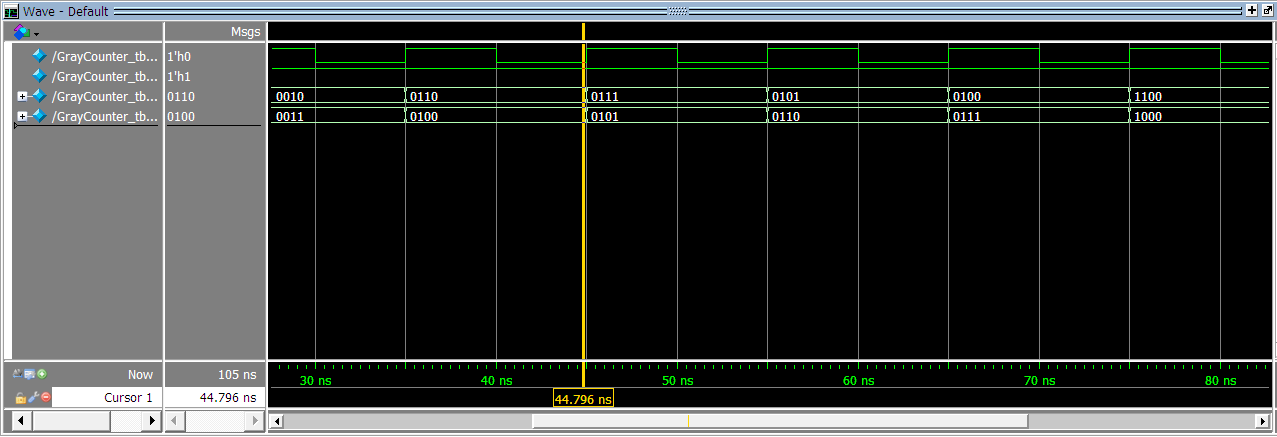

部分波形