实验要求

该项目主要实现一个占空比为50%的时钟四分频分频器。模块功能应包括主时钟计数、分频时钟翻转等逻辑部分。

该项目由一个功能模块和一个testbench组成。其中功能模块的端口信号如下表所示。

clk_div

module clk_div(clk, rstn, clk_out);

input clk, rstn;

output clk_out;

reg clk_out;

reg [1:0] cnt;

always @(posedge clk or negedge rstn)

begin

if (!rstn) begin // cnt_reset

cnt <= 1'b0;

end

else if (cnt == 2'b11) begin

cnt <= 1'b0;

end

else begin

cnt <= cnt + 1'b1;

end

end

always @(posedge clk or negedge rstn)

begin

if (!rstn) begin

clk_out <= 1'b0;

end

else if(cnt == 1'b1) begin

clk_out <= !clk_out;

end

else if (cnt == 2'b11) begin

clk_out <= !clk_out;

end

else begin

clk_out <= clk_out;

end

end

endmodule

clk_div_tb

`timescale 1ns/1ns

module clk_div_tb;

reg clk, rst;

wire clk_out;

clk_div dut(.clk(clk),

.rstn(rst),

.clk_out(clk_out)

);

initial begin

clk <= 0;

forever begin

#5 clk <= ~clk;

end

end

initial begin

#10 rst <= 0;

repeat(2) @(posedge clk);

rst <= 1;

end

initial begin

#500 $stop;

end

endmodule

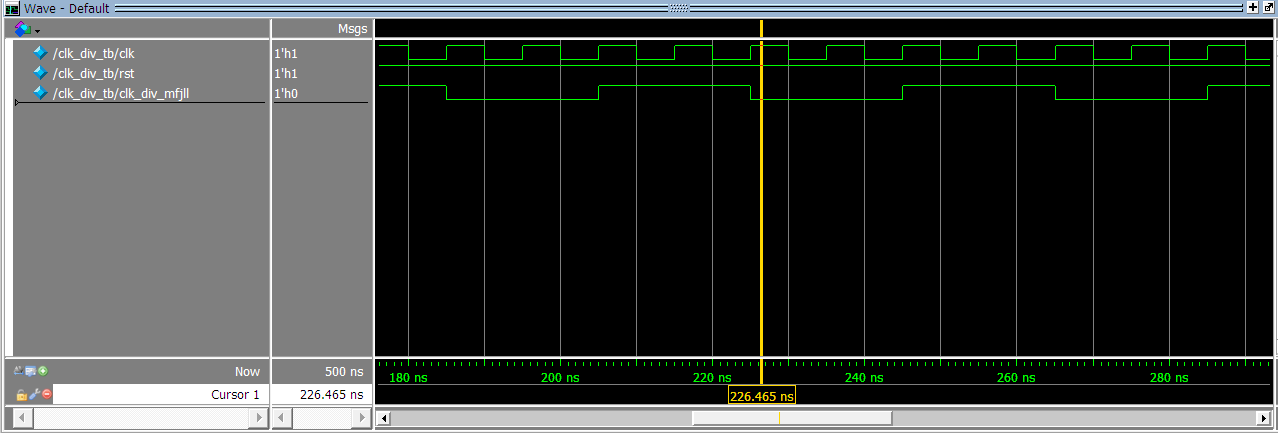

完整波形

部分波形