目录

学习目标:

提示:这里可以添加学习目标

1.能够描述基本 MOS开关:nmos.pmos和cmos。

2.理解双向传输开关、电源和地的建模方法。

3.识别阻抗MOS开关。

4.解释在基本MOS 开关和双向传输开关上说明延迟的方法。

5.在Verilog 中,用所提供的开关建立基本开关级电路。

学习内容:

提示:这里可以添加要学的内容

1.MOS开关

Verilog 提供了各种语言结构,可以为开关级电路建立模型,MOS晶体管级数字电路可以用这些最基本的电路模型元件'来描述,

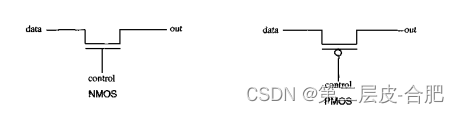

可以用关键字定义nmos和pmos晶体管建模,关键字pmos用于pmos建模,

信号out的值由信号data和control的值确定。out的逻辑值如表11.1所示。信号data和control的不同组合导致这两个开关输出1,0或者z或x、逻辑值(如果不能确定输出为1或0,就有可能输出z值或×值)。符号L代表О或z、H代表1或z。

2.CMOS开关

信号ncontrol和pcontrol通常是互补的。当信号ncontrol为1且pcontrol信号为О时,开关导通。如果信号ncontrol为0且pcontrol为1、则开关的输出为高阻值。CMOS门本质上是两个开关(NMOS和 PMOS )的组合体。

因为CMOS开关由NMOS 和 PMOS开关派生而来,所以给定data,ncontrol和 pcontrol 的信号值就可以根据表111推断出CMOS开关的输出值。

3.双向开关

NMOS.PMOS 和 CMOS门都是从漏极向源极导通,是单向的。在数字电路中,双向导通的器件很重要。对双向导通的器件而言,其两边的信号都可以是驱动信号。通过设计双向开关就可以实现双向导通的器件。有三个关键字用来定义双向开关:tran,tranif0和tranif1,

4.电源和地

设计晶体管级电路时需要源极( Vdd,逻辑1)和地极(Vss,逻辑О)。源极和地极用关键字supply1和 supplyo来定义。

源极类型 supply1相当于电路中的Vdd,并将逻辑Ⅰ放在网表中。源极类型supply0相当于地或Vss,并将逻辑О放在网表中。在整个模拟过程中,supply1和 supplyO始终为网表提供逻辑1值和逻辑О值。

5.阻抗开关

前面所讨论的MOS,CMOS 和双向开关可以用相应的阻抗器件建模。阻抗开关比一-般的开关具有更高的源极到漏极的阻抗,且在通过它们传输时减少了信号强度。在相应的一般开关关键字前加带r前缀的关键字,即可声明阻抗开关。阻抗开关与一般开关的语法类似。

在一般开关和阻抗开关之间有两个主要区别:源极到漏极的阻抗和传输信号强度的方式。关于Verilog 中的强度级。

阻抗器件具有较高的源极到漏极阻抗。一般开关的面极到漏极阻抗较低。

阻抗开关在传递信号时减少了信号强度,其变化如下所示。一般开关从输入到输出一直保持强度级别不变。有一点例外,如果输入supply强度、则输出strong 强度。表11.2显示出由于阻抗开关导致的强度缩减。

6.开关中的延迟说明

可以为通过这些开关级元件的信号指定延迟。延迟是可选项,它只能紧跟在开关的关键字之后。延迟说明类似于之前中讨论的Rise,Fall和Turn-off延迟。可以为开关指定0个、1个、2个或者3个延迟,所示。

specify块: 也可以给使用开关设计的模块指定路径延迟(引脚到引脚的延迟〉以及时序检查。用specify块可以描述路径延迟。在之后中详细讨论了路径延迟说明、它在开关级模型中也完全适用。

学习时间:

提示:这里可以添加计划学习的时间例如:

20230618

学习总结:

提示:这里统计学习计划的总量

1.开关级建模处于很低的设计抽象层次。只在很少的情况下,比如在设计者需要定制自己的叶级元件(即最基本的元件)时,才使用开关级建模。随着电路复杂度的增加,这个级别的Verilog 设计越来越少见;

2.MOS,CMOS,双向1.关和supply1,supplyO源可用于设计任意的开关级电路。CMOS开关是MOS开关的一种组合;

3.延迟对开关元件来说是可选的。对于不同的双向器件,有不同的延迟解释。