1、逻辑电路基础

1.1.1、逻辑代数

1.1.2 、布尔代数定理

1.1.3、真值表

真值表和逻辑门。针对逻辑函数所有可能的输入组合一一列出输出值,我们就可以得到真值表。对于组合逻辑电路,只要列出所有可能的输入和对应的输出值,就可以完整地描述电路功能。因此,电路功能通常使用真值表描述。输入的个数为n时,真值表的组合数为2”。真值表中,需要记入每组输入值所对应的输出值。

1.1.4、组合逻辑电路

逻辑电路分为组合逻辑电路和时序逻辑电路

**组合逻辑:**不包含记忆元件、某个时间的输出,取决于当时的输入;

任何逻辑电路都可以用积之和的表达式来描述:使用与或非组合而成的逻辑电路可以实现任何逻辑函数

1.1.5、时序逻辑电路

时序逻辑电路由组合逻辑电路与存储电路组成。组合逻辑电路为非必须。

存储器与锁存器是构成存储电路的基本逻辑单元。

双稳态(0,1)

时序逻辑:含有记忆元件的逻辑电路。在时序逻辑电路中,只知道当前的输入并不足以确定当前的输出。也就是说,时序逻辑电路是一种过去的电路状态也会对输出产生影响的逻辑电路。

**同步时序逻辑电路:**输入和内部状态的变化由时钟信号控制同步进行,而异步时序逻辑电路则不需要时钟信号。FPGA中多为同步时序

**异步时序逻辑电路:**不需要时钟信号(留坑)

米勒模型的输出由内部状态和输人共同决定,其状态数通常比摩尔模型的少,因此有电路规模较小的优点。然而由于输入会立刻反映到输出,所以逻辑元件或不等长的布线所带来的信号延迟等容易引起信号竞争,进而导致非预期的错误输出(冒险)

摩尔模型的输出仅由内部状态决定。相比之下,摩尔模型直接使用记忆状态的输出,因此电路速度快且不易发生冒险。但摩尔模型由于状态数量多,电路规模也相对较大

1.2.1、触发器(Filp Flop, FF)

触发器是一种只能储存1bit的存储单元,可用作时序逻辑电路的记忆元件。工作时由CLK(上升沿、下降沿)触发,将输入信号的变化传递到输出

简单来说,如果要更改输出信号,必须输入信号更改的同时,时钟信号也进行修改。

1.2.2、建立时间和保持时间(锁存器)

关于锁存器的相关知识,可以在该视频中进行了解。

锁存器(Latch)是一种对脉冲电平敏感的双稳态电路(0,1),一旦状态被确定,就能自行保持.直到有外部特定输人脉冲电平作用在电路一定位置时,才有可能改变状态。这种特性可以用于置入和存储1位二进制数据。

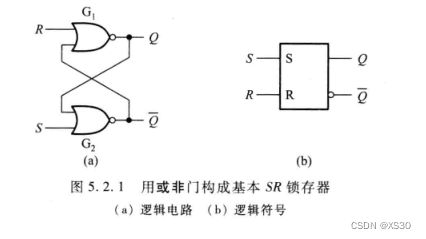

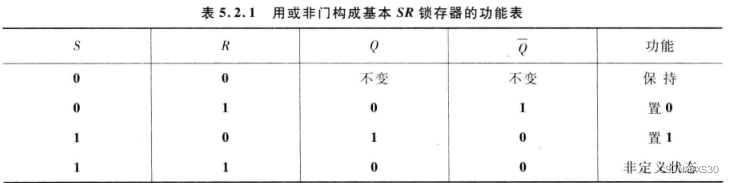

下图为用或非门组成的SR锁存器,

由R与Q非状态共同决定Q的状态,于是便有如下图2的真值表

关于各种逻辑门真值表,可以参考

或非门:即输入两者为假,输出为真,否则输出全为假。

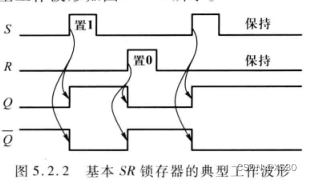

可以看出,当S=1时,Q=1,后S=0,直到R(复位信号)=1时,Q=0;

该功能可以作为保存数据功能使用,S=Signal;R=Reset;Q=Register

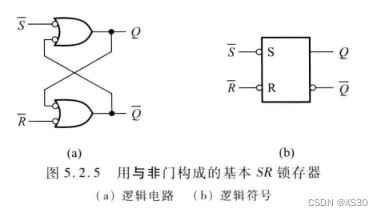

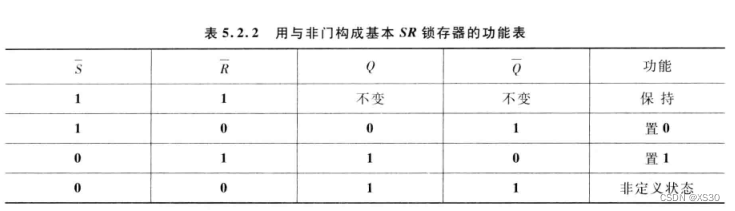

与非门SR锁存器

与非门:除非输入全为真,输出才会为假,否则全为真。(这里的输入端为S非、Q非)

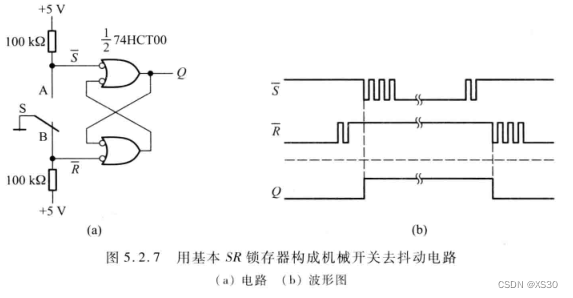

可以从以下应用中看出,由与非门所组成的基本SR锁存器,功能为使用S控制寄存器Q置高,通过R复位寄存器Q。

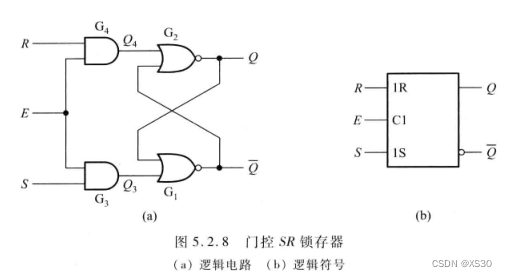

门控SR锁存器

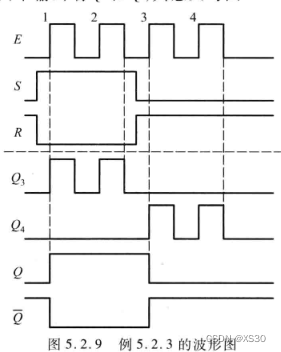

通过控制E端电平,可以实现多个锁存器同步的数据锁存。

可以看出E可以作为更新状态的控制器Enable。