前言

因为要期末考试了所以就将知识点进行了总结,把期末要考的知识点分章节进行划分,以至于我能取得一个好成绩。

第一章

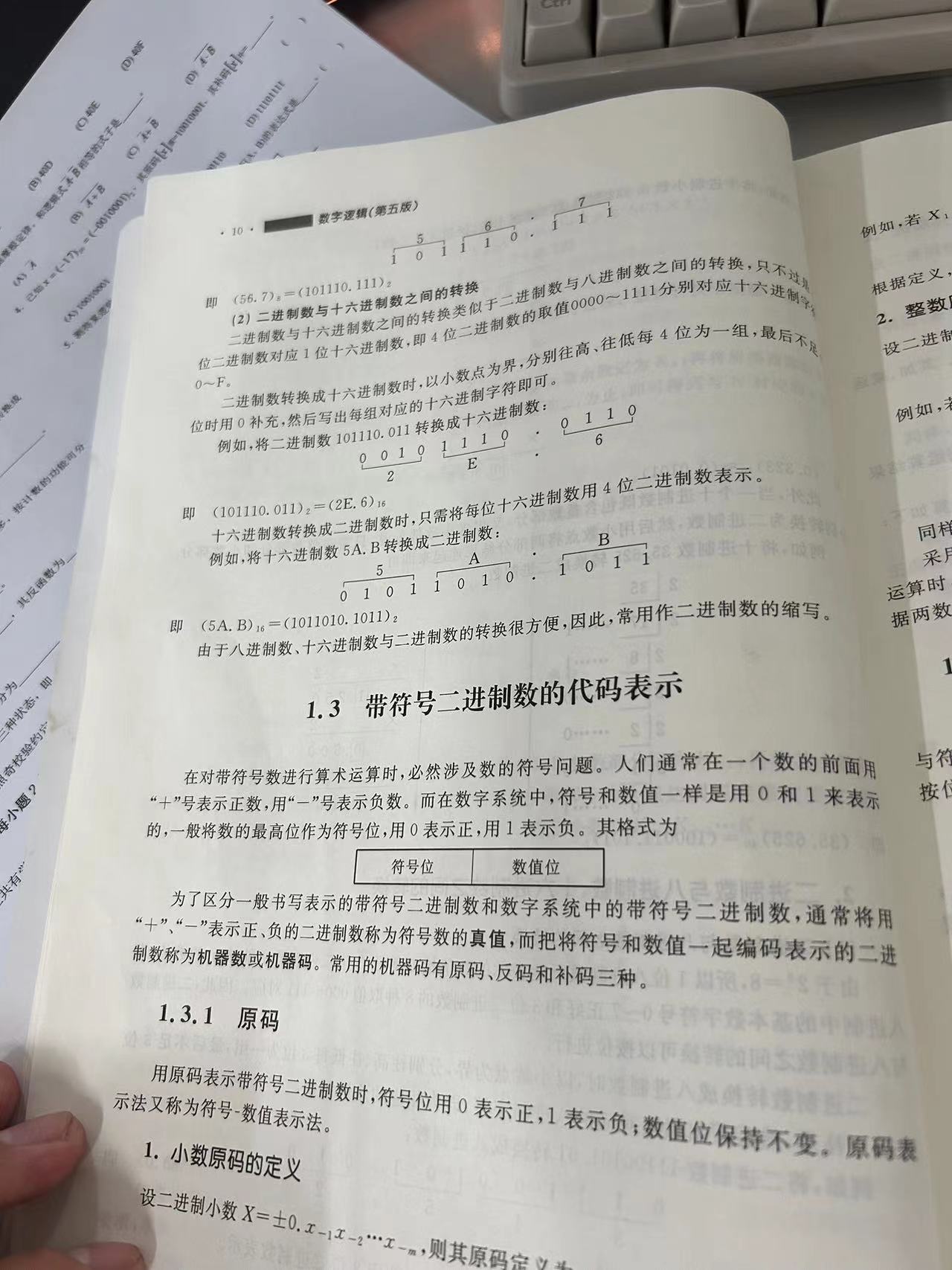

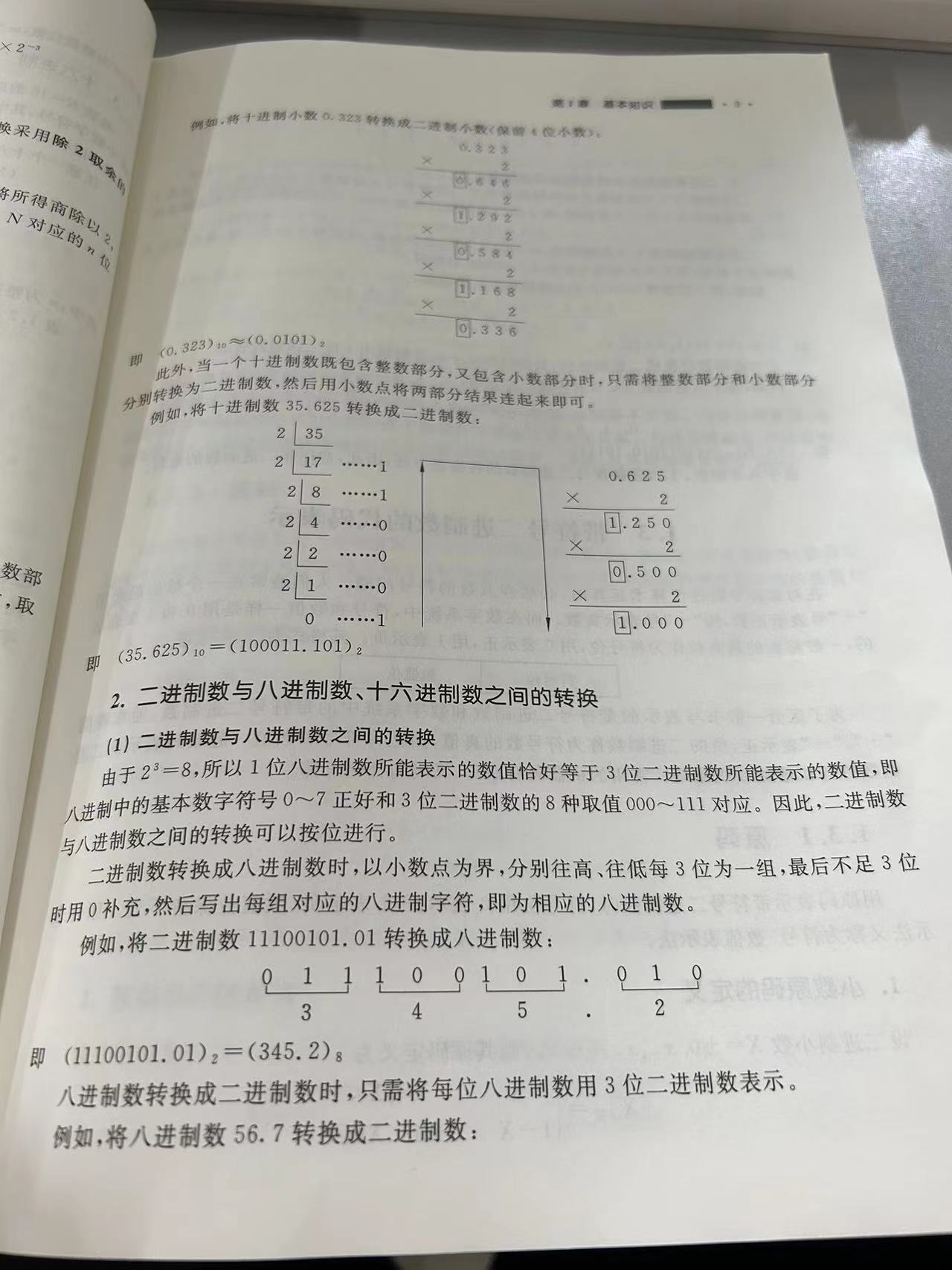

进制转换 8421码、2421码、余3码、格雷码;原码、反码、补码

奇偶校验码

第二章

1、5公理3运算3表示法8定理(包含律)3规则 记忆

2、异或和同或;与-或表达式和或-与表达式;最小项

3、函数化简

第三章

1、TTL:晶体管-晶体管逻辑

2、与、或、非门符号、图形 P76记忆图表

3、触发器:有两个互补的输出端Q和Q非。

第四章

1、逻辑电路按其是否具有记忆功能分为组合逻辑电路和时序逻辑电路。

P96 例4.2 4.4 4.9

2、输入信号经过不同路径到达输出端的时间有先后的现象为竞争现象,其使得输入信号的变化可能引起输入信号出现非预期的错误输出,这一现象称为险象。通常把不产生错误输出的竞争为非临界竞争,反之为临界竞争。

3、险象的消除:增加冗余法、增加惯性延时环节、选通法。

第五章

1、时序逻辑电路按其工作方式的不同,可分为同步时序逻辑电路和异步时序逻辑电路;根据电路的输出是否与输入直接相关,可分为Mealy型和Moore型;根据输入信号形式可分为脉冲型和电平型。

2、组合逻辑电路在任何时刻产生的稳定输出信号都仅与该时刻电路的输入信号相关;而时序逻辑电路在任何时刻产生的稳定输出信号不仅与电路该时刻的输入信号有关,而且与电路过去的输入信号有关。

P120 例5.1

第六章

1、异步时序逻辑电路的工作特点

无论输入信号是脉冲信号还是电平信号,对其变化过程均有一定约束。异步时序逻辑电路可分为脉冲异步时序逻辑电路和电平异步时序逻辑电路两种类型

第七章:

1、记忆:组合逻辑电路:译码器、编码器、全加器

非组合逻辑电路:寄存器

八路数据分配器,其地址输入端(选择控制端)有3个

2、使用最广泛的中规模组合逻辑集成电路有二进制并行加法器、译码器(二进制译码器、二-十进制译码器、数字显示译码器、3-8线译码器)、编码器、多路选择器和多路分配器等。

P187 例7.5

全减器:是实现对被减数、减数及来自相邻低位的借位进行减法运算,得到差及向相邻高位借位的逻辑电路。

3、多路选择器又称数据选择器或多路开关,用MUX表示。

P194 例7.8

多路分配器又称数据分配器,常用DEMUX表示,结构与MUX相反,单输入、多输出的逻辑部件

4、计数器是一种能在输入信号作用下依次通过预定状态的时序逻辑电路,按其工作方式可分为同步计数器和异步计数器;按其进位制可分为二进制计数器、十进制计数器和任意进制计数器;按其功能可分为加法计算器、减法计数器和加/减可逆计数器。一般具有计数、保存、清除和预置等功能。

P199 例7.12 7.13 P203 例7.15

5、把数字信号转换成模拟信号的器件称为数/模转换器,简称D/A转换器或DAC;把模拟信号转换成数字信号的器件称为模/数转换器,简称A/D转换器或ADC。

第八章

1、PLD为可编程逻辑器件,包括:PROM-可编程只读存储器;PLA-可编程逻辑阵列;PAL-可编程阵列逻辑。 GAL为通用阵列逻辑(均为低密度可编程逻辑器件),FPGA为现场可编程门阵列

根据集成度,通常将PLD分为LDPLD和HDPLD(高密度可编程逻辑器件 集成度>=1000门)

2、半导体存储器按其功能可分为:随机存取存储器RAM(读/写存储器)和只读存储器ROM(非易失性存储器)

3、内容不进行了解,记住每个简写对应的名称,可能会出两个填空题

总结

数字逻辑复习,期末考试冲冲冲!!!