基于《A Loosely-Coupled Arm and RISC-V Locksteping Technology》文章总结

一、lockstep技术分类

文中将lockstep技术总结成三类:系统级、分系统级和CPU级。系统级拥有两套不同的CPU、Caches和Memory,输入通过IO进入各自Memory和Caches,输出通过Checker比较结果;分系统级共享同一个Memory和IO,输入进入各自Cache,输出通过Checker比较结果;CPU级只有两套CPU内核,Cache和Memory均使用同一套。

二、ARM+RISC-V双核lockestep设计实现

2.1 总体架构

下图ARM+RISC-V双核lockstep实现架构,其中RISC-V使用了rocket chip五级流水,并添加了用于同步的xLockstep模块。上层软件将同一套程序通过两套编译器生成底层代码,分别分发给ARM和RISC-V,RISC-V在FPGA中实现。该架构不能完成指令级的错误纠正,只能实现错误检测和冗余备份功能。

xLockstep为该架构设计的重点,其内部结构如下图所示。该结构有四个接口:两个APB3总线和两个中断输出。结构内部有16个内部寄存器、1个timer、1个checker模块、1个FSM状态机和数据控制交互逻辑。所有寄存器均32bits位宽,2个状态寄存器为只读,具体寄存器含义如下。

2.2 内部寄存器

- 控制寄存器:用来控制系统运行,低6bits使用。

- bit_Enable: 置1使能工作,置0复位系统;

- bit_SynchroX: 置1开始同步两边CPU并对比数据,当其完成后自动回到0;

- bit_DataSel_x: 该2bit用于指示对比数据的数量;

- bit_EnInterrupt: 用于使能中断信号接口,当xLockstep完成对比中断就会拉高,直到bit_SynchroX位回0;

- bit_ErrorSolve: 用来通知xLockstep发现的错误CPU已经解决了。

- 状态寄存器:用来指示xLockstep系统当前状态,低4bits有效。

- bit_busy: 指示当前系统是否忙;

- bit_stateFSM_x: 指示内部FSM状态机当前值;

- TimeOut寄存器:用来给Timer模块赋初值。

- 数据寄存器:对比的数据。

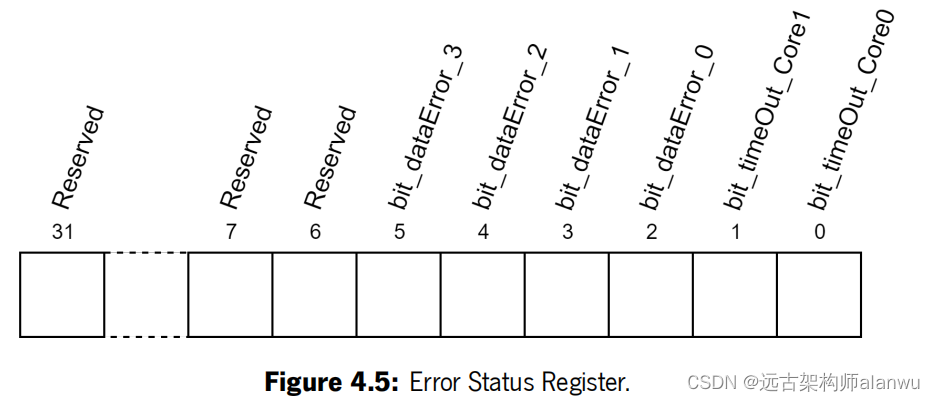

- 错误状态寄存器:用于指示系统错误。

- bit_timeOut_Corex: 如果timeout寄存器设置的时间内其中一个core没有达到checkpoint,那么将该bit位置1;

- bit_dataError_x: 用于指示数据寄存器的哪个寄存器数据比较结果出错;

2.3 FSM状态机

FSM状态机如下图所示,主要包括六个状态:Start、Idle、Synchro、Checker、Resume和Error。

系统上电复位后进入Start状态,Start状态为复位后状态,所有数据清空。Start状态等待两个core置位bit_Enable,只有两个都置位才会进入Idle状态,其中一个清0均会跳入Start状态。

Idle状态下,系统会将Timeout寄存器中的数值更新到Timer中,并更新两个状态寄存器。系统会不停检查控制寄存器中的设置,并根据控制寄存器数值进行相应的处理。如果其中一个core将bit_synchroX位置1,那么状态机会进入Synchro状态,也就是说此时至少一个core达到了checkpoint的位置。

Synchro状态下,系统使能timer计数,如果在规定时间内另一个核也进入到checkpoint位置并拉高bit synchroX,则状态机进入Checker状态。如果未能在规定时间内进入checkpoint,那么超时标志拉高,状态进入Error状态。

Checker状态下,系统将使能checker模块工作,并比较所有处理器的输出。如果输出不一致,Checker将置位错误标志并进入Error状态,如果比较一致,则置位EndOfCheck标志,并进入Resume状态。

进入Error状态后,CPU需要处理当前的错误,并在处理完成后置位bit_ErrorSolve信号,并重新通过bit_SynchroX同步。如果错误修复ErrorFix的标志拉高且bit_SynchroX回0,系统进入Idle状态。在错误状态下,系统将会更新状态和错误寄存器,并拉高中断。

在Resume状态下,系统更新状态寄存器和中断。系统会保持该状态直到bit_SynchroX被清除并置位continue(与非bit_Synchro0和bit_Synchro1)。

2.4 Timer模块

Timer模块用于同步双核,内部包括一个计数器。如果计数器达到timeout预设值而另一个core还没有达到checkpoint,那么会产生超时error并进入Error状态。如果没有错误发生,timer会停止计数,系统进入下一个状态。下图是Timer模块的结构图以及状态机。

其内部结构较为简单,状态机主要包括三个状态:Reset、Count和Timeout。Reset状态下计数器值为0,并在enable使能后进入count状态开始计数工作。count状态下,计数器持续计数直到达到timeout或enable关闭(另一个核达到checkpoint)。timeout状态下置位超时错误标志,并等待enable关闭进入reset状态。

2.5 Checker模块

Checker模块每个周期比较4 x 32bits寄存器结果,下图是该模块的结构和内部状态机。Enable使能数据对比,DataSelX用于指示对比寄存器的数量,EndofCheck用于指示对比结束,ErrorDataX用于指示各个寄存器数据对比结果是否有误。

状态机从Idle状态开始,如果Enable有效则进入ErrorClean状态。Idle状态下输出EndOfChecker和SelectDataX清0,直到输入Enable有效。ErrorClean状态只维持一个时钟周期,并在下一周期直接进入Compare状态。Compare状态下,数据开始通过Data_Core0和Data_Core1一拍拍进入Checker,直到对比结束,EndofData有效进入End状态。End状态下,状态机等待Enable拉低。

三、软件实现

3.1 API

xLockstep使用APB接口作为设备访问接口,主核和从核均通过各自的接口访问可见地址空间的寄存器。经过API封装后,上层应用程序可以轻松的访问内部寄存器。API封装的函数如下所示:

- XLOCKSTEP_init();

- XLOCKSTEP_synch();

- XLOCKSTEP_checker();

- XLOCKSTEP_resume();

- XLOCKSTEP_errorFix();

- XLOCKSTEP_config();

- XLOCKSTEP_getStatus();

- XLOCKSTEP_getErrorStatus();

3.2 Framework

由于主从核的异构,以及指令集的不同,程序难以做到周期级的指令对比,采用松耦合的checkpoint对比方法,能够有效保证双核的同步和回卷,下图显示这种异构的双核对比过程。

主从核执行同一套程序,但只有主核的程序运行结果会输出。系统首先会开始双核的同步过程,如果同步成功,系统会保存处理器信息并执行程序代码。当双方程序均运行到checkpoint时,系统会比较两个处理器的输出,如果没有错误则继续到下一个checkpoint。如果在下次比较时,其中的一个核产生了错误并在对比过程中检查出来,那么系统将会回卷到上一次正确checkpoint,并重新运行程序。

checkpoint到达后,系统需要将主从核的内容存储保存。由于ARM和RISCV都采用了load-store架构,程序首先会将memory中的数据load到寄存器,执行指令并将结果写回memory。需要保存的处理器信息包括:寄存器数值、memory数值、stack堆栈内容,这些内容的保存对于回卷操作至关重要。saveContext()函数被调用后,首先会保存寄存器文件、Frame Pointer和Stack Pointer。当上述内容保存完成后,还会保存PC值。

保存寄存器和stack,需要清楚处理器内部寄存器和堆栈如何工作,ARM Cortex-M3包括17个寄存器:R0-R12通用,R13用于SP,R14用于LR,R15用于PC,PSR用于程序状态指示。另外,M3使用R7作为FP,在程序调用过程中,SP和FP均会变化,过程如下图所示:

假设此时程序在主函数中,FP指向0x20008000地址,SP指向0x20007000地址,当程序调用function()函数后,FP指向0x20006FFC并将上一个FP位置写入该地址,SP也会指向新的地址。

RISCV包括32个寄存器:X0常值0,X1用于返回地址,X2用于SP,X3-X27通用,X28-X31备用。当function call发生时,同样需要保存上述寄存器和stack中的内容。上述的不一致性需要考虑,因为对比数据需要从保存的数据中提取,在发生错误回卷时,也需要考虑恢复的内容。尽管RISCV和ARM采用了不同的指令集,但系统保存FP和SP的方式是相似的。