RISC-V技术杂谈

RISC-V(发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA)。

与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件。虽然这不是第一个开源指令集,但具有重要意义,因为其设计使其适用于现代计算设备(如仓库规模云计算机、高端移动电话和微小嵌入式系统)。设计者考虑到了这些用途中的性能与功率效率。该指令集还具有众多支持的软件,这解决了新指令集通常的弱点。

该项目2010年始于加州大学伯克利分校,但许多贡献者是该大学以外的志愿者和行业工作者。

RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。

截至2017年5月,RISC-V已经确立了版本2.22的用户空间的指令集(userspace ISA),而特权指令集(privileged ISA)也处在草案版本1.10。

2022年6 月 21 日,RISC-V 国际组织宣布了 2022 年的首批四项规格和扩展的批准 ——RISC-V 高效跟踪(E-Trace)、RISC-V 主管二进制接口(SBI)、RISC-V 统一可扩展固件接口(UEFI)规格,以及 RISC-V Zmmul 纯乘法扩展。

参考文献链接

https://baike.baidu.com/item/RISC-V/22606314?fr=aladdin

https://special.wch.cn/zh_cn/RISCV_MCU_Index/

https://baijiahao.baidu.com/s?id=1730142571773859647&wfr=spider&for=pc

RISC-V(读作“RISC-FIVE”)是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),V表示为第五代RISC(精简指令集计算机),表示此前已经有四代RISC处理器原型芯片。每一代RISC处理器都是在同一人带领下完成,那就是加州大学伯克利分校的David A. Patterson教授。与大多数ISA相反,RISC-V ISA可以免费地用于所有希望的设备中,允许任何人设计、制造和销售RISC-V芯片和软件。虽然不是第一个开源的指令集(ISA),但很重要,因为是第一个被设计成可以根据具体场景、可以选择适合的指令集的指令集架构。基于RISC-V指令集架构可以设计服务器CPU,家用电器cpu,工控cpu和用在比指头小的传感器中的cpu。

完全开源

对指令集使用,RISC-V基金会不收取高额的授权费。开源采用宽松的BSD协议,企业完全自由免费使用,同时也容许企业添加自有指令集拓展而不必开放共享以实现差异化发展。

架构简单

RISC-V架构秉承简单的设计哲学。体现为:

在处理器领域,主流的架构为x86与ARM架构。x86与ARM架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟,但作为商用的架构,为了能够保持架构的向后兼容性,其不得不保留许多过时的定义,导致其指令数目多,指令冗余严重,文档数量庞大,所以要在这些架构上开发新的操作系统或者直接开发应用门槛很高。而RISC-V架构则能完全抛弃包袱,借助计算机体系结构经过多年的发展已经成为比较成熟的技术的优势,从轻上路。RISC-V基础指令集则只有40多条,加上其他的模块化扩展指令总共几十条指令。 RISC-V的规范文档仅有145页,而“特权架构文档”的篇幅也仅为91页。

易于移植*nix

现代操作系统都做了特权级指令和用户级指令的分离,特权指令只能操作系统调用,而用户级指令才能在用户模式调用,保障操作系统的稳定。RISC-V提供了特权级指令和用户级指令,同时提供了详细的RISC-V特权级指令规范和RISC-V用户级指令规范的详细信息,使开发者能非常方便的移植linux和unix系统到RISC-V平台。

模块化设计

RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而试图通过一套统一的架构满足各种不同的应用场景。用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,比如针对于小面积低功耗嵌入式场景,用户可以选择RV32IC组合的指令集,仅使用Machine Mode(机器模式);而高性能应用操作系统场景则可以选择譬如RV32IMFDC的指令集,使用Machine Mode(机器模式)与User Mode(用户模式)两种模式。

完整的工具链

对于设计CPU来说,工具链是软件开发人员和cpu交互的窗口,没有工具链,对软件开发人员开发软件要求很高,甚至软件开发者无法让cpu工作起来。在cpu设计中,工具链的开发是一个需要巨大工作量的工作。如果用RISC-V来设计芯片,芯片设计公司不再担心工具链问题,只需专注于芯片设计,RISC-V社区已经提供了完整的工具链,并且RISC-V基金会持续维护该工具链。当前RISC-V的支持已经合并到主要的工具中,比如编译工具链gcc, 仿真工具qemu等

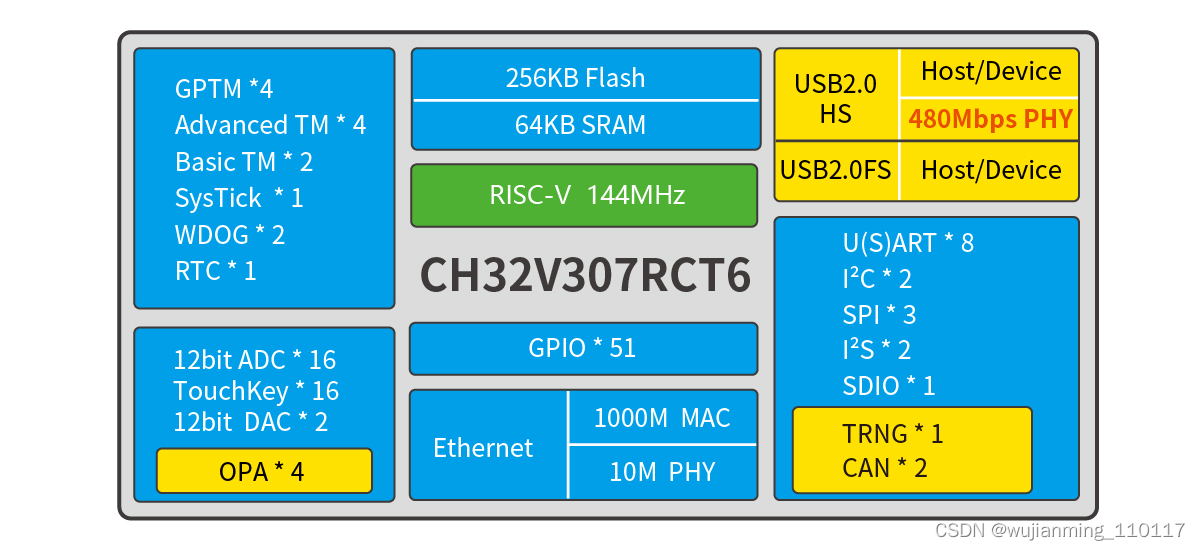

互联型RISC-V单片机CH32V307

概述

CH32V305/7系列是基于32位RISC-V设计的互联型微控制器,配备了硬件堆栈区、快速中断入口,在标准RISC-V基础上大大提高了中断响应速度。加入单精度浮点指令集,扩充堆栈区,具有更高的运算性能。扩展串口UART数量到8组,电机定时器到4组。提供USB2.0高速接口(480Mbps)并内置了PHY收发器,以太网MAC升级到千兆并集成了10M-PHY模块。

系统框图

产品特点

• 青稞V4F处理器,最高144MHz系统主频

• 支持单周期乘法和硬件除法,支持硬件浮点运算(FPU)

• 64KB SRAM,256KB Flash

• 供电电压:2.5/3.3V,GPIO单元独立供电

• 多种低功耗模式:睡眠、停止、待机

• 上/下电复位、可编程电压检测器

• 2组18路通用DMA

• 4组运放比较器

• 1个随机数发生器TRNG

• 2组12位DAC转换

• 2单元16通道12位ADC转换,16路触摸按键TouchKey

• 10组定时器

• USB2.0全速OTG接口

• USB2.0高速主机/设备接口(480Mbps 内置PHY)

• 3个USART接口和5个UART接口

• 2个CAN接口(2.0B主动)

• SDIO接口、FSMC接口、DVP数字图像接口

• 2组IIC接口、3组SPI接口、2组IIS接口

• 千兆以太网控制器ETH(内置10M PHY)

• 80个I/O口,可以映射到16外部中断

• CRC计算单元,96位芯片唯一ID

• 串行2线调试接口

• 封装形式:LQFP64M、LQFP100

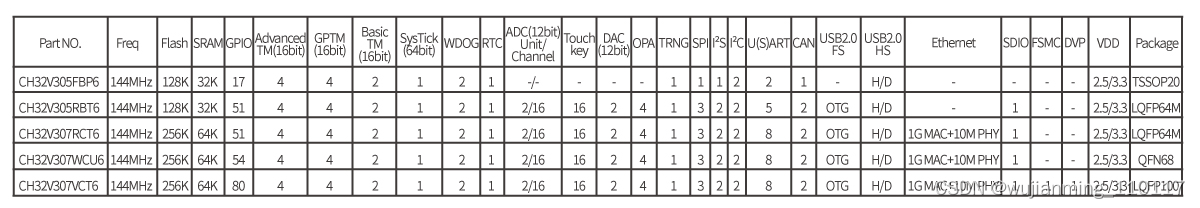

选型指南

开发资料

1、数据手册:CH32V20x_30xDS0.PDF,CH32FV2x_V3xRM.PDF

2、CH32V307评估板说明及参考应用例程:CH32V307EVT.ZIP

3、集成开发环境(IDE):MounRiver Studio(MRS)

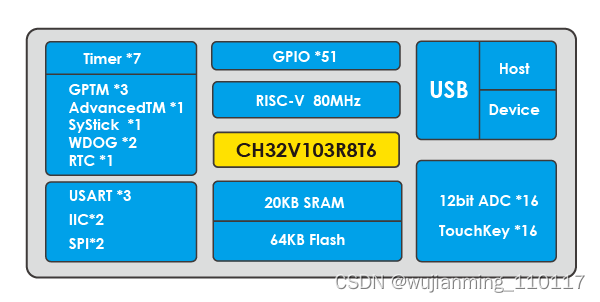

32位通用增强型RISC-V单片机 CH32V103

概述

CH32V103系列是以RISC-V3A处理器为核心的32位通用微控制器,该处理器是基于RISC-V开源指令集设计。片上集成了时钟安全机制、多级电源管理、通用DMA控制器。此系列具有1路USB2.0主机/设备接口、多通道12位ADC转换模块、多通道TouchKey、多组定时器、多路IIC/USART/SPI接口等丰富的外设资源。

系统框图

产品特点

• 青稞V3A处理器,最高80MHz系统主频;

• 支持单周期乘法和硬件除法;

• 20KB SRAM,64KB CodeFlash;

• 供电范围:2.7V ~ 5.5V,GPIO同步供电电压;

• 多种低功耗模式:睡眠/停止/待机;

• 上电/断电复位(POR/PDR);

• 可编程电压监测器(PVD);

• 7通道DMA控制器;

• 16路TouchKey通道监测;

• 16路12位ADC转换通道;

• 7个定时器;

• 1个USB2.0主机/设备接口(全速和低速);

• 2个IIC接口(支持SMBus/PMBus);

• 3个USART接口;

• 2个SPI接口(支持Master和Slave模式);

• 51个I/O口,所有的I/O口都可以映射到16个外部中断;

• CRC计算单元,96位芯片唯一ID;

• 串行单线调试(SWD)接口;

• 封装形式:LQFP64M、LQFP48、QFN48。

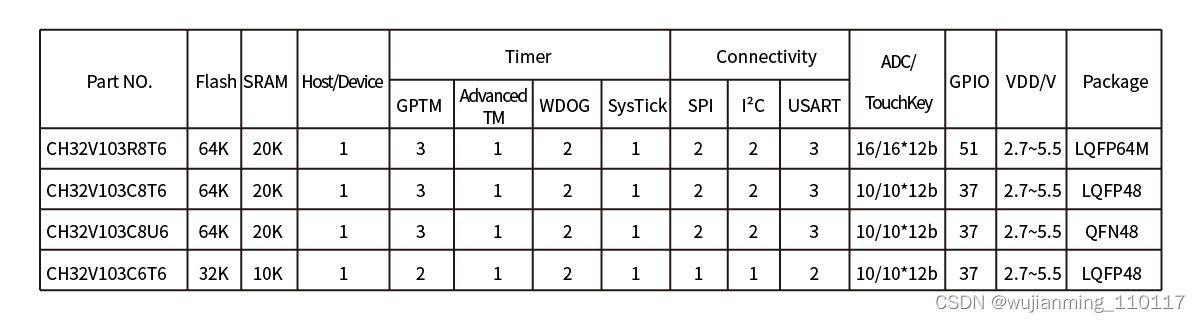

选型指南

开发资料

- 产品手册:CH32V103DS0.PDF,CH32xRM.PDF

- CH32V103评估板说明及参考应用例程:CH32V103EVT.ZIP

- 集成开发环境(IDE):MounRiver Studio(MRS)

USB3.0超高速U盘+蓝牙锁

概述

U盘,一种微型高容量移动存储产品,具有即插即用、无需物理驱动器、便于携带等优点。随着磁盘存储技术、闪存技术、通用串行总线技术的发展,U盘在速度、接口、容量、功耗等方面相应提升变化,成为各领域进行数据转移、存储、备份功能的首选工具。在此基础上,加密U盘、启动U盘、多分区U盘等多样功能产品也应运而生,丰富便捷了生活。

参考设计及产品

CH569 MCU资源上配有EMMC卡控制器和USB3.0 OTG控制器及收发器,通过EMMC接口挂载SD/TF/EMMC卡后即可具备U盘设计的基本物理资源。USB口作为设备口,插入USB主机端口后,系统得到供电5V,通过DC-DC转换为3.3V电压供应给CH569芯片和存储卡(一般都是3.3V系统)。

硬件设计上,CH569内置双层DMA架构,两路DMA实时并发处理高速数据(如USB3.0端、EMMC卡端)和低速数据(如MCU、定时器等),互不影响;中断模式提供优先级抢占和高速直通方式;接口模式上采用通知优先方式,将软件处理和硬件传输同步进行,提高整体速度性能。

软件设计上,缓冲区资源共享,划分队列管理,USB3.0端数据和EMMC卡数据只进行DMA地址修改,不参与任何数据拷贝,减少MCU处理时间;添加了EMMC卡协议命令处理及USB3.0设备端命令响应过程。

经实测,使用一款16G EMMC卡作为存储介质(工作在HS200模式下),在Win10平台下进行大数据拷贝,读出速度不低于90MB/s,写入速度不低于40MB/s。读写速度尤其是写速度主要受限于EMMC卡本身的存储延迟,可通过选择更快的存储介质做速度提升。

此外,启用片上AES/SM4对称算法加解密模块,可以将普通U盘扩展为数据加密存储U盘,正确的密钥下才可见磁盘或数据。

低速接口外挂一个低成本的蓝牙MCU(如CH573、CH579)或者便捷的蓝牙模块(如CH9140),将扩展无线解锁/锁定磁盘功能。

其它片上资源扩展,如使用Ethernet实现数据共享;DVP接口实现UVC摄像头;HSPI接口通讯FPGA功能等等。

RISC-V架构作为一个开源、免费的架构,这几年确实受到了全球厂商们的关注和使用,目前RISC-V基金会成员已有超过2000家,覆盖了70个国家。

像intel这样的大佬,都做出了违背祖宗的决定,加入RISC-V架构阵营了,甚至想着要将X86架构与RISC-V架构一起应用到CPU或/SoC中去。

而国内的芯片企业们就更加热情了,毕竟开源的、免费的不会被卡脖子。

像阿里旗下的平头哥、华为海思、兆易创新、华米科技、全志科技、芯来科技、格兰仕、晶心科技等众多的厂都纷纷入局,推出了基于RISC-V的IP核或芯片。

有很多网友认为,我们最应该努力发展RISC-V架构,这样就能够慢慢摆脱对X86、ARM架构的依赖,让RISC-V成为中国芯的主流。

但发展RISC-V架构的芯片,真的就能够让中国芯不再依赖X86、ARM架构?我觉得你还是想多了,就算最终RISC-V架构与X86、ARM形成三足鼎立之势,RISC-V架构也替代不了X86、ARM。

先说X86架构,X86架构是复杂指令集,主要用于PC产业,并且地位非常稳固,虽然ARM架构也经常踩过界,但简单指令集,在PC领域上还是无法与复杂指令集比,再加上Wintel的坚固联盟,其它架构,无法取代X86的位置,RISC-V当然也不行。

再说说ARM架构,这是简单指令集,功耗低、主要用于手机、移动设备等。RISC-V在一定程度上可以替代ARM,毕竟RISC-V也是简单指令集。

但是ARM架构与安卓已经形成了一个强大的生态联盟,称之为A-A生态,需要生态的设备,肯定会使用ARM,而不是RISC-V。

所以目前像RISC-V架构,更多的是用在不需要生态的物联网设备上,这些设备更多的是一些边缘化的设备。

RISC-V开源有开源的好处,但也因为开源,所有的组织和个人,都可以基于RISC-V进行修改,最终导致RISC-V架构或者生态其实是割裂的,很难形成一个真正统一的生态圈出来。

所以最终是无法去替代拥有Wintel联盟的X86架构,无法替代拥有A-A联盟的ARM架构,最好的结果也是三足鼎立,但要说有了RISC-V,就不需要X86、ARM架构,那就是真的想多了。

参考文献链接

https://baike.baidu.com/item/RISC-V/22606314?fr=aladdin

https://special.wch.cn/zh_cn/RISCV_MCU_Index/

https://baijiahao.baidu.com/s?id=1730142571773859647&wfr=spider&for=pc