1.6.芯片设计趋势

我们将希望在未来的SoC项目中使用我们的原型环境,但是这些项目会是什么样子的呢?

了解芯片设计的八个主要趋势将导致对未来的项目的更好的准备和更灵活的内部原型方法。

推动半导体设计需求的八个主要趋势是:

- 进一步小型化到更小的技术节点。

- 整体设计的减少就开始了。

- 可编程性结合了嵌入式软件内容的快速增加。

- IP重用。

- 应用程序的特异性。

- 采用多核架构。

- 低功率。

- 芯片的模拟/混合信号部分的增加。

所有这些都对原型需求产生了深远的影响,我们将快速地查看它们及其支持的趋势数据

1.6.1.小型化到更小的技术节点

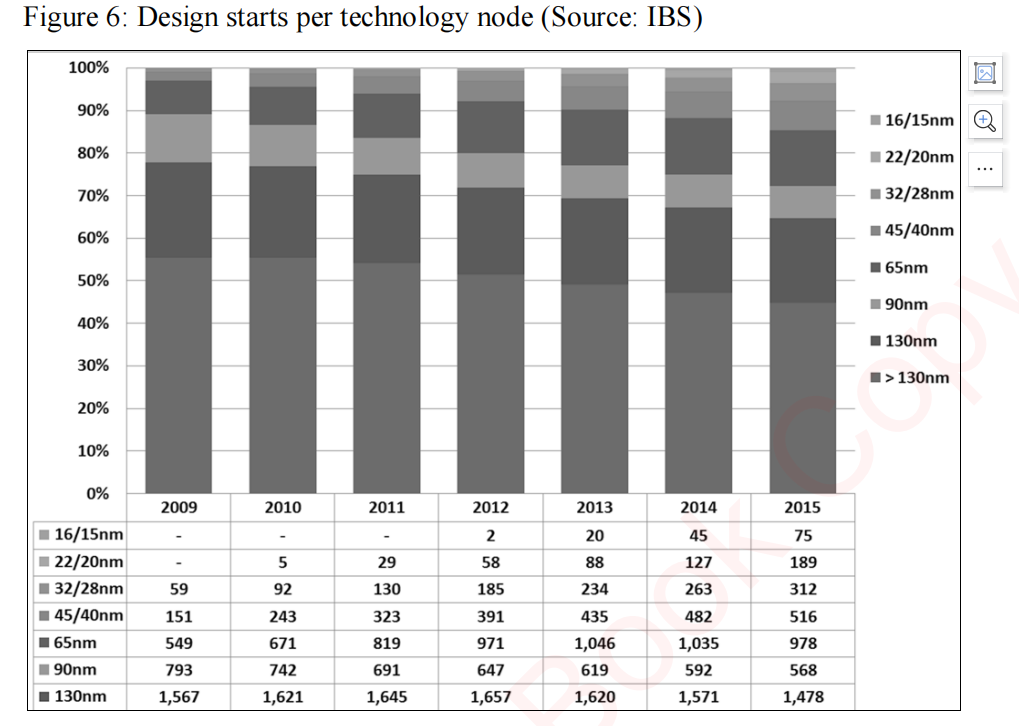

在处理器设计中,晶体管的数量从1979年定义X86的29,000个晶体管增加到2005年定义双核离子的17.2亿个晶体管。这比26年增长了近6万倍。这一趋势一直持续,并且可能在未来继续,从较小的技术节点开始进行的设计数量将会增加,如图6所示。该图表(由加州洛斯加托斯的国际商业战略公司(IBS)的行业分析师提供)显示了每个节点占所有ASIC和SoC设计开始的百分比。

65nm和45nm节点的设计始于2007年,现在已成为主流。因此,需要形成原型的设计的规模稳步增加,对基于软件和硬件的原型都需要越来越多的容量。

基于软件的原型的速度自然受到传统软件串行执行的限制。这进一步增加了提高软件模拟速度的压力,特别是对于处理器模型。

虽然自20世纪90年代末以来,已经使用专有技术建立了快速模拟模型,但标准化现在已经允许将来自各种来源的模型组合成基于系统c的模拟,而不会使用开放的TLM-2.0api实现显著的速度下降。

对于基于硬件的原型,**这一趋势进一步增加了采用更高密度的fpga进行原型设计的压力。**考虑到FPGA原型设计的能力受到可用FPGA能力的限制,唯一的选择是划分和征服,并且只对设计的较小部分作为原型。为了解决这种情况,FPGA原型使用堆叠和扩展的标准接口变得更加可扩展。最后,在要在正在开发的芯片的系统上下文中测试一个原型的情况下,设计的划分可能是困难的。考虑到每个原型板的fpga数量将增加以允许足够的容量,对跨FPGAs自动划分设计的要求也增加了。

1.6.2.整体设计开始减少

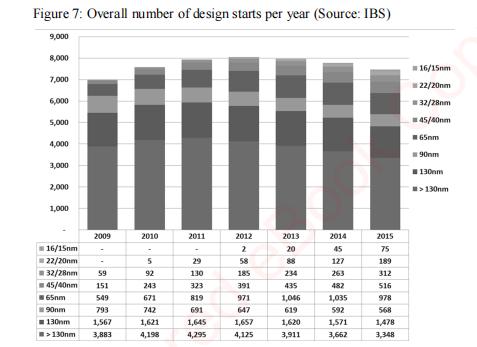

小型化趋势的另一方面是设计开始次数的减少。如图7所示,soc的设计总数就开始了预计将会显著减少。乍一看,现代设计的开发成本是如此之高,以至于更少的公司能够负担得起SoC的开发。

然而,在现实中,最大的下降将是对旧技术的设计开始,即130纳米及以上。设计团队将继续为那些软件内容和对原型设计的需求最大的前沿流程进行设计。

这一趋势的直接结果是,每个设计的风险急剧增加,越来越多的公司已经要求在设计之前对其设计进行原型设计,以验证正确性和避免昂贵的重新旋转。原型设计可以在设计流程的不同点上使用各种不同的技术进行。总的来说,设计开始阶段的减少只会进一步增加每个项目的风险,因此原型设计将变得更加重要。

1.6.3.增加了可编程性和软件功能

绝大多数的电子系统和产品现在都包含了一些可编程性的元素,这在本质上是延迟的功能,它有好几种形式。首先,对ASIC、ASPP和FPGAs设计开始的相对数量的估计表明,大量的设计开始是在FPGAs和其他可编程逻辑设备中;这显然是一个可编程硬件。

其次,包括微处理器在内的FPGA设计的数量也在快速增长。这为可编程硬件增加了软件的可编程性。

此外,相当大比例的ASIC和ASSP设计开始时也包含嵌入式处理器。因此,该软件甚至增加了专用SoC芯片的可编程性。因此,软件的重要性正在显著增加,即使是在SoC项目中也是如此。

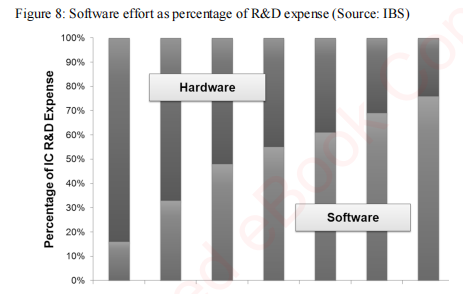

图8说明了预计的软件工作占技术节点的研发费用的百分比。在65纳米处,预期的软件研发费用已经超过了硬件开发。

总的来说,软件已经成为芯片开发的关键路径,其努力正在超过硬件。在传统的串行设计流程中,软件开发开始得很晚,也就是说,当硬件顺利进行时,甚至在最终的原型芯片可用之后。因此,软件的可用性可以阻碍芯片的发展达到主流生产。

从原型化的角度来看,这代表了在项目中尽早开始软件开发的原型化的另一个驱动因素。由于软件在很大程度上决定了一个设计的功能,它注定也会改变验证流程。对原型的软件验证将进一步重要,软件也将成为硬件验证的驱动因素。作为使用VHDL或系统版本编码的测试台的经典验证的替代方法,使用软件的定向测试最近得到了更多的采用。

顺便说一句,如前面所述,这允许在开发的各个阶段中使用一种新的验证重用形式。为了支持这种类型的验证重用,尽早构建硬件原型将成为强制化的。考虑到验证在不同开发阶段的无缝重用,不同原型技术之间的接口也变得更加重要。如今的虚拟原型可以连接到基于硬件的原型上,以允许基于硬件和软件的混合执行,提供了各种优势:

- 首先,避免必须重新建模RTL中已经可用的设计部分,可以减少开发工作,并支持硬件辅助的虚拟平台。

- 其次,硬件原型可以更快地提出,因为测试台——传统上可以包含总体缺陷的50%——已经被验证和稳定,因为它们以前已经应用于虚拟原型。

- 第三,通过混合使用基于硬件和软件的技术,可以更灵活地管理原型的准确性、速度和可用性时间之间的权衡。

- 最后,在系统上下文中验证硬件/软件原型需要与正在开发的芯片环境的接口。来自硬件原型的接口可以接近,甚至在实时执行。使用虚拟原型的接口甚至可以在实际硬件可用性之前就可用。例如,USB 3.0驱动程序已经在虚拟平台上的事务级模型上开发出来,甚至在实际的电缆可用之前。

1.6.4.知识产权块重用

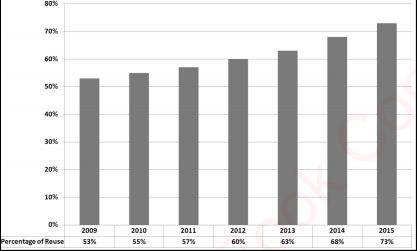

另一个重要的趋势是IP块的重用。随着芯片复杂性的不断增加,IP重用已成为保持设计生产率增长的一种重要途径。图9显示了重用的百分比继续增加,虽然没有在此图中显示,但自2007年以来,块的重用从45%增加到55%,即大多数块现在在其他设计中被重用。

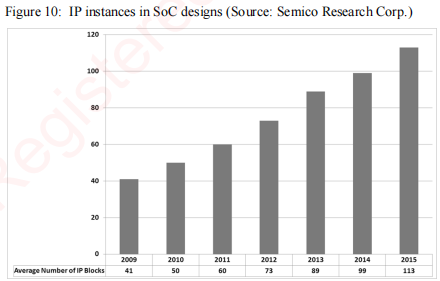

同时,直到每个芯片的平均IP块数量从28个增长到50个,如图10所示。这两个数据点都来自于Semico研究公司的一项研究。考虑到这些IP趋势,芯片设计本身正成为一项通过互连结构组装现有块的任务。芯片的差异化可以通过定制的块、定制的协处理器,当然,还有软件来实现。

增加IP重用对原型化有各种影响。首先,预定义的IP模型在FPGA原型中进行预先映射和预验证,以减少启动时间和减少不必要的工作重复。IP的用户也越来越多在项目的不同阶段和作为IP交付本身的一部分的不同抽象级别上请求模型库。这在处理器领域已经很普遍了,用户要求ARM®、MIPS®、ARC®和扩展®等IP提供商提供可用于早期软件开发和验证的处理器模型

虽然在过去,这些模型的开发是一个挑战,因为它们必须适应各种专有的模拟环境,但这种模型的开发最近在商业上变得可行。

随着OSCI系统c TLM-2.0等标准的出现,处理器、外围设备和互连的模型已经可以在不同的系统c兼容的仿真引擎之间进行互操作。标准化意味着从早期采用者阶段到主流阶段的过渡,因此IP模型的可用性已经大大提高。

1.6.5.应用特异性和混合信号设计

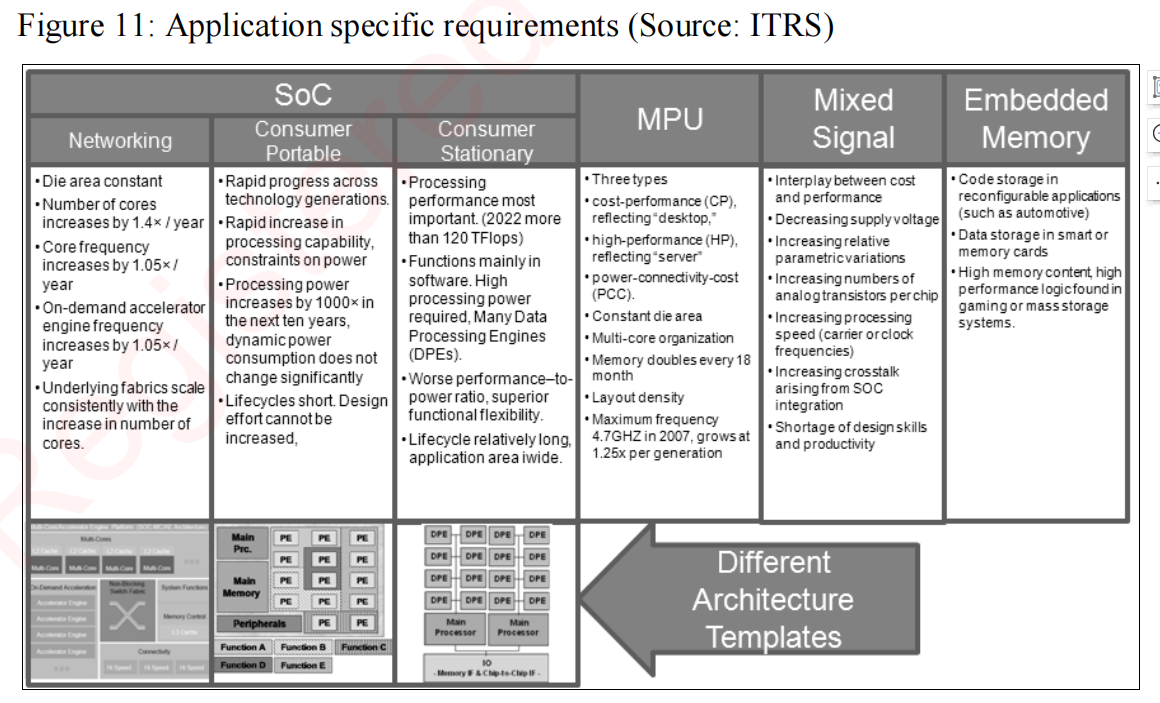

芯片开发的目标应用市场对芯片开发本身有着深远的影响。图11根据国际半导体技术路线图(ITRS),图11总结了不同目标应用的一些定义特征。

ITRS区分了芯片设计的四种主要类别——soc、微处理器单元(MPUs)、混合信号设计和嵌入式内存。每个类别都有特定的要求。在保持模具面积不变的同时提高性能对mpu很重要。降低电源电压是混合信号产生的一个关键问题。

在SoC域内,ITRS将网络应用程序与消费者便携式和消费者固定式分离开来,其各种子需求如

图11所示

总的来说,最终应用对于芯片设计要求和SoCs变得更加重要。因此,不同应用领域的原型需要特定应用程序的分析以及特定应用程序的系统接口,其中大多数具有显著的混合信号内容。除了其他特性外,外部接口的速度还决定了一个原型是可以直接使用还是需要减慢。

1.6.6.多核架构和低功耗

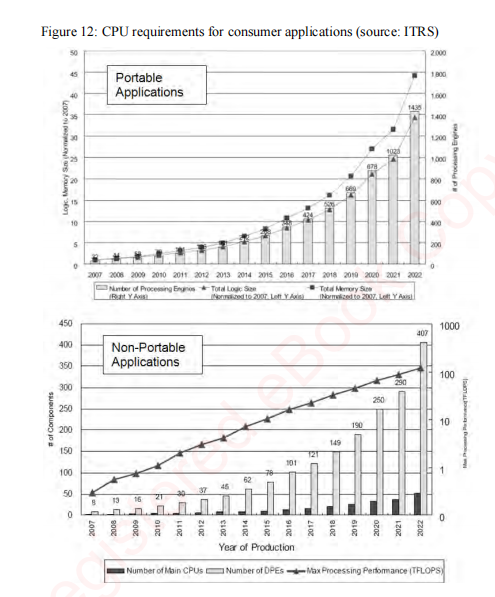

几十年来,处理器速度的扩展满足了软件应用程序对性能日益增长的需求,但行业一直了cpu4 GHz和嵌入式处理器1 GHz的限制。这种限制的原因在于功耗,当缩放到更高的程度时,它只是超过了功率包络。这种真正而困难的限制导致了一种转向多核架构的趋势。简单地说,在更低的频率下,更多的核将比简单地扩展一个核导致更少的功耗。图12中的图表证实了**CPU和数据处理引擎(DPE)**在消费者应用程序中使用的这一趋势。

例如,我们可以看到,从2007年到2011年,dpe的平均数量几乎增加了两倍,而且预计将进一步增加。虽然这在硬件方面是一个很好的解决方案,但现在的挑战已经转移到了软件方面。

传统上,顺序软件现在需要分布在多个核上。对于原型设计来说,这意味着调试(查看硬件/软件执行的能力)以及启动、暂停、恢复和停止硬件/软件执行的能力已经变得更加重要。

今天的虚拟原型已经提供了非干扰性调试设计的智能技术,并且可以在任何给定的时间启动和停止它们。对基于硬件的原型的调试和控制的需求也增加了**,但基于FPGA的原型的调试能力仍然落后于虚拟原型**。

1.7.总结

所有形式的原型都为验证硬件设计和验证软件提供了强大的方法,**模型或多或少地模仿了目标环境。**基于FPGA的原型设计在项目的关键后期阶段尤其有益。用户有几个原型设计选项根据他们的主要需求,可以选择各种基于软件和硬件的技术来原型他们的设计。

由于设计验证和软件开发现在主导着SoC的开发工作,原型设计的使用在减少项目持续时间和设计成本方面从未像现在这样重要过。上面提到的各种IC趋势也使我们只得出一个结论:原型已经成为芯片设计的必要元素,在未来将变得更加重要,我们将在本书的最后一章看到。

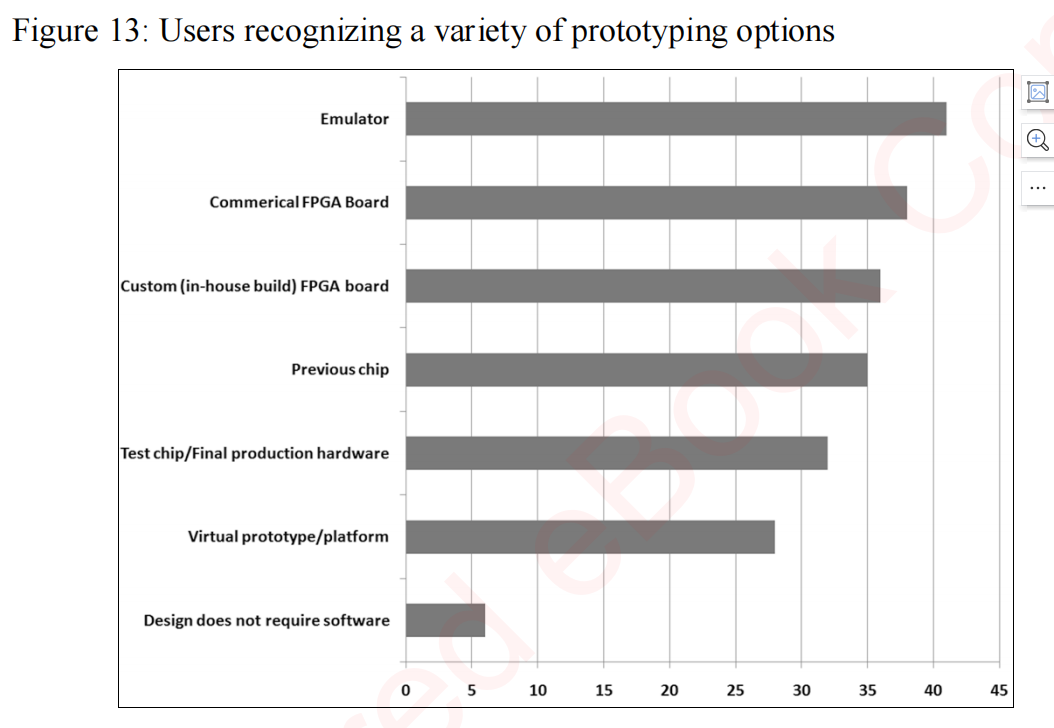

在本章中,我们已经介绍了许多术语和一些完全不同的原型设计类型。它们在现实生活中都有多普遍?为了回答这个问题,我们参考图14,它总结了对2009年8月SoC虚拟会议期间进行的使用调查的116个回复。当被问及“您将使用什么方法来为您的设计项目开发依赖于硬件的软件(例如,驱动程序、固件)时?”,**研究结果显示,用户确实能识别出各种不同的原型设计解决方案。**结果表明,前面描述的所有原型技术都在积极使用中——这是上面讨论的不同优先级的明显结果——有利于不同的原型选项。在下一章中,我们将放大基于FPGA的原型设计的好处,特别是对软件团队和整个SoC项目的好处。

这一章是统揽,下面就单独开始聚焦于FPGA原型验证!!!