目录

一、理论基础

整个程序分为以下三大部分:

·时钟控制部分,分为调整分,秒功能,秒清零功能;

·暂停功能,时钟计数停止功能;

·4位数码管显示功能;

系统按键为,分快速调整按钮,复位,秒清零按钮,系统暂停按钮(工作和暂停两个功能供用)

所以需要四个按钮。

二、案例背景

1.问题描述

整个系统的基本框图如下所示:

2.思路流程

·按键消抖主要是通过延迟的功能来实现的,在实际下板子的时候往往需要延迟很长一段时间,所以我们的代码为您提供两个版本的代码,一个版本为仿真版本,不加消抖,一个版本为硬件版本,具有消抖功能。

·仿真版本主要考虑系统的功能,所以我们直接对时钟进行系统控制;而硬件版本,我们为了得到1秒对应的时钟,需要对系统时钟进行分频。

三、verilog核心仿真

top程序如下:

module time_module(

i_clk, //系统时钟

//这里假设按键的初始状态为0,按下后为1

i_rst, //系统复位

i_min_fast,//调整分

i_sec_fast,//调整秒

i_stop_run,//暂停或者继续工作

o_min, //显示分

o_sec //显示秒

);

input i_clk;

input i_rst;

input i_min_fast;

input i_sec_fast;

input i_stop_run;

output[7:0]o_min;

output[7:0]o_sec;

reg[7:0]o_min = 8'd0;

reg[7:0]o_sec = 8'd0;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_min <= 8'd0;//59

o_sec <= 8'd0;//59

end

else begin

if(i_stop_run == 0)//不按下时为0,时钟正常工作

begin

//正常计时间

if(o_sec[3:0] == 4'd9)

begin

o_sec[3:0] <= 4'd0;

if(o_sec[7:4] == 4'd5)

begin

o_sec[7:4] <= 4'd0;

//分计数

if(o_min[3:0] == 4'd9)

begin

o_min[3:0] <= 4'd0;

if(o_min[7:4] == 4'd5)

begin

o_min[7:4] <= 4'd0;

end

else begin

o_min[7:4] <= o_min[7:4] + 4'd1;

end

end

else begin

o_min[3:0] <= o_min[3:0] + 4'd1;

end

end

else begin

o_sec[7:4] <= o_sec[7:4] + 4'd1;

end

end

else begin

o_sec[3:0] <= o_sec[3:0] + 4'd1;

end

//调整时间

if(i_min_fast == 1'b1)

begin

if(o_min[3:0] == 4'd9)

begin

o_min[3:0] <= 4'd0;

if(o_min[7:4] == 4'd5)

begin

o_min[7:4] <= 4'd0;

end

else begin

o_min[7:4] <= o_min[7:4] + 4'd1;

end

end

else begin

o_min[3:0] <= o_min[3:0] + 4'd1;

end

end

if(i_sec_fast == 1'b1)

begin

o_sec <= 8'd0;

end

end

else begin//按下时为1,时钟停止

o_min <= o_min;

o_sec <= o_sec;

end

end

end

endmodule

四、仿真结论分析

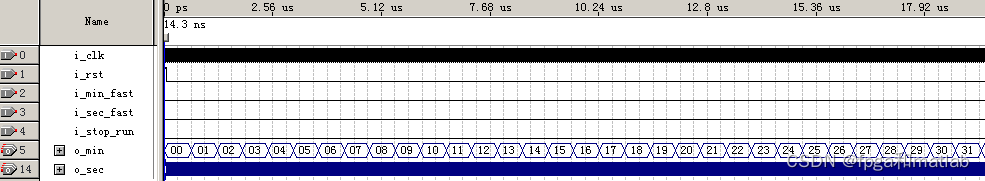

仿真结果如下所示:

正常运行:

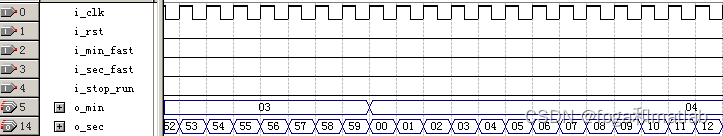

如上图可以看到,当秒计数到59的事后哦,变0,然后分的数字加1;

调整:

分调整:

分调整按钮按下,分马上开始快速计数,和现实中的电子表一个原理。

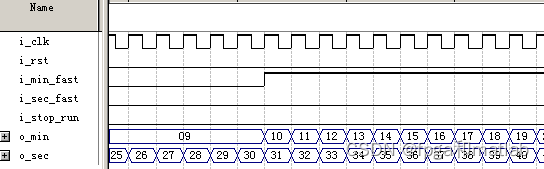

秒调整:

秒调整按钮按下,秒变0。

暂停:

当按下暂停的时候,停止走动。

复位:

通过复位后,系统变为0;A02-36