Verilog快速入门已经全部刷完,详见主页FPGA刷题(1)~(5)

今天开始干Verilog进阶挑战,序列检测部分有4道题:

目录

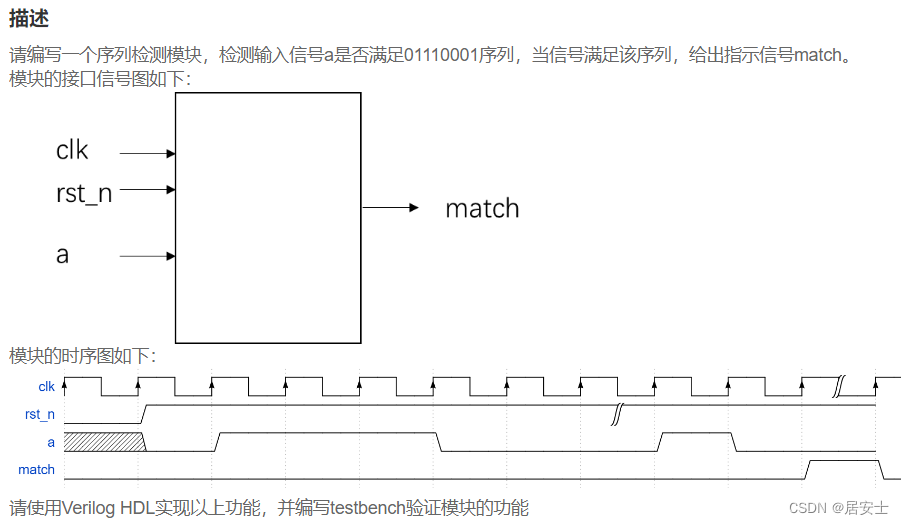

输入序列连续的序列检测

对于序列检测题目,常规的解法有两种:状态机法和序列缓存对比法。

状态机法的过程类似于题意理解中提到的过程:在初始状态中,先判断第一位是否符合,若符合则进入下一个状态,判断第二位是否符合;若第一位不符合则保持在初始状态,直到第一位匹配。如前两位匹配,则判断第三位是否符合,若第一位匹配,最新输入的数值和目标序列的第二位不匹配,则根据最新一位是否匹配第一位,进入第一位匹配状态或者初始状态。依次类推。

序列缓存对比法,则是将八个时刻的数据缓存,作为一个数组,每个时刻的输入位于数组的末尾,数组其它元素左移,把最早输入的数据移出。然后将数组和目标序列对比,如果数组和目标序列相等,则说明出现目标序列。

序列缓存对比法在实现上比较简单,本题采用该方法实现。首先声明一个数组,缓存八个时刻的a输入的数值。移位可以通过位截取操作和位拼接操作实现:a_tem[6:0]表示截取a_tem的低7位,{a_tem[6:0],a}表示把a_tem[6:0]和新输入的数值a拼接,a位于低位。

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg[7:0]a_reg;

always@(posedge clk or negedge rst_n)begin

if(~rst_n)begin

a_reg<=8'd0;

end

else begin

a_reg<={a_reg[6:0],a};

end

end

always@(posedge clk or negedge rst_n)begin

if(a_reg==8'b01110001)begin

match<=1'd1;

end

else begin

match<=1'd0;

end

end

endmodule含有无关项的序列检测

题目要求检测a的序列,a为单bit输入,每个时刻可能具有不同的值,题目要求检测前三位和后三位,不要求检测中间三位,如果把如果把中间的XXX,分别列出:000,001,010,011,100,101,110,111,分别检测,代码过于累赘,考虑分别检测前三位和后三位,分成两个小段的序列检测。当前三位信号和后三位信号同时匹配时,把匹配信号match拉高。

将九个时刻的数据缓存,作为一个数组,每个时刻的输入位于数组的末尾,数组其它元素左移,把最早输入的数据移出。然后截取数组的前三位和目标序列011对比,截取数组的后三位和目标序列110对比,如果两段数组都和目标序列相等,则说明出现目标序列。

module sequence_detect(

input clk,

input rst_n,

input a,

output match

);

reg [8:0] a_reg;

reg match_1;

reg match_0;

always@(posedge clk or negedge rst_n)begin

if(~rst_n)begin

a_reg<=9'd0;

end

else begin

a_reg<={a_reg[7:0],a};

end

end

always@(posedge clk or negedge rst_n)begin

if(~rst_n)begin

match_1<=1'd0;

end

else if(a_reg[8:6]==3'b011)begin

match_1<=1'd1;

end

else begin

match_1<=1'd0;

end

end

always@(posedge clk or negedge rst_n)begin

if(~rst_n)begin

match_0<=1'd0;

end

else if(a_reg[2:0]==3'b110)begin

match_0<=1'd1;

end

else begin

match_0<=1'd0;

end

end

assign match = (match_1) && (match_0);

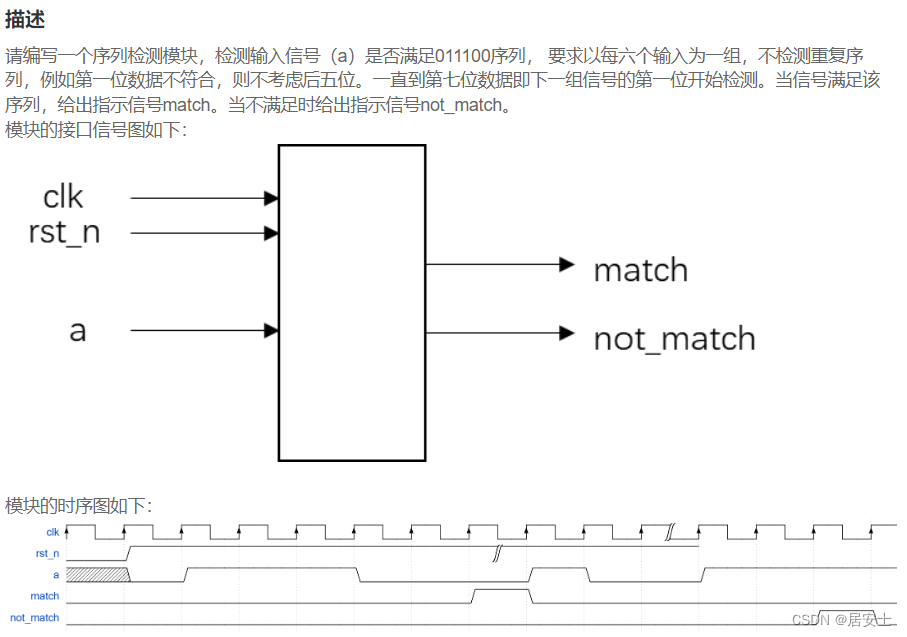

endmodule不重叠序列检测

题目要求检测a的序列,a为单bit输入,每个时刻可能具有不同的值, 当连续的六个输入值符合目标序列表示序列匹配,当六个输入值的一个或多个不符合则表示序列不匹配。

值得注意的是:题目要求以六位数据为一组,不同于常见的序列检测,要求检测重复序列,在画状态转移图时要注意,例如第一位不匹配,不应该返回到初始状态去进行第一位的判断,因为此时的输入是第二位数值,题目要求不对该数值做判断,而需要等到六个时钟周期之后,即第七位数据(第二组数值的第一位)再判断是否匹配目标序列的第一位。

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

parameter ZERO=0, ONE=1, TWO=2, THREE=3, FOUR=4, FIVE=5, SIX=6, FAIL=7;

reg [2:0] state, nstate;

reg [2:0] cnt;

always@(posedge clk or negedge rst_n) begin

if(~rst_n)

cnt <= 0;

else

cnt <= cnt==6? 1: cnt+1;

end

always@(posedge clk or negedge rst_n) begin

if(~rst_n)

state <= ZERO;

else

state <= nstate;

end

always@(*) begin

if(~rst_n)

nstate = ZERO;

else

case(state)

ZERO : nstate = data? FAIL : ONE;

ONE : nstate = data? TWO : FAIL;

TWO : nstate = data? THREE: FAIL;

THREE: nstate = data? FOUR : FAIL;

FOUR : nstate = data? FAIL : FIVE;

FIVE : nstate = data? FAIL : SIX;

SIX : nstate = data? FAIL : ONE;

FAIL : nstate = cnt==6&&data==0? ONE: FAIL;

default: nstate = ZERO;

endcase

end

always@(*) begin

if(~rst_n) begin

match = 0;

not_match = 0;

end

else begin

match = cnt==6&&state==SIX;

not_match = cnt==6&&state==FAIL;

end

end

endmodule

输入序列连续的序列检测

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

reg [3:0] pstate,nstate;

parameter idle=4'd0,

s1_d0=4'd1,

s2_d01=4'd2,

s3_d011=4'd3,

s4_d0110=4'd4;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

pstate<=idle;

else

pstate<=nstate;

end

always @(pstate or data or data_valid)

begin

case(pstate)

idle:

if(data_valid && !data)

nstate=s1_d0; //第一位匹配

else

nstate=idle;

s1_d0:

if (data_valid)

begin

if (data) nstate = s2_d01; //数据有效且为1,即前两位01匹配,下一状态为s2_d01

else nstate = s1_d0; //数据有效但为0,即只有第一位0匹配,下一状态为s1_d0

end

else nstate = s1_d0; //数据无效,保持在s1_d0

s2_d01:

if (data_valid)

begin

if (data) nstate = s3_d011; //数据有效且为1,即前三位011匹配,下一状态为s3_d011

else nstate = s1_d0; //数据有效但为0,即只有第一位0匹配,下一状态为s1_d0

end

else nstate = s2_d01; //数据无效,保持在s2_d01

s3_d011:

if (data_valid)

begin

if (!data) nstate = s4_d0110; //数据有效且为0,即前四位0110匹配,下一状态为s4_d0110

else nstate = idle; //数据有效但为1,即不匹配,下一状态为idle

end

else nstate = s3_d011; //数据无效,保持在s3_d011

s4_d0110:

if (data_valid)

begin

if (!data) nstate = s1_d0; //数据有效且为0,即匹配目标序列的第一位0,下一状态为s1_d0

else nstate = idle; //数据有效但为1,不匹配目标序列,下一状态为idle

end

else nstate = idle; //数据无效,下一状态为idle

default:

nstate=idle;

endcase

end

always @(pstate or rst_n)

begin

if(!rst_n==1)

match=1'b0;

else if(pstate==s4_d0110) //进入状态s4_d0110表示四位数据都匹配,把匹配指示信号match拉高

match=1'b1;

else

match=1'b0;

end

endmodule