小芯片chiplet技术杂谈

中央处理器(central processing unit,简称CPU)作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。CPU自产生以来,在逻辑结构、运行效率以及功能外延上取得了巨大发展。

CPU出现于大规模集成电路时代,处理器架构设计的迭代更新以及集成电路工艺的不断提升促使其不断发展完善。从最初专用于数学计算到广泛应用于通用计算,从4位到8位、16位、32位处理器,最后到64位处理器,从各厂商互不兼容到不同指令集架构规范的出现,CPU 自诞生以来一直在飞速发展。

中央处理器(CPU),是电子计算机的主要设备之一,电脑中的核心配件。其功能主要是解释计算机指令以及处理计算机软件中的数据。CPU是计算机中负责读取指令,对指令译码并执行指令的核心部件。中央处理器主要包括两个部分,即控制器、运算器,其中还包括高速缓冲存储器及实现它们之间联系的数据、控制的总线。电子计算机三大核心部件就是CPU、内部存储器、输入/输出设备。中央处理器的功效主要为处理指令、执行操作、控制时间、处理数据。

参考文献链接

https://mp.weixin.qq.com/s/VHZcebt_Yi_ROjJG5FCkgg

AMD:先进分装,步入Chiplet时代

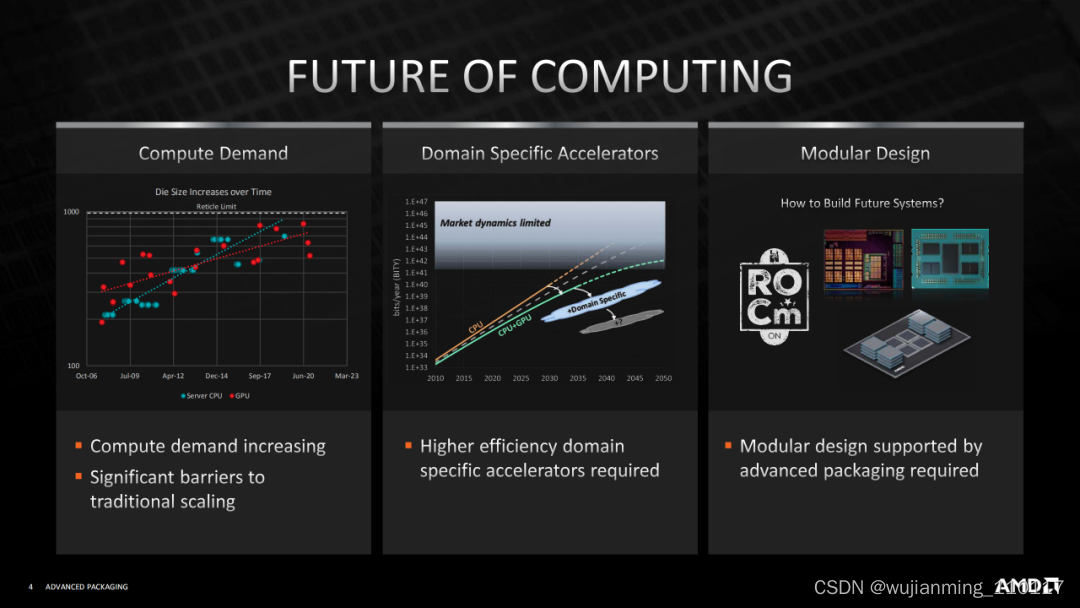

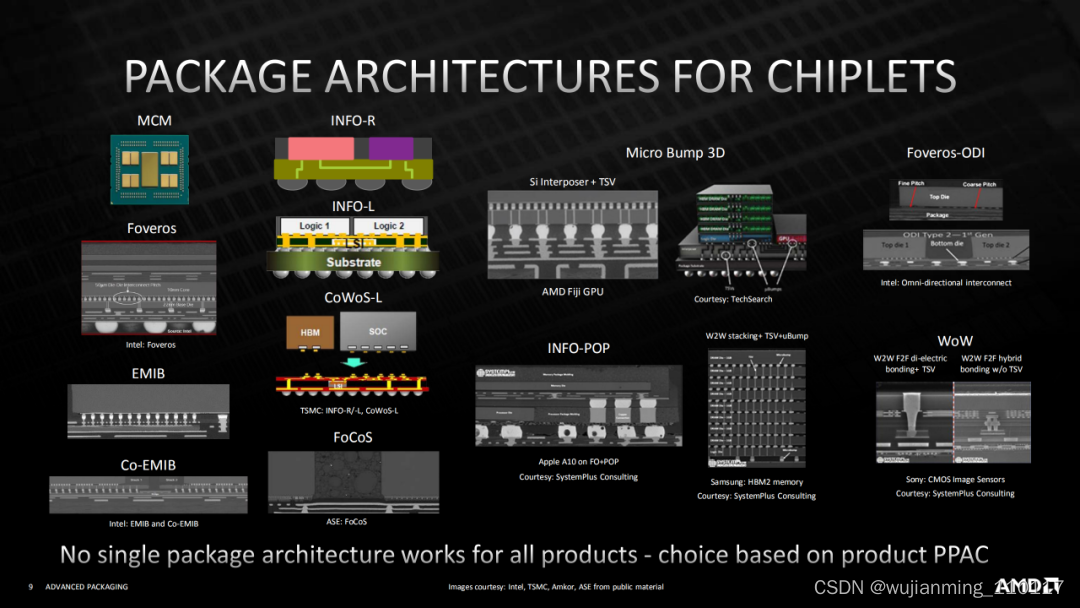

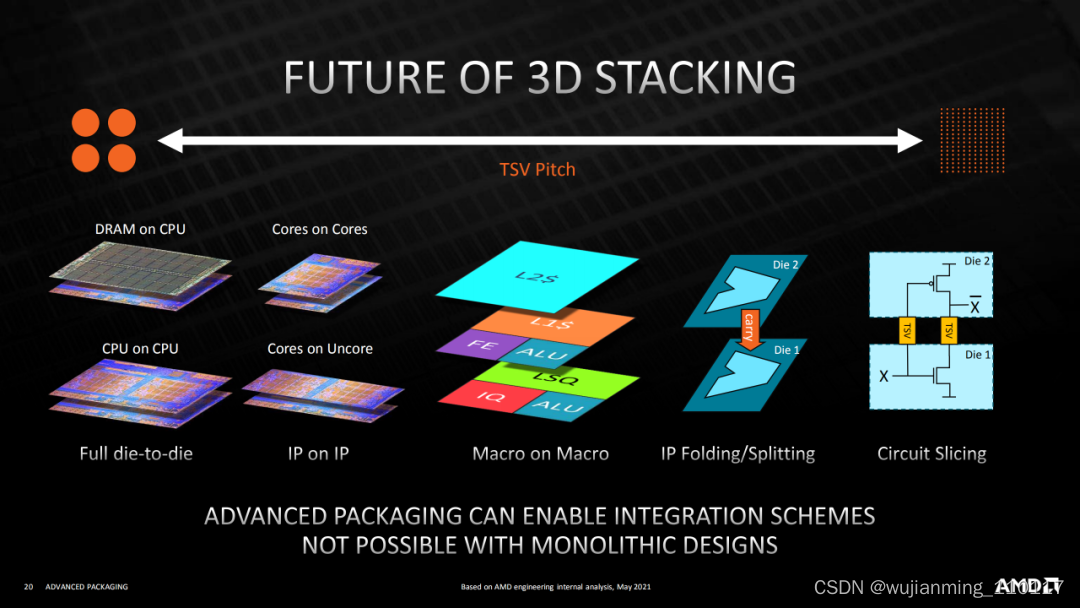

封装行业正在努力将小芯片(chiplet)的采用范围扩大到几个芯片供应商之外,也为下一代 3D 芯片设计和封装奠定基础。

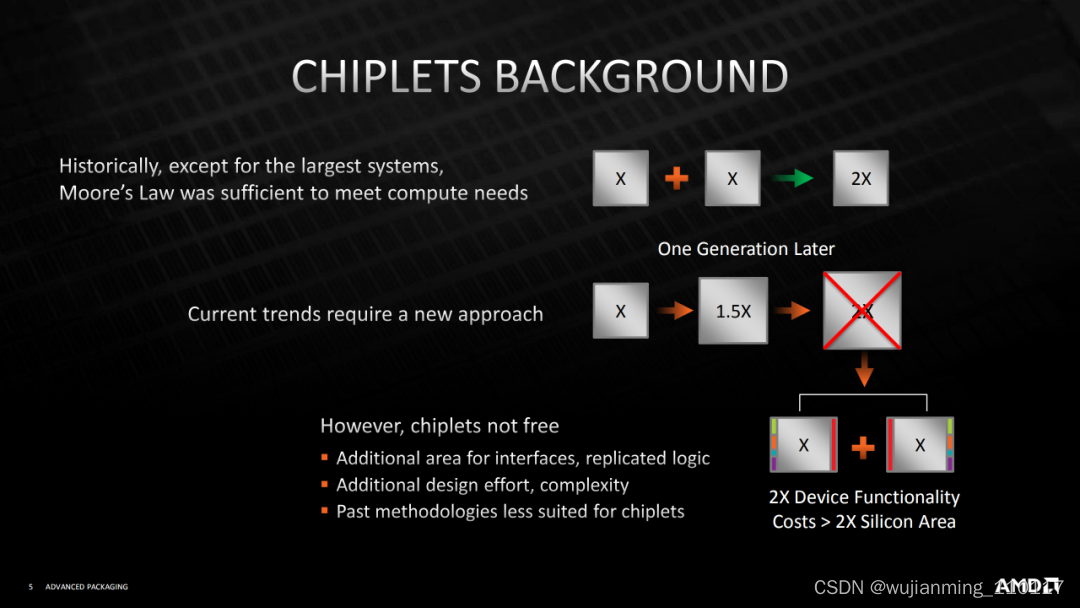

新的小芯片标准和用于确定给定基于小芯片的设计可行性的成本分析工具是两个新的重要部分。与其他努力一起,他们目标是推动小芯片模型向前发展,尽管该技术仍存在挑战和差距。

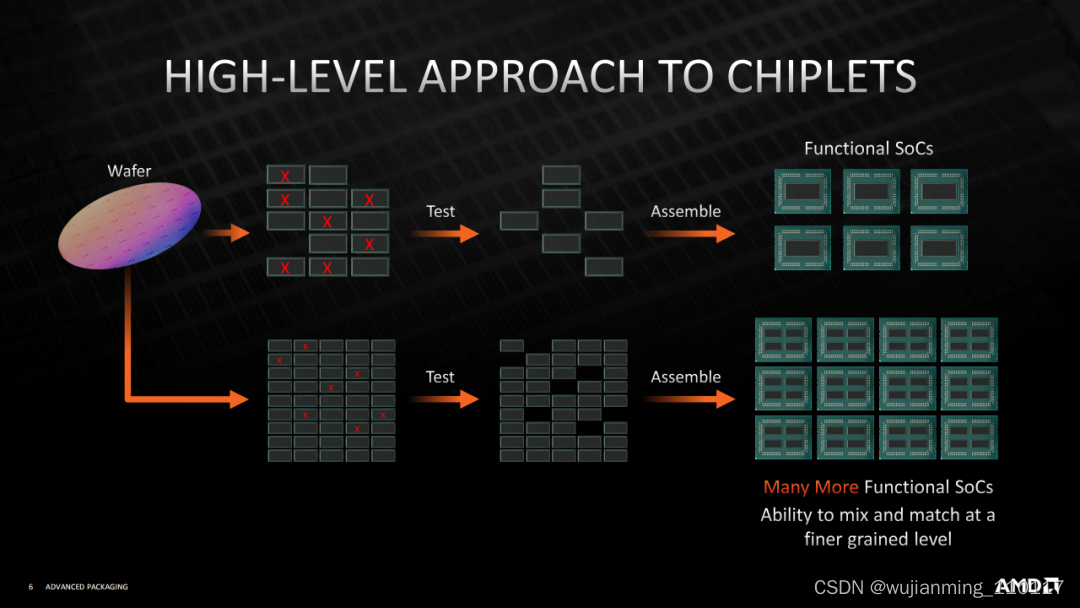

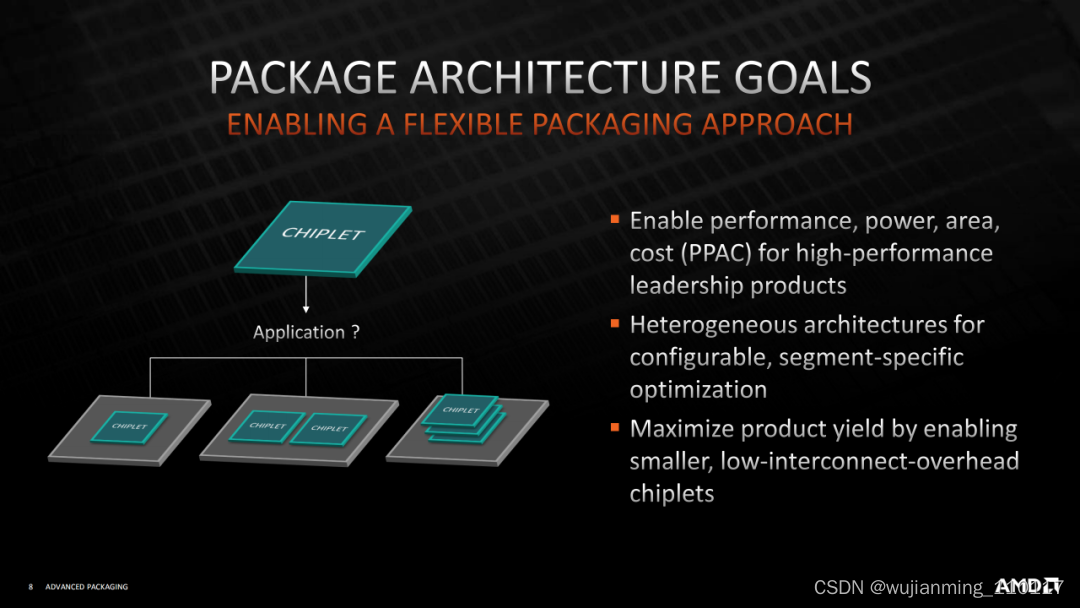

使用这种方法,封装公司可以在库中拥有具有不同功能和工艺节点的模块化芯片或小芯片“菜单”。然后,芯片客户可以选择这些小芯片中的任何一个,并将它们组装在一个先进的封装中,从而产生一种新的、复杂的芯片设计,作为片上系统 (SoC) 的替代品。

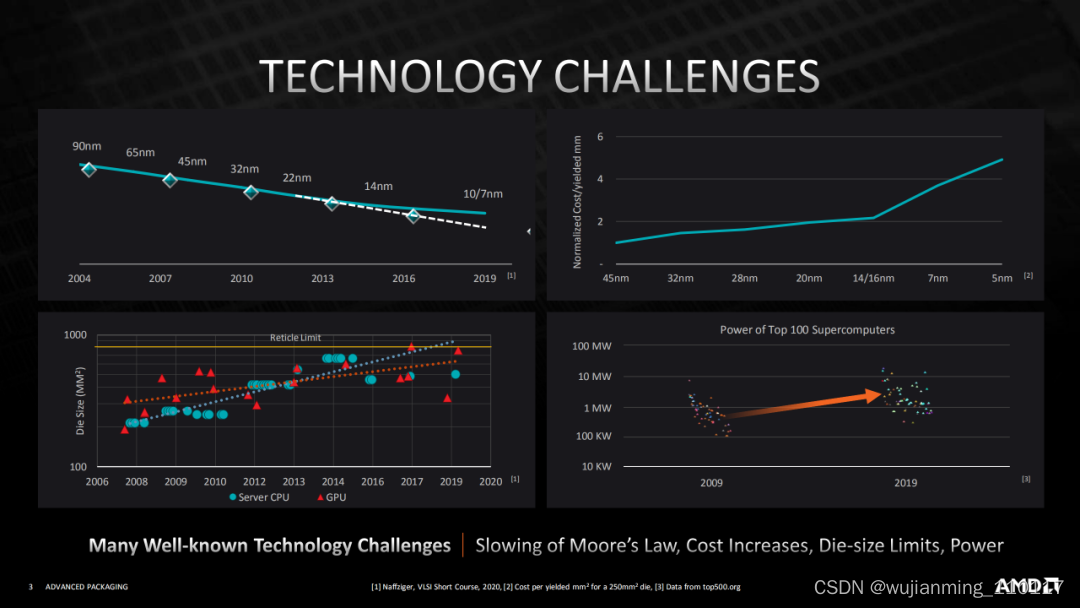

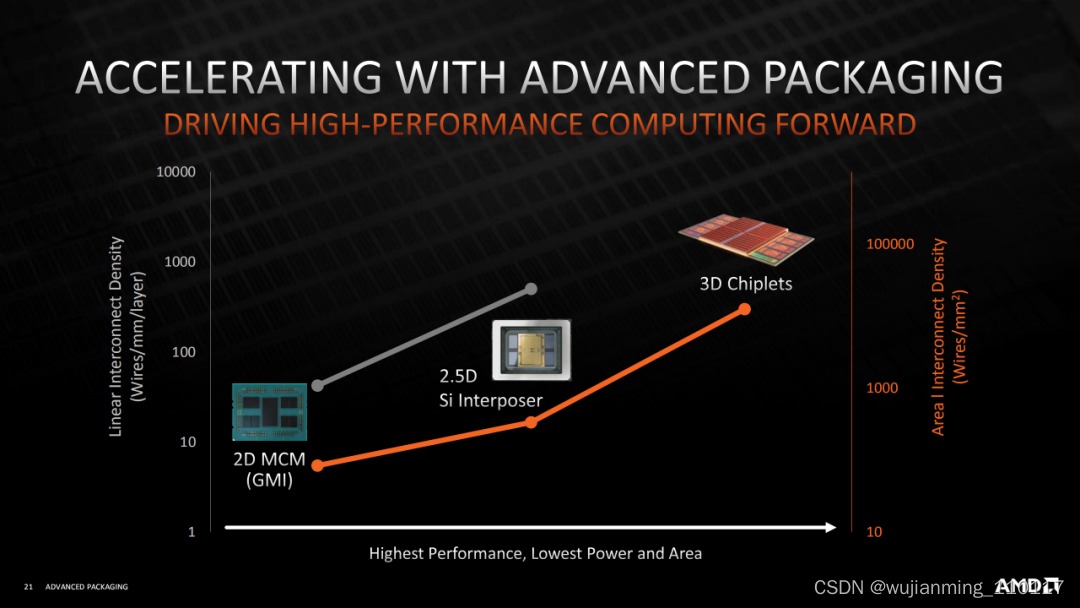

小芯片模型已被英特尔、AMD 和 Marvell 等公司证明有效,这些公司设计自己的小芯片和互连。现在,该行业的其他公司正在探索小芯片,主要是因为扩展对许多人来说变得过于困难和昂贵,而且迁移到新节点的功率和性能优势正在缩小。高级封装提供了一种在不同技术节点上组合芯片的经济高效的方式,而小芯片则提供了增加互连 RC 延迟的解决方案。它们还承诺更快地开发复杂芯片,并且可以针对特定市场和应用进行定制。

传统上,为了开发复杂的 IC 产品,供应商设计了一种将所有功能集成在同一芯片上的芯片。在随后的每一代中,每个芯片的功能数量都急剧增加。在最新的 7nm 和 5nm 节点上,成本和复杂性飙升。(节点是指特定的过程及其设计规则。)

“设计新硅节点的成本正在上升,”谷歌高级技术开发工程师 Mudasir Ahmad 在最近的一次演讲中说。“只是为了给你一个规模,现在做 5nm 芯片的成本与做 10nm 和 7nm 芯片的成本加起来差不多或差不多。它非常昂贵。”

虽然传统方法仍然是新设计的一种选择,但小芯片为客户提供了另一种解决方案。但与任何新技术一样,chiplet 集成并不简单。目前,基于小芯片的设计专门用于高端产品,而不是日常设计。即便如此,构建基于小芯片的模型也需要几个部分。只有少数大公司拥有所需的内部专业知识和能力,其中大部分是专有的。

这将基于小芯片的方法的采用限制在少数人身上。但现在,行业正在努力使基于小芯片的设计更易于访问。这些努力包括:

• ASE、AMD、Arm、谷歌、英特尔、Meta、微软、高通、三星和台积电组成了一个新的小芯片联盟。该小组发布了一种新的开放式裸片到裸片互连规范,使小芯片能够在封装中相互通信。

• 开放域特定架构 (ODSA) 子项目正在对类似技术进行最后的润色。ODSA 还刚刚发布了一个新的成本分析工具,它有助于确定给定的基于小芯片的设计是否可行。

• 几家封装公司正在开发制造技术,以将基于小芯片的设计投入生产。

小芯片具有挑战性;通常,要开发基于小芯片的设计,第一步是定义产品。然后,提出的基于小芯片的设计需要几个部分,例如产品架构、已知良好的芯片 (KGD) 和芯片到芯片的互连。它还需要完善的制造策略。

KGD 是设计中使用的裸片或小芯片。芯片到芯片互连允许小芯片在设计中相互通信。通过开发或采购这些部件,芯片客户可以开发基于小芯片的设计,至少在纸面上是这样。

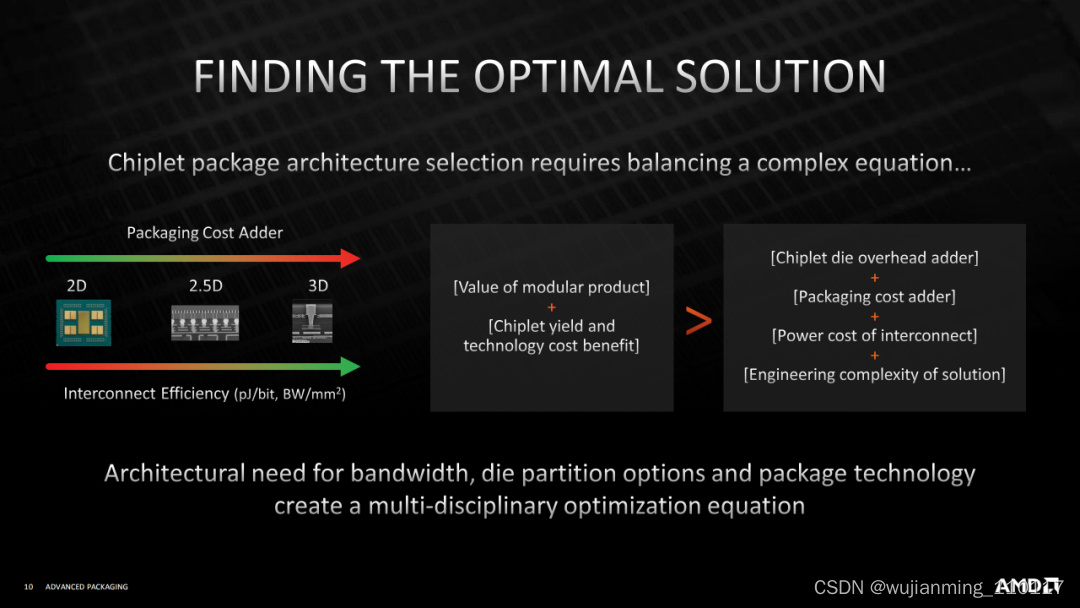

但最大的问题是该设计是否可行或具有成本效益。这可能是一个主要的绊脚石,阻止了对风险不利的芯片客户考虑小芯片。

为了帮助这里的客户,ODSA 发布了一个成本分析软件工具,其中包括开发基于小芯片的设计所涉及的所有可能组件和成本的电子表格。

“没有通用规则说你应该总是做小芯片,或者你不应该做。这一切都取决于特定的应用程序,”谷歌的Mudasir Ahmad说。“我们需要一个可用于每个应用程序的模型来提供反馈。[使用电子表格,芯片客户](With the spreadsheet, chip customer)可以使用通用框架将数据输入其中。然后他们可以尝试了解为特定应用程序制作小芯片是否有意义。”

成本不是唯一的因素。工程师还必须考虑小芯片的挑战。根据Ahmad的说法,以下是其中一些挑战:

• 报废成本:如果一个小芯片在一个或多个最终设计中失败,则设备可能会报废。这增加了废品成本。

• 测试:为了最大限度地减少废品损失,设计需要更多的测试覆盖率。

• 良率:封装复杂性可能会影响整体良率。

• 性能:将信号从一个芯片移动到另一个芯片可能会降低产品的性能。

商业模式是另一个挑战。如果您有不同的供应商提供不同的零件,并且您将它们全部放在一个封装中,那么谁负责什么?谁承担失败的责任?

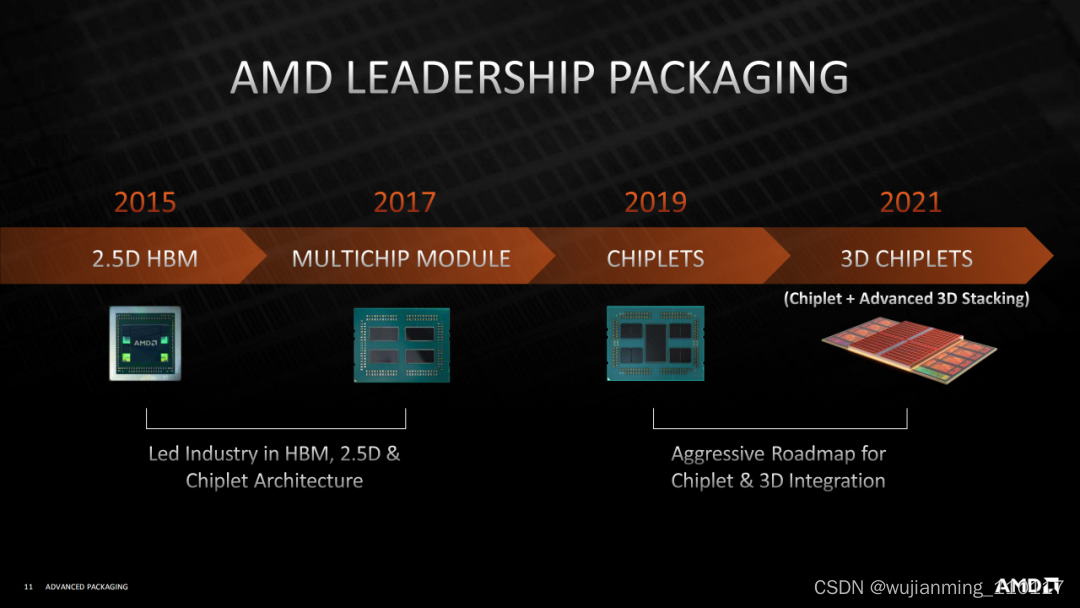

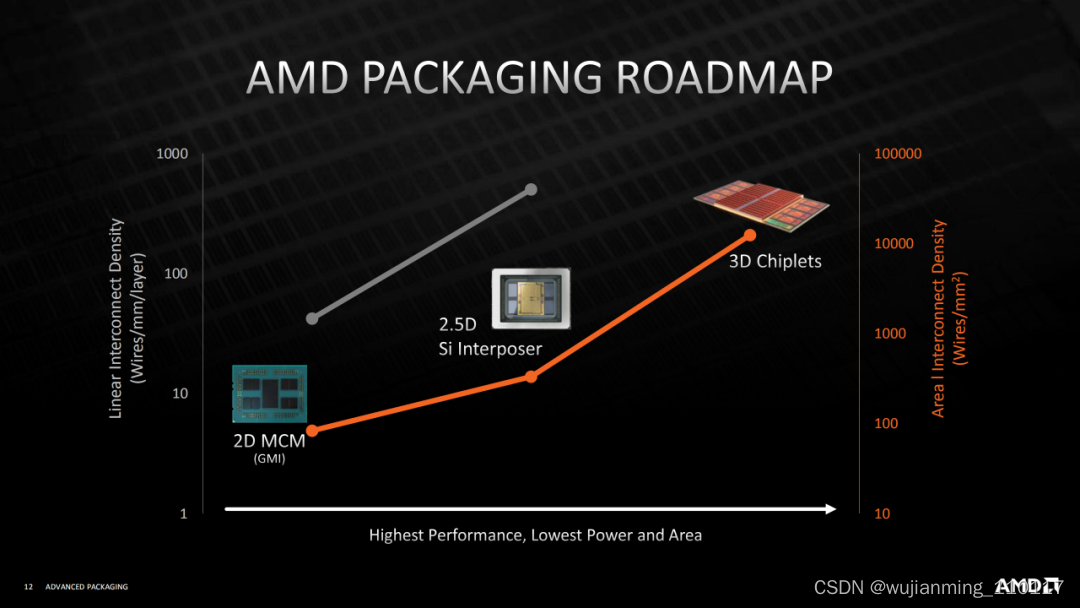

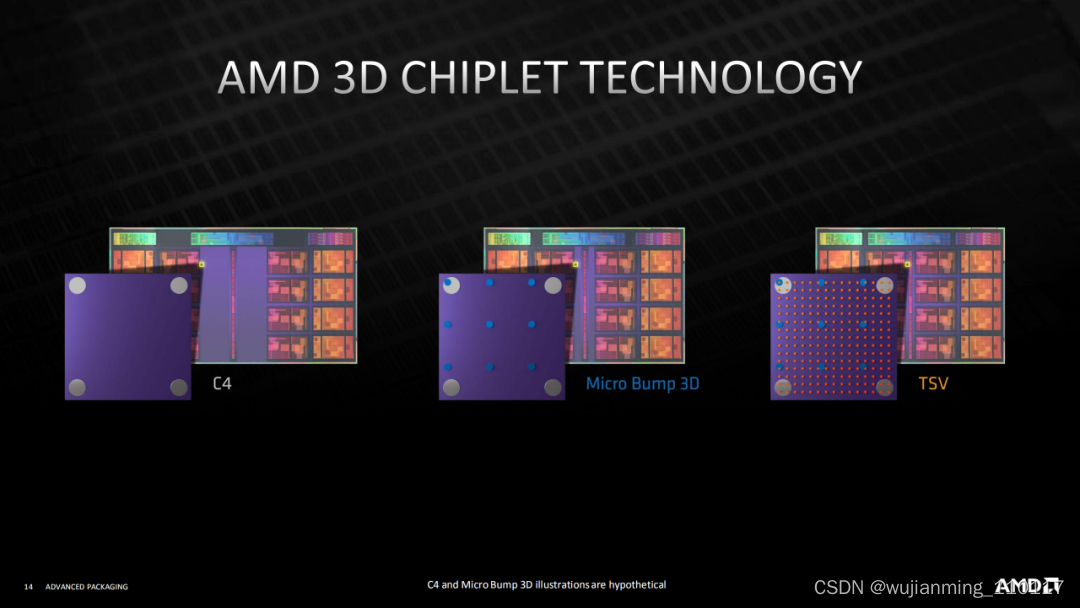

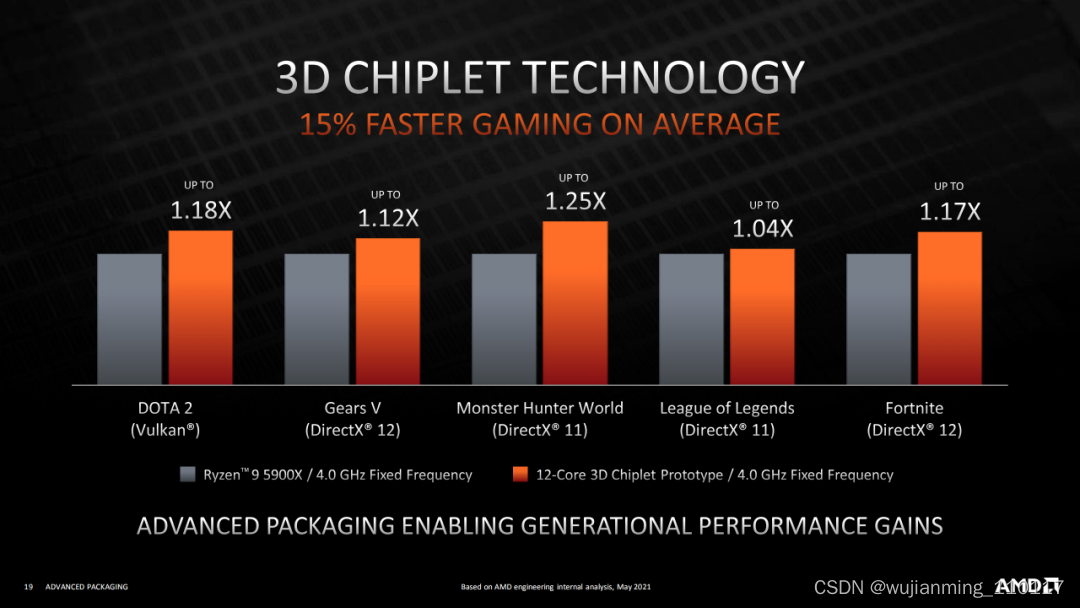

以下内容来自“2021 Hot Chips AMD Advanced Packaging”,下载链接:2021 Hot Chips全球芯片厂商技术合集(1)和2021 Hot Chips全球芯片厂商技术合集(2)。

参考文献链接

https://mp.weixin.qq.com/s/VHZcebt_Yi_ROjJG5FCkgg