目录

实验目的:

学习数控分频器的设计、分析和测试方法,练习计数器的设计应用。

实验预习:

熟悉计数器的设计;了解如何用计数器实现分频器的设计。

实验讲解:分频器的设计

思考两个问题:

Q:什么是分频器,什么是分频系数?

A:能将频率高的信号clk转变为频率低的信号clk_1的电路叫分频器,如果clk_1信号的周期为clk周期的n倍,则n为分频系数)

Q:分频器设计的核心思想是什么?

A:计数器的设计)

偶分频器的设计(以6分频器为例)

module dvf6(clk,clk_1);

input clk;

output reg clk_1;

reg[2:0] q;

always@(posedge clk)

begin

if(q==3'b101) q<=3'b000;

else q<=q+1;

end

always@(q)

begin

if(q>=3b'011) clk_1<=1'b1;

else clk_1<=1'b0;

end

endmodule

另一种设计方案

module dvf6(clk,clk_1);

input clk;

output reg clk_1;

reg[2:0] q;b

always@(posedge clk)

begin

if(q==3'b010) begin q<=q+3'b001; clk_1<=~clk_1;end

else if (q==3'b101) begin q<=3'b000; clk_1<=~clk_1;end

else q<=q+3'b001;

end

endmodule奇分频器的设计(以9分频器为例)

module dvf9(clk,clk_1);

input clk;

output clk_1;

reg[3:0] q1,q2;

reg clk_p,clk_n;

always@(posedge clk)

begin

if(q1==4'b100) begin q1<q1+4'b0001;clk_p<=~clk_p;end

else if(q1==4'b1000) begin q1<=4'b0000;clk_p<=~clk_p;end

else q1<=q1+4'b0001;

end

alway@(negedge clk)

begin

if(q2==4'b0100) begin q2<=q2+4'b0001;clk_n<=~clk_n;end

else if (q2==4'b1000) begin q2<=4'b0000;clk_n<=~clk_n;end

else q2<=q2+4b'0001;

end

always@(negedge clk)

begin

if(q2==4b'0100) begin q2<=q2+4'b0001;clk_n=~clk_n;end

else if(q2==4'b1000) begin q2<=4'b0000;clk_n<=~clk_n;end

else q2<=q2+4'b0001;

end

assign clk_1=clk_p|clk_n;

endmodule30分频器设计

module dvf_30(clk,clk_1);

input clk;

output reg clk_1;

reg[4:0] q;

always@(posedge clk)

begin

if(q==5'b11101) q<=5'b00000;

else q<=q+1;

end

always@(q)

begin

if(q>=4'b1111) clk_1<=1'b1;

else clk_1<=1'b0;

end

endmodule

实验内容:数控分频器的设计

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可。

源代码

module dvf_suk(clk,D,fout,full_1);

input clk;

input [7:0] D;

output reg fout;

reg[7:0] reg8;

reg full;

output full_1;

always@(posedge clk)

begin

if(reg8==8'hff) begin reg8<=D;full<=1'b1; end

else begin reg8<=reg8+8'b1;full<=1'b0; end

end

always@(posedge full)

begin

fout<=~fout;

end

assign full_1=full;

endmodule

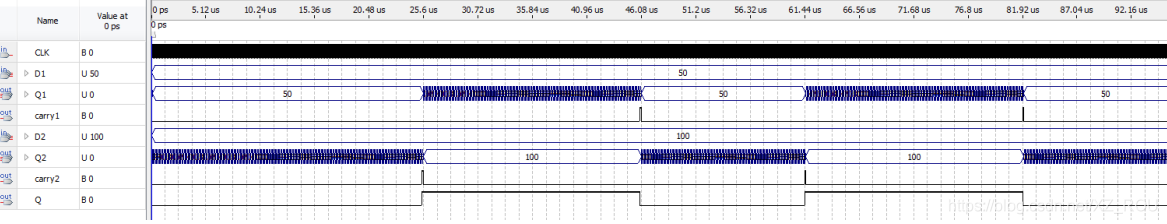

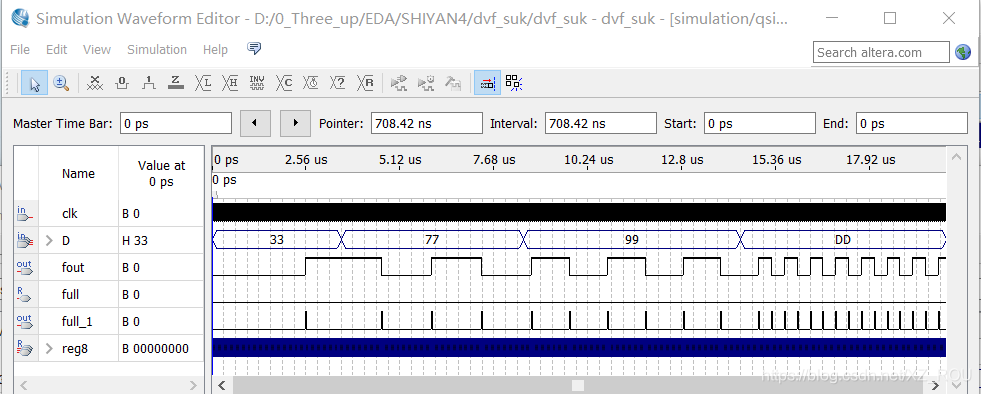

仿真波形

硬件验证

设计数控分频器的功能时,可选实验电路模式1,其中键2/键1负责输入8位预置数D(PIO7~PIO0);CLK由clockB0输入,频率选65536Hz或更高(确保分频后落在音频范围);输出接入蜂鸣器信号输入端。改变键2/键1的输入值,可听到不同音调的声音。

课后作业

利用两个数控分频器模块设计一个电路,使其输出方波的正负脉宽的宽度分别由两个8位输入数据控制。