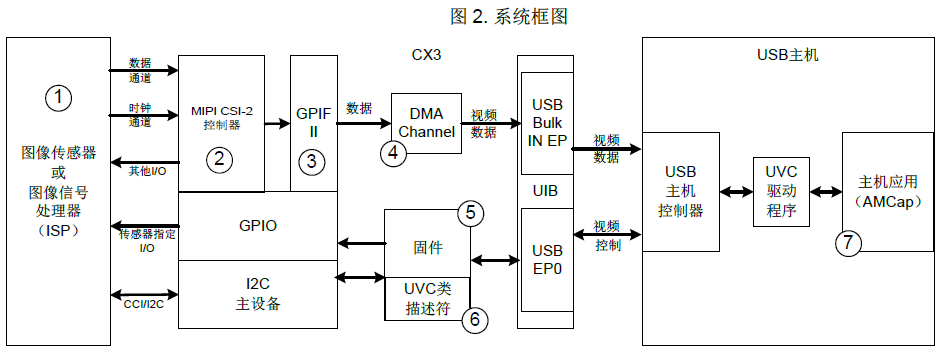

Cypress CX3的sdk提供了配置工具,用于生成CX3项目。使用该工具可以根据用户输入生成完整的CX3固件项目(包含UVC/供货商类别描述符、处理UVC请求、视频串流DMA引擎以及MIPI CSI-2控制器配置)。

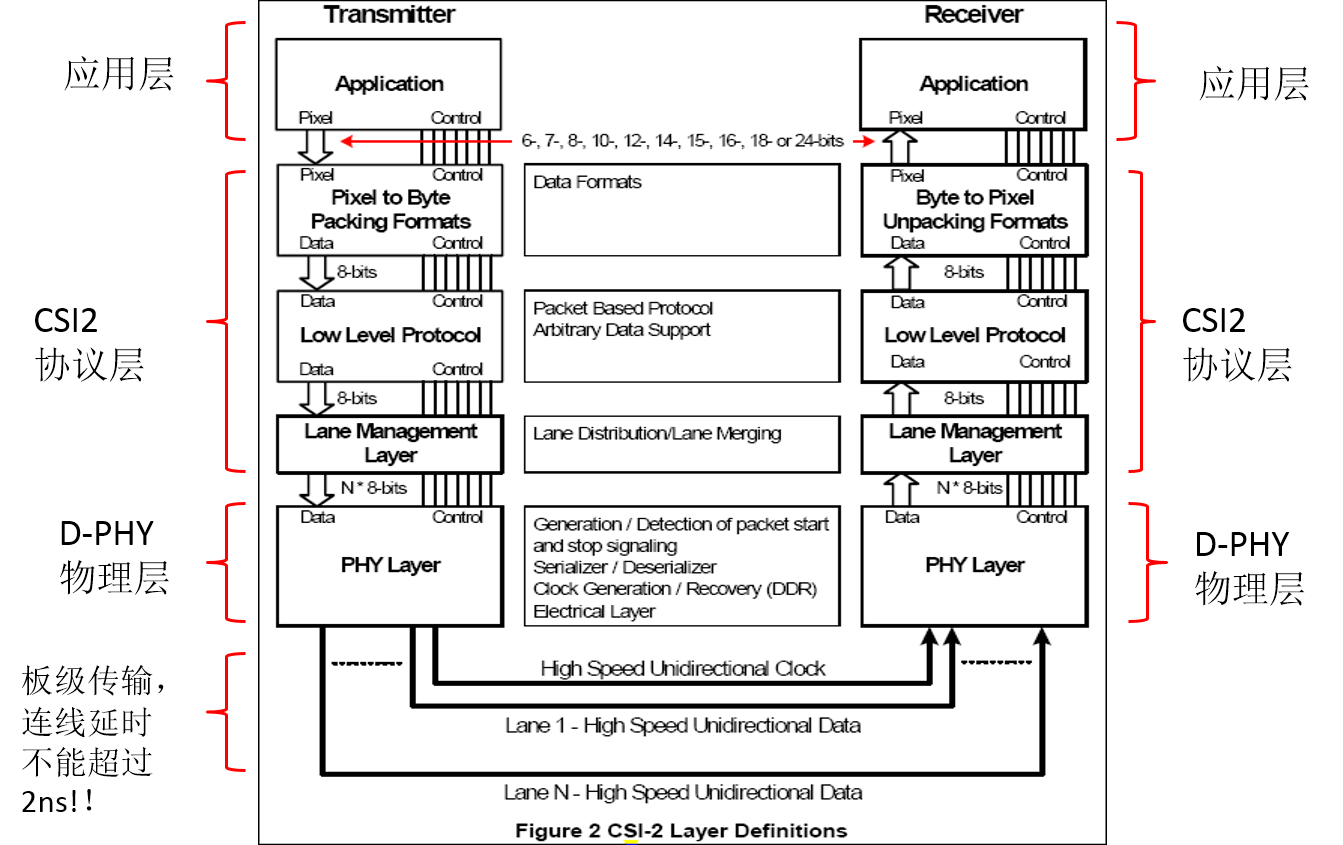

MIPI CSI -2

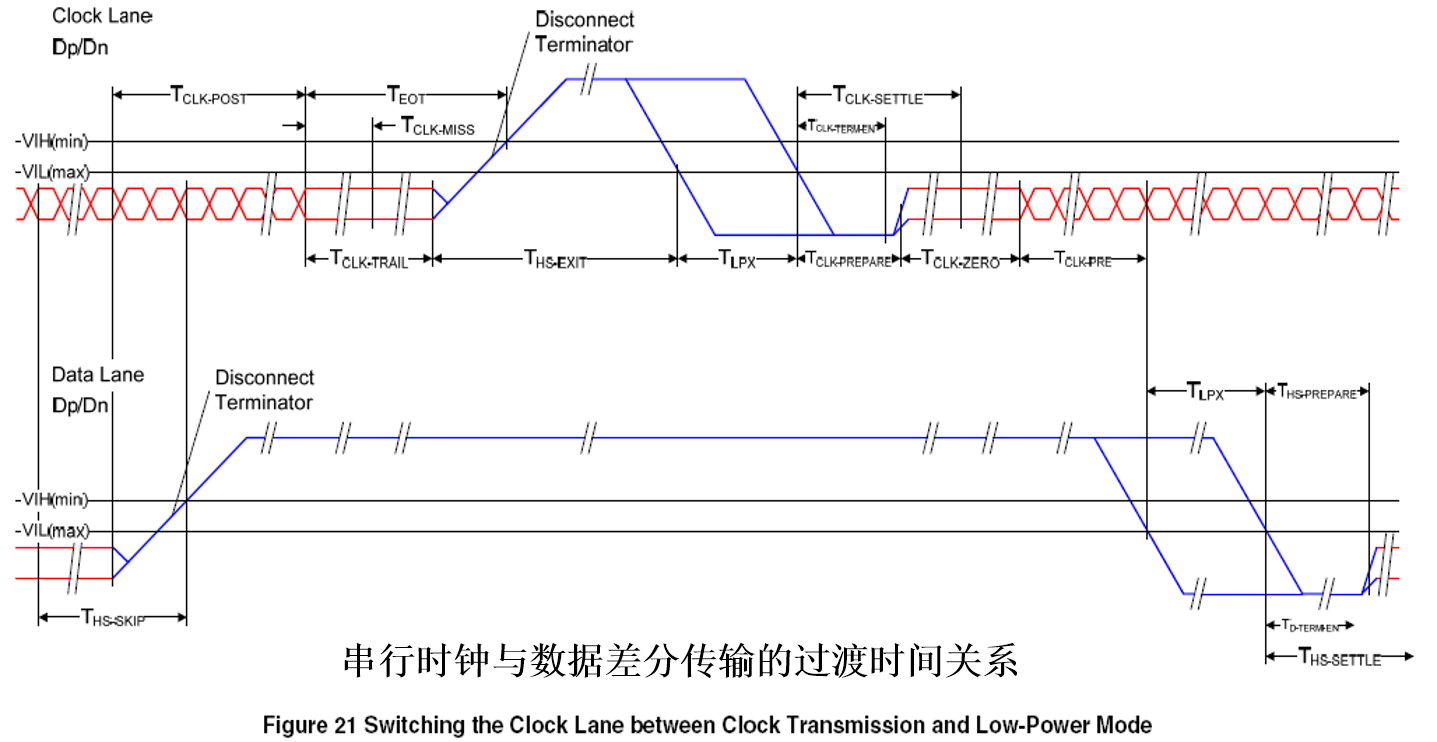

MIPI规定,传输过程中,包内是200mV、包间以及包启动和包结束时是1.2V,为了传输过程中各数据包之间的安全可靠过渡,从启动到数据开始传输,MIPI定义了比较长的可靠过渡时间,加起来最少也有600多ns;而且规定各个时间参数是可调的,所以需要一定等待时间,需要缓存。

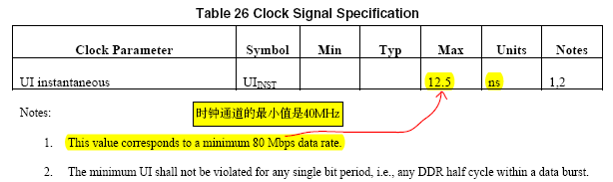

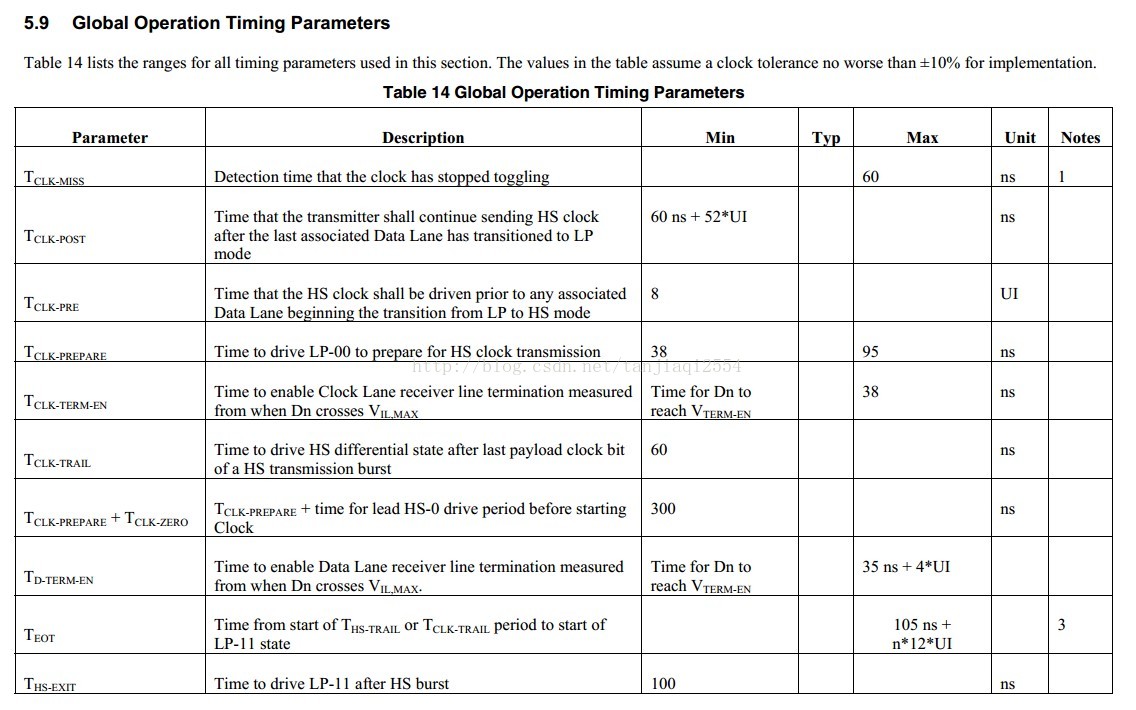

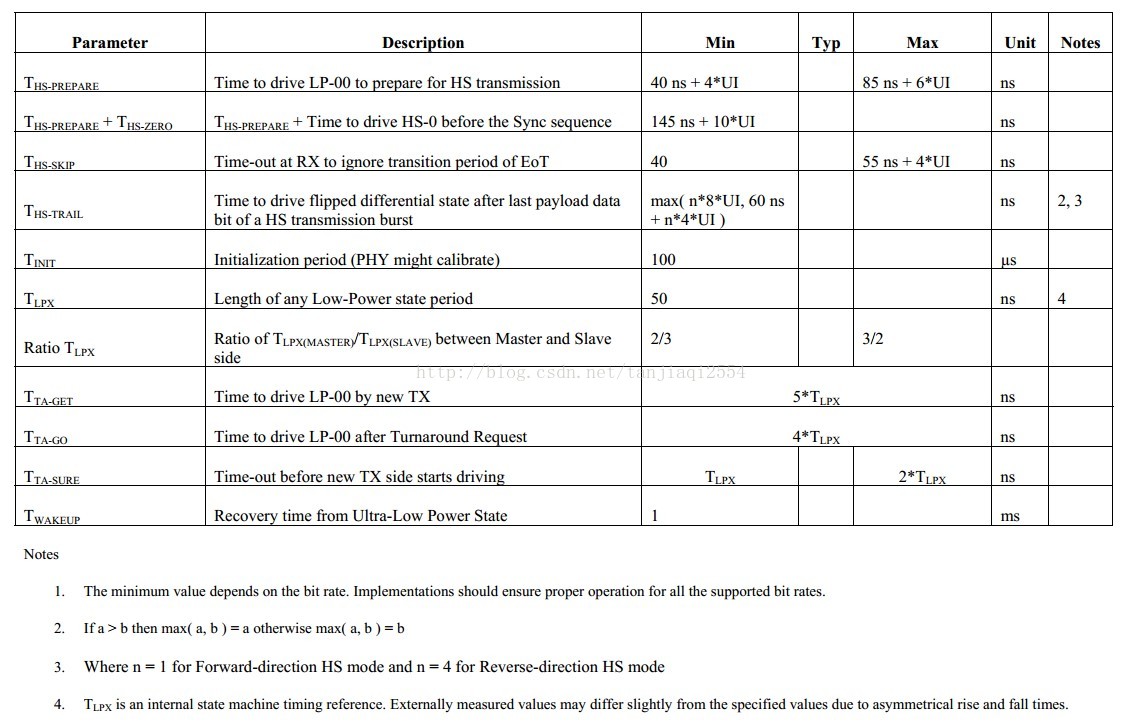

各个时间参数限制要求:

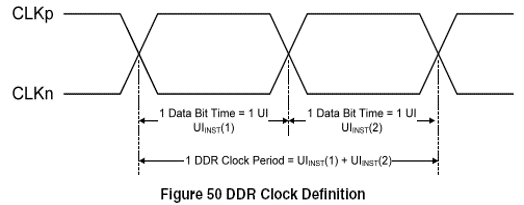

UI即MIPI的CLK lane的高速时钟High-Speed clock cycles周期的一半,因为MIPI是采用DDR时钟

CX3 MIPI控制器配置

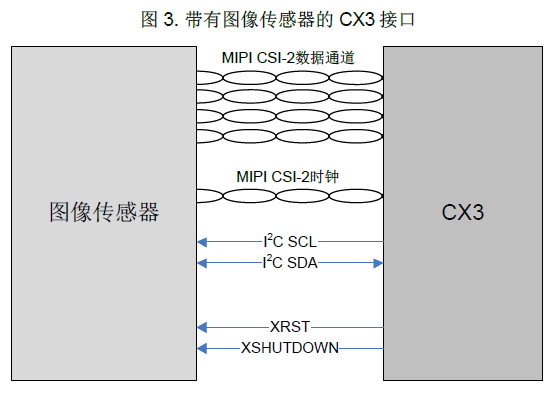

MIPI Camera Serial Interface (CSI) 接口是一个带有数据及时钟信号的单向差分串行接口。每次可以传输四个数据通道,数据速率可达1 Gbps。

XRST:CX3 中的复位信号。

XSHUTDOWN:可关闭传感器或使其进入待机模式以降低功耗。

MCLK:通过使用外部时钟振荡器提供图像传感器所需要的主(或参考)时钟。

CX3 MIPI控制器配置界面

H-active = H-Active*UI*位数/lane数

H-total = V-total / (V-Active+ V-Blanking)

V-active = V-total-V-Blanking*H-total

V-total = 1/帧率

参考时钟(REFCLK)

MIPI CSI-2 模块提供的参考时钟输入。该时钟输入的频率范围应为6 至40 MHz。CX3中,提供的时钟是19.2Mhz。

PLL 时钟(PLL_CLK)

MIPI CSI-2 模块的主要时钟。PLL 时钟的频率范围应为62.5 MHz 至1 GHz。其他所有的内部和输出时钟都来源于该时钟。

通过使用以下公式,可以从输入参考时钟生成PLL 时钟频率:

PLL_CLK = REFCLK * [(PLL_FBD + 1) / (PLL_PRD + 1) ] / (2^ PLL_FRS)

其中:

PLL_FBD 是反馈分频器,其范围值为0 至0x1FF(Multiplier of Unit Clk),CX3配置工具提供范围值参考。

PLL_PRD 是输入分频器,其范围值为0 至0x0F(Pre Divider Value)。

PLL_FRS 是频率范围选择的参数(PLL OutRange)。其值可以为:

‘0’,如果PLL 时钟频率的范围介于500 MHz 和1 GHz 之间。

‘1’,如果 if the PLL clock is between 250 MHz and 500 MHz.

‘2’,如果PLL 时钟频率的范围介于125 MHz 和250 MHz 之间。

‘3’,如果PLL 时钟频率的范围介于62.5 MHz 和125 MHz 之间。

CSI RX LP <—> HS 时钟

该时钟用于检测CSI 链路低功耗(LP) <—>高速(HS)的切换。通过对PLL_CLK 进行2、4 或8 分频(CSI RX Clock Divider)可以得到该时钟。该时钟的最大频率为125 MHz。

输出并行时钟(PCLK)

该时钟是PCLK 输出,用于驱动CX3 中功能固定的GPIF II 接口。通过对PLL_CLK 进行2、4 或8 分频(Output Parallel Pixel Clock Divider)可生成此时钟。

图像传感器的参考时钟(MCLK)

MCLK 是一个可选的时钟输出,可将它作为图像传感器的输入参考时钟使用。PLL_CLK 先进行mClkRefDiv(2/4/8)分频,然后再进行MCLKCTL 分频,从而生成该时钟

MCLK 可通过下面的公式计算得出:

MCLK = ( PLL_CLK/mClkRefDiv ) / [ ( HighByte (mClkCtl) + 1 ) + ( LowByte (mClkCtl) + 1 ) ]

如果PLL_CLK 的频率为672 MHz,那么要想生成频率为24 MHz 的MCLK,则需要将mClkRefDiv 设置为4, 并将mClkCtl 设置为0x0203。

当高字节(MClkCtl)和低字节(MclkCtl)均为非0 值时,MCLK 是唯一的输出。

mClkRefDiv、 MclkCtl的值均在结构体中直接修改,不在图形界面中更改

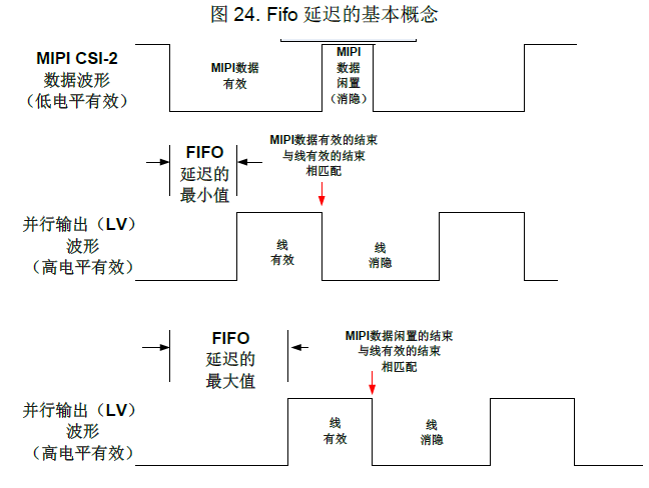

Fifo Delay

调节FIFO Delay Time。Fifo 延迟参数将在并行输出的每个线开头添加一个延迟。当输出并行像素时钟设置值大于该工具所建议的输出并行像素PCLK‘最小值’时,需要使用Fifo 延迟参数。

必须指出的是,fifo 延迟参数的最小值和最大值不是通过对MIPI H-有效时间和输出并行H-有效时间进行简单减法计算得出的。在MIPI 控制器中,只有一个行缓冲区可用,在计算Fifo 延迟时间时,需要计算该缓冲区。该工具负责进行此项调整。

发生下一个MIPI 线数据之前,应该通过并行接口完成发送当前的MIPI 线数据。如果违反该规则,可以在视频帧中观察到垂直分割。因此,要谨慎选择使用Fifo 延迟。

配置完成后,保存,生成相应的代码,用于配置对应的寄存器,通过对应的函数调用即可完成配置。另,从代码中可知,该工具不适用THS-Prepare和THS-Zero值字段。要想调整THS-Prepare和Zero值,SDK应支持一个API ‘CyU3PMipicsiSetPhyTimeDelay’,参考FX3的API手册。

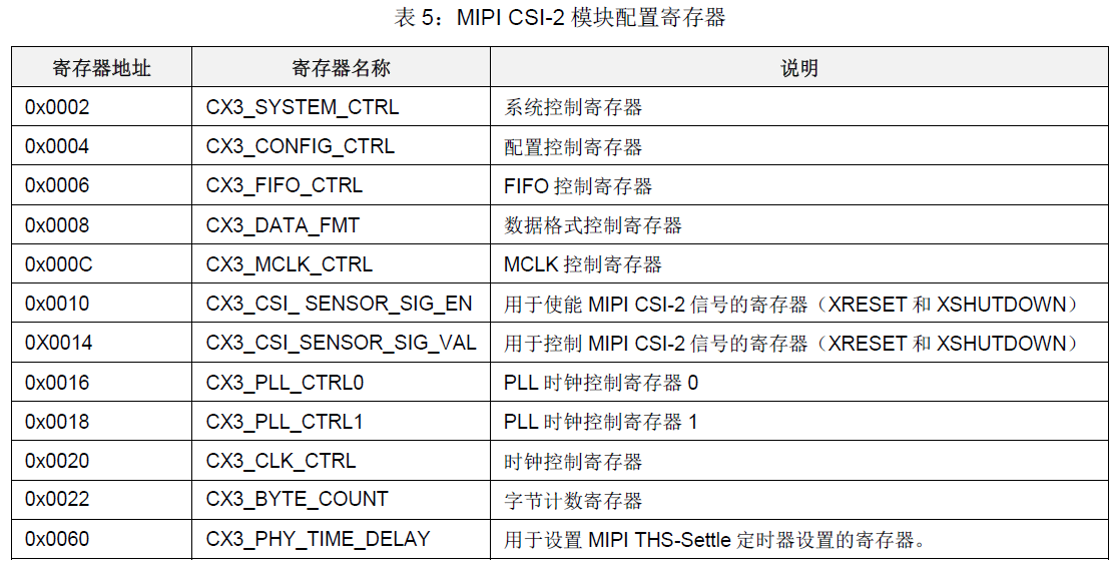

对应的寄存器见下表,具体的寄存器说明见CX3的技术参考手册。

配置过程中遇到的问题:

1.数据缺失,能正常传输,但每帧图像缺几行

解决方案:增大Multiplier of Unit Clk,或者减小Fifo Delay