SC8810 DDR PCB设计指南:

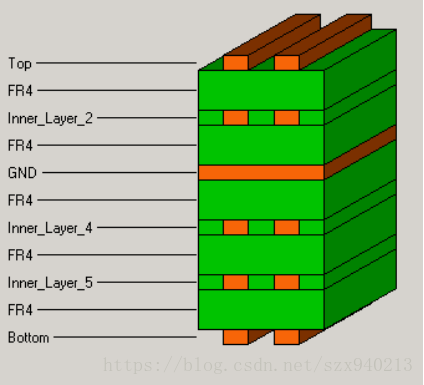

8层HDI板叠层指导:

TOP:Component(RF)

L2:Signal

L3:GND

L4: Signal(重要信号)

L5:GND

L6: Signal

L7: Signal

Bottom:LCM,KEY

6层(HDI)板叠层指导:

TOP:Component(RF)

L2:Signal

L3:GND

L4:Signal(重要信号)

L5:Signal

Bottom:LCM,KEY

PCB叠层的选择:

1:单面器件,另一面只有电池或LCM等器件的要可以做6层板。

2:半截板,L型板,U型板,镂空板等板型怪异,两面有器件对着的板子一定要做8层板。

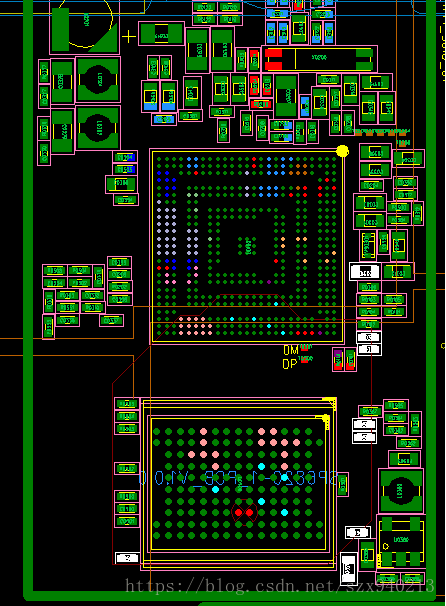

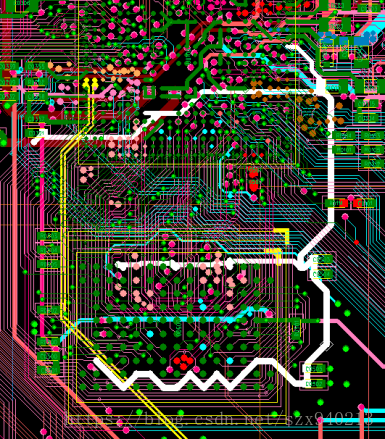

BaseBand和MCP布局:

如下图,BaseBand和MCP的P1脚采用如下的相对位置放置,两者之间留些位置方便走线,最好能有3mm以上。电容的位置要一组组分散在电源pin附近。

在Layout的时候要优先做好电源层和地。保证电源和地的完整。

DDR布线次序:

在DDR部分走线的时候,建议按以下的顺序来布线:

1.首先确定VDDMEM的电源平面和相邻层的地。电源平面先画好(6层板建议在L5层,8层板建议在L7层,TOP层是器件层)。

2.数据线

3.CLKDP,DM走线。

4.地址线和控制线

5.对于DDR的部分,一般数据线走在L1,L2层(表层的信号线尽量的短)。地址线,控制线走在L4层。

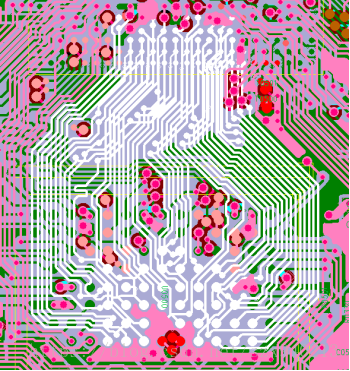

DDR 电源平面:

1.VDDMEM 一定要做电源平面(在BB的MCP区域和DDR区域,简单的说就是DDR的信号线到的地方都需要) , 相邻层要是地.电源和地层的间距不大于0.1mm, 对8层板 (器件在top层), 最好在L7层(相邻的L8层是地)。对6层板 (器件在top层), 最好在L5层(相邻的L6层最好是地).

2.VDDMEM如果在电源平面外的线宽至少0.5mm

3.每个电源管脚都要有过孔到电源平面.

4.VDDMEM的电容要靠近电源管脚摆放,0.1和0.01UF的电容要搭配在一起,分散在DDR的周围,电容的地管脚要有地空到主地层。

DDR CLK:

1.DDR的CLKDP,DM要差分走线,并完全保护好。

2.DDR的CLK走线不能在表层走长线,要走到内层。

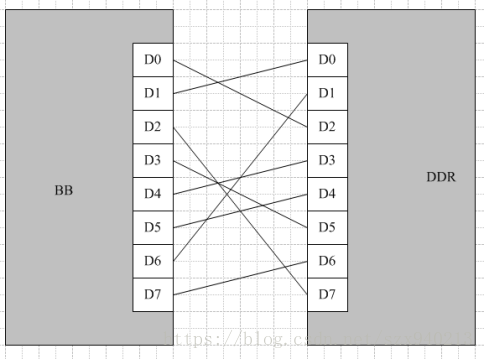

DDR数据线:

1.DDR的数据线总共有4组:BYTE0:DQ0~7,DQS0,DQM0; BYTE1:DQ8~15,DQS1,DQM1; BYTE2:DQ16~23,DQS2,DQM2; BYTE3:DQ24~31,DQS3,DQM3;

2.走线要组内一起走,并满足等长要求。

3.走线尽量在L1,L2层完全走完。

4.为方便走线,DDR数据线支持组内的交换(右下图).

DDR 走线的等长要求:

1.CLKDP,DM的长度差最大1mm

2.DQS和CLK的长度差最大5mm

3.数据线,DQM线对 DQS线 (组内)长度差最大3mm

4.不同组的DQS信号的长度差最大4mm

5.地址线,控制线对CLK的长度差是最大5mm

6.地址线之间的长度差是最大6mm

7.相同性质的信号线上过孔的数量要一致 (DQ≤ 3,CLK,Address,control ≤4)

案例1:

1.8层HDI板,板厚0.8mm,叠层如下,没有电源层,等长基本符合要求。DDR时序有问题。

2.问题主要在于没有电源层。电源的电容也不多。