| 十进制数 | 自然二进制数 | 格雷码 |

|---|---|---|

| 0 | 0000 | 0000 |

| 1 | 0001 | 0001 |

| 2 | 0010 | 0011 |

| 3 | 0011 | 0010 |

| 4 | 0100 | 0110 |

| 5 | 0101 | 0111 |

| 6 | 0110 | 0101 |

| 7 | 0111 | 0100 |

| 8 | 1000 | 1100 |

| 9 | 1001 | 1101 |

| 10 | 1010 | 1111 |

| 11 | 1011 | 1110 |

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

格雷码转换二进制码的逻辑关系为:

bin[0]=gray[3]^gray[2] ^gray[1] ^gray[0]

bin[1]=gray[3]^gray[2] ^gray[1]

bin[2]=gray[3]^gray[2]

bin[3]=gray[3]

设计代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/07

// Design Name:

// Module Name: Test1103

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

module Test1103(gray,bin,clk,inc,rst_n);

parameter size=4;

output [size-1:0] gray,bin;

input clk,inc,rst_n;

reg [size-1:0] gnext,gray,bnext,bin;

integer i;

///

always @(posedge clk or negedge rst_n)

if(!rst_n)

gray<=0;

else

gray<=gnext;

///

always @(gray or inc)

begin

for(i=0;i<size;i=i+1)

bin[i]= ^(gray>>i);

bnext=bin+inc;

gnext=(bnext>>1) ^ bnext;

end

endmodule

测试代码(Testbench)

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/07

// Design Name:

// Module Name: Test1110

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

module Test1110;

reg clk;

reg rst_n;

reg inc;

wire [3:0] gray,bin;

always begin

#10 clk=0;

#10 clk=1;

end

initial begin

clk=0;

inc=0;

rst_n=0;

#100;

rst_n=1;

#20;

inc=1;

end

Test1103 x1(.gray (gray ),

.bin (bin ),

.clk (clk ),

.inc (inc ),

.rst_n(rst_n));

endmodule

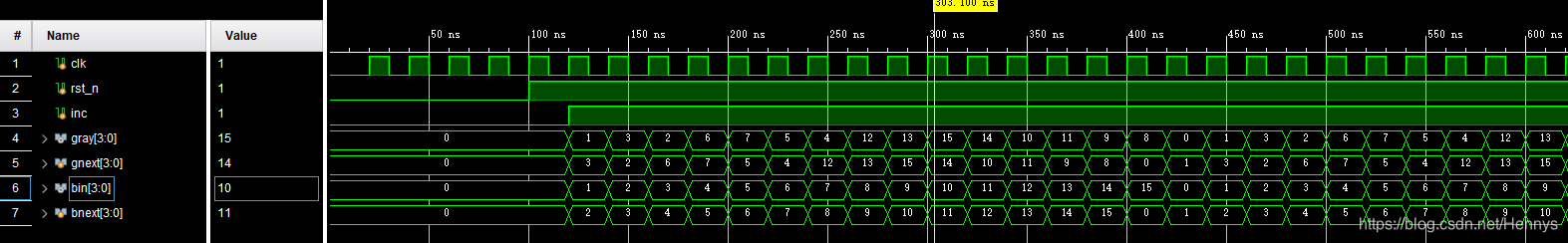

仿真波形如下