一、什么是AXI?

AXI(Advanced eXtensible Interface, 高级可扩展接口)隶属于ARM AMBA(Advanced Microcontroller Bus Architecture)家族,AMBA是1996年ARM引入的微控制器总线标准。AMBA的本质是开放的片内总线互联标准,为多主机设计中多个微控制器和外围设备的连接和管理提供了基础。

AXI于2003年在AMBA3.0标准中首次出现,于2010年发布的AMBA4.0则推出了AXI,AXI4的第二个主流版本,并广泛使用至今。

二、AXI接口的类型

有三种形式的AXI接口,Xilinx的官方文档UG1037中对它们的描述如下:

- AXI4(AXI4-Full):为了满足高性能存储器映射的需求

- AXI-Lite:简化版的AXI4接口,为了简单、低吞吐量的存储器映射通信(例如到控制寄存器和状态寄存器的通信)

- AXI4-Stream(AXI-ST):为了高速的流式数据通信而设计(比如视频流),不属于存储映射的范围。

在这里简单补充一下存储器映射(Memory-Mapped)的概念(Quoted From The Zynq Book):如果一个协议是存储映射的,那么在主机所发出的会话中(无论读或写)中就会标明一个地址,这个地址是对应于系统存储空间中的一个地址。也就是在AXI4的语境下,所有对外设的访问都会被抽象为对特定存储空间地址的访问。

三、AXI协议的优势

-

生产力:通过将AXI接口标准化,开发者只需要学习一个简单的协议。

-

灵活性:正如上面分类所述,有三种不同类型的AXI4接口提供了广泛的应用场景(这里还有一些关于三种接口的详细说明,不再详述了)

-

可获得性:通过成为事实上的工业标准,不仅可以使用到各式各样的IP核,也同时加入到ARM全球的合作者中

四、AXI如何工作?- AXI和AXI-Lite接口都包含5个不同的通道:读地址通道、写地址通道、读数据通道、写数据通道、写响应通道。数据可以在主从端口之间同时地双向传输,数据传输规格是可变的。AXI4协议支持一次高达256个数据的猝发传输,而AXI-Lite则一次只能传输一个数据。

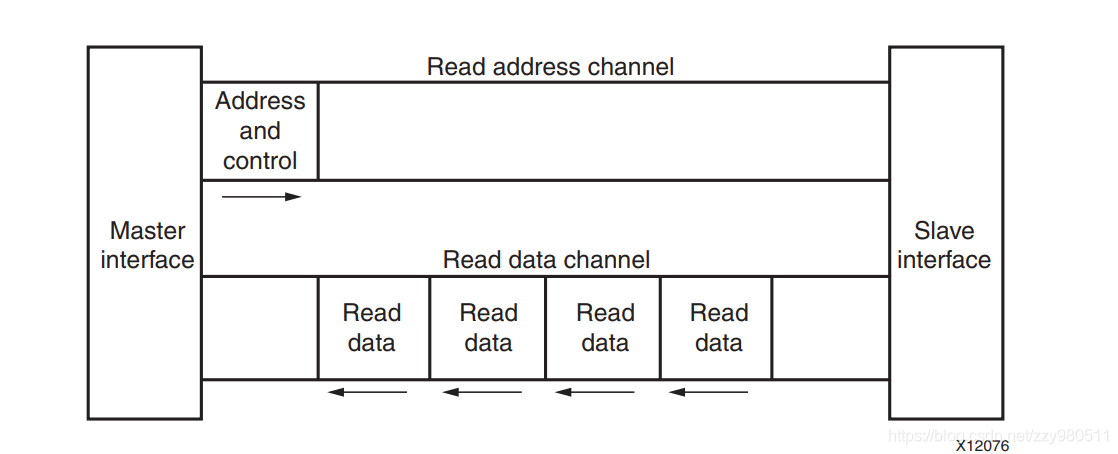

- 下面的图片展示了一次AXI4读事务的执行时序:

也就是主机首先向从机发送要读的地址和控制信息(比如说促发传输的数据长度),随后从机向主机返回连续的数据。

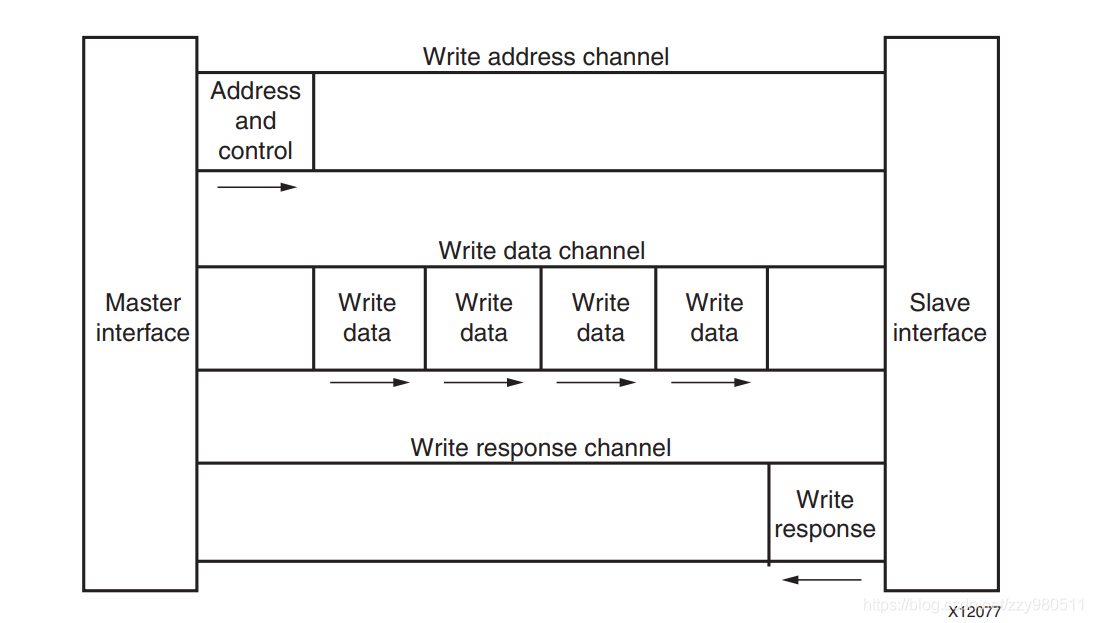

3.下面的图片展示了一次AXI4写事务的执行时序:

也就是在执行写事务时,主机首先向从机发送要写入的地址和控制信号,随后连续发送要写入的数据流,从机在接受到数据之后返回一个写响应信号来表示成功接收到主机发送的数据。

正如上述所展示的,由于读和写的数据通道和地址通道不重合,所以AXI4支持同时的、双向的数据传输。AXI4-Lite和AXI4十分相似,不同的是它不支持猝发式传输(猝发式传输:主机指定一个起始地址,连续写入多个数据,下一个要写入的地址的计算由从机来完成,计算往往是有规律可循的,例如连续递增),而一次只能传输一个数据。而AXI-Stream完全类似于AXI4中的写通道(也就是说AXI-Stream是单向的),与之不同的是AXI4-Stream的猝发传输是没有上限约束的,而AXI4有256个数据的最大量限制。

最后还不得不提的一个重要部分是基础设计IP核,这些IP核是用来将系统组装起来的“粘合剂”,它们并非是数据的终端。常见的IP核如下:

- AXI Register Slice(用来流水化)

- AXI FIFOs(为了起到缓冲作用和时钟域转换)

- AXI Interconnect IP and AXI SmartConnect IP(用于将存储器映射的IP连接到一起)

- AXI DMA 引擎(将存储器映射访存向流式数据转换)

- AXI Performance Monitors and Protocol Checkers(用于分析和debug)

- AXI验证IP(用于基于仿真的验证和性能分析)

五、AXI的通道描述

- 每一个独立的通道(channel)都由一组信息信号(数据)和专用于提供双向握手信号的VALID和READY信号组成。 数据发送者使用VALID信号来表明有效地址、数据或控制信息已经可用,数据目的地则使用READY信号来表示它已经可以接受数据。除此之外,还有一个LAST信号,在一次数据传输的结尾处,数据发送者会在最后一个数据传送时将LAST信号电平拉高来表明这是最后一个数据项。

- 读和写地址通道:每一个读写事务都有自己的地址通道,地址通道包含一次传输所有的地址和控制信息。

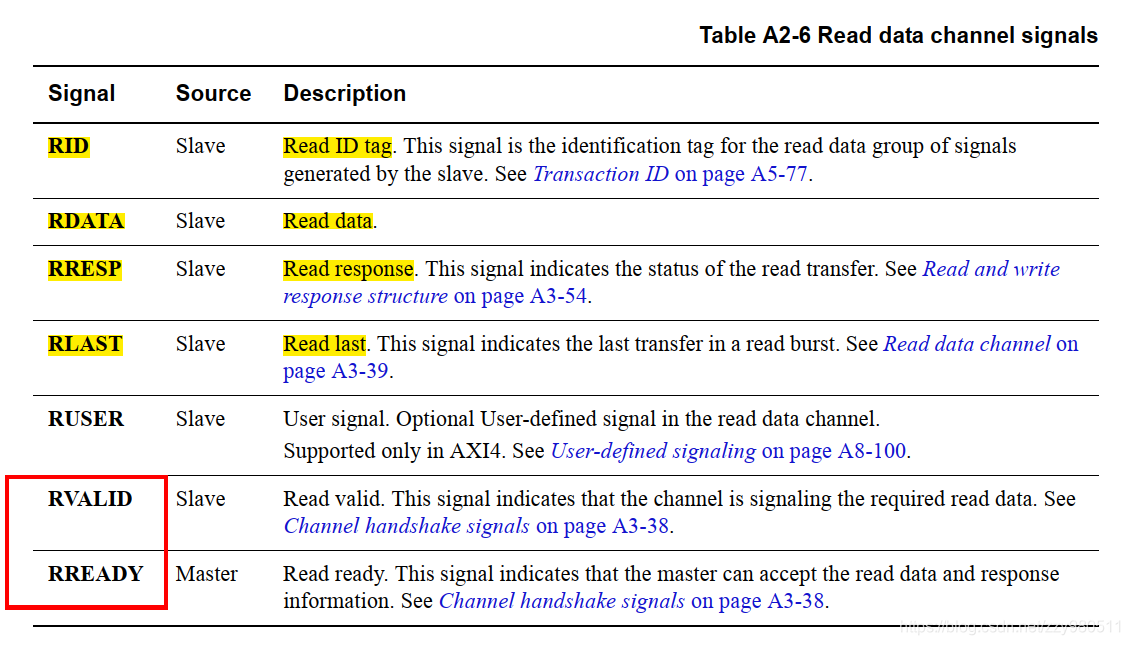

- 读数据通道:读数据通道不仅负责传输从机到主机的读数据信息,还负责传输从机到主机的读响应信息。它包含:一条数据总线,位宽可以是8、16、32、64、128、256、512、1024;一个读响应信号用来表明读事务完成的状态。

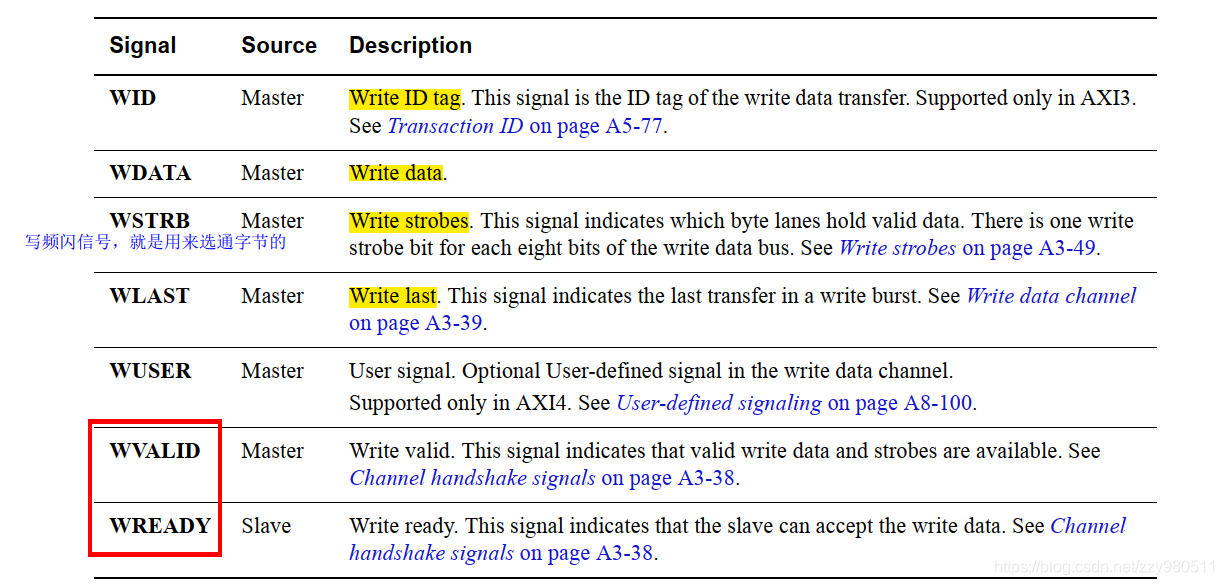

- 写数据通道:写数据通道负责传输主机到从机的数据,它包含:一条数据总线,位宽可以是8、16、32、64、128、256、512、1024;一个为每8个比特传输数据(也就是一字节)准备的字节选通信号(或者叫频闪信号),用来告诉从机传输过程中的哪一个字节是真正有效的。

让我再细致的解释一下字节选通信号,假设写数据通道有一条32位宽的数据总线,那么就会有一个4位的字节选通信号(32位=4字节)在旁边提示这4个字节的可用性。如果选通信号为1110,那么就表示前三个字节是有效的,最后25-32位的那个字节就是无效的,从端口不接收。

最后,写数据通道默认情况下带缓冲,所以主机无需等待从机对上一次写事务的响应就可以开始下一次数据传输。 - 写响应通道:从机需要使用写响应通道来对写事务做出响应,需要注意的是写响应是在整个事务结束时进行一次响应,而非每一个数据传输结束时都要响应一次,更不能在传输数据的过程中发出写响应信号。

六、AXI4-FULL的信号描述

关于这部分,技术手册上做了很清晰的解释,我就不再赘述了,我是一个莫得感情的截图机器:

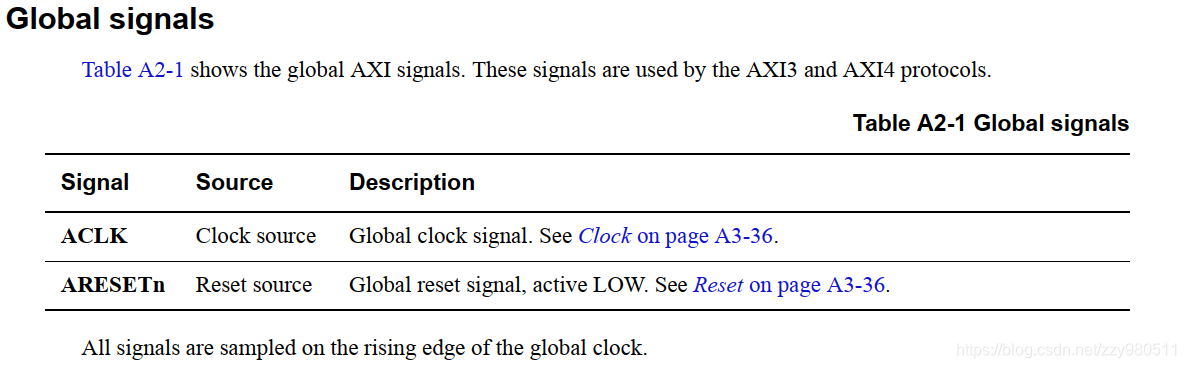

- 全局信号:ACLK和ARESETn分别是全局时钟信号和全局复位信号,注意全局复位信号低电平有效,所有信号都在全局时钟的上升沿采样。

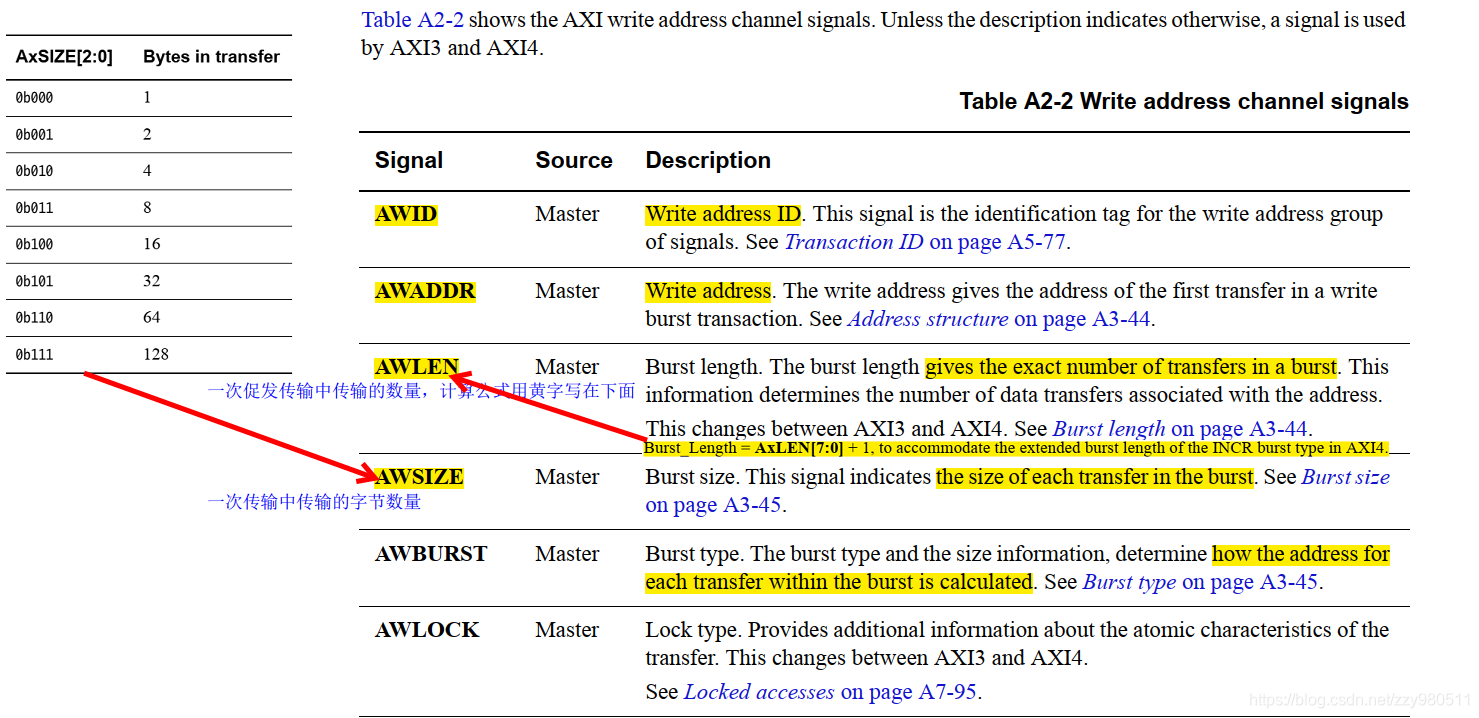

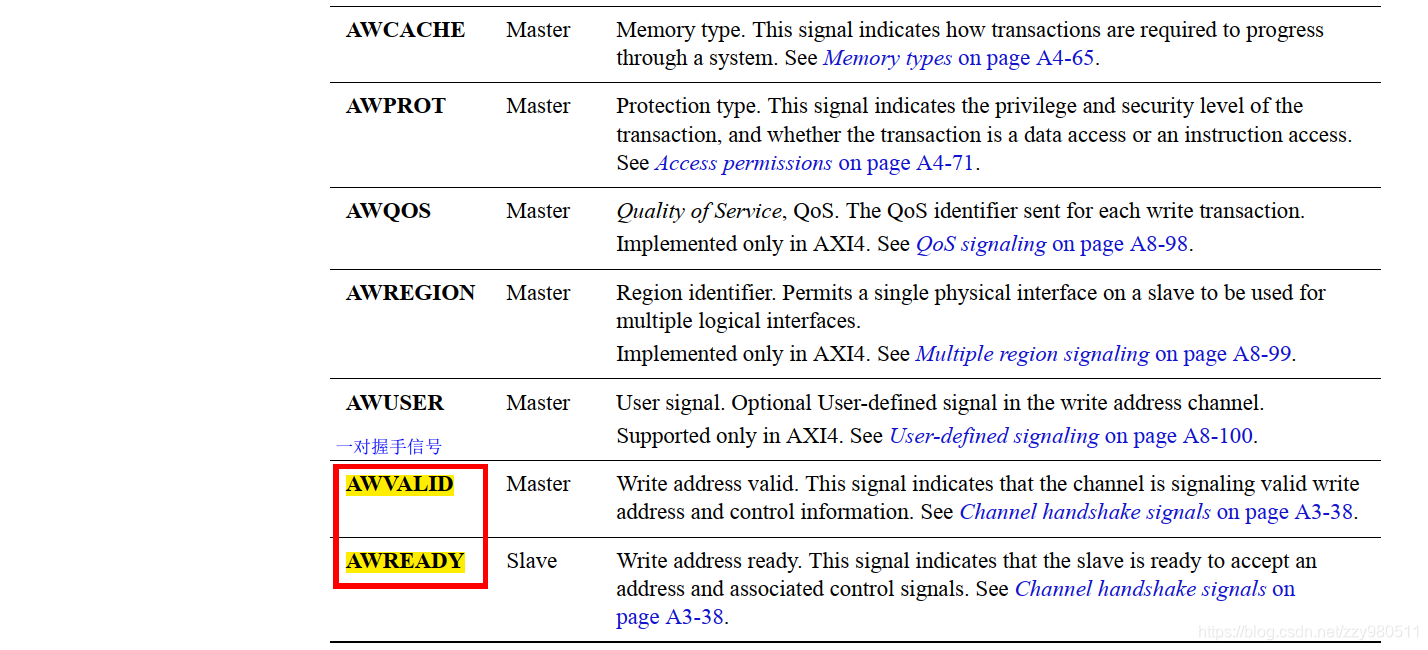

2.写地址通道信号

2.写地址通道信号

3.写数据通道信号

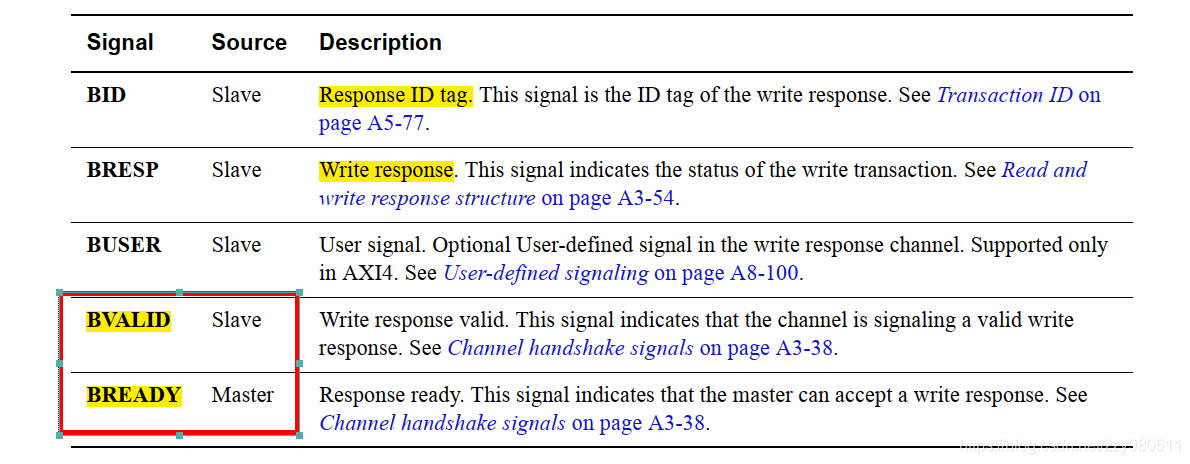

4.写响应通道信号

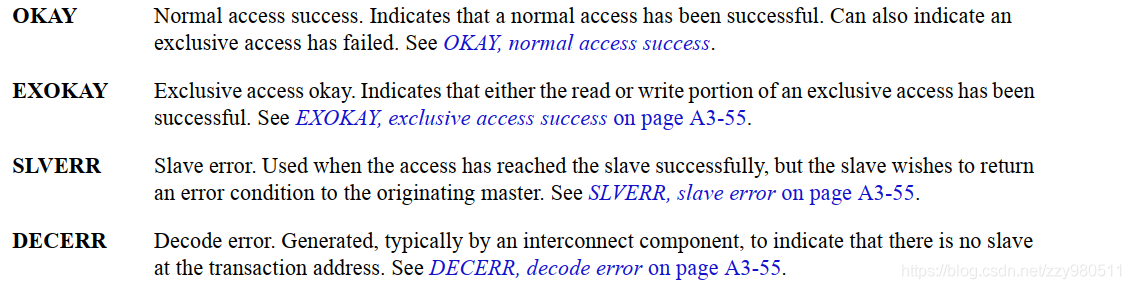

关于响应信号,有以下四种:

OKAY:通常状态下的访问成功信号

EXOKAY:独占式访问成功信号

SLVERR:从机错误,表示已经成功连接到从机,但是从机期望向主机返回一个错误状态

DECERR:解码错误,一般情况下是由互联(Interconnect)产生的,表明指定的传输地址处未找到从及设备

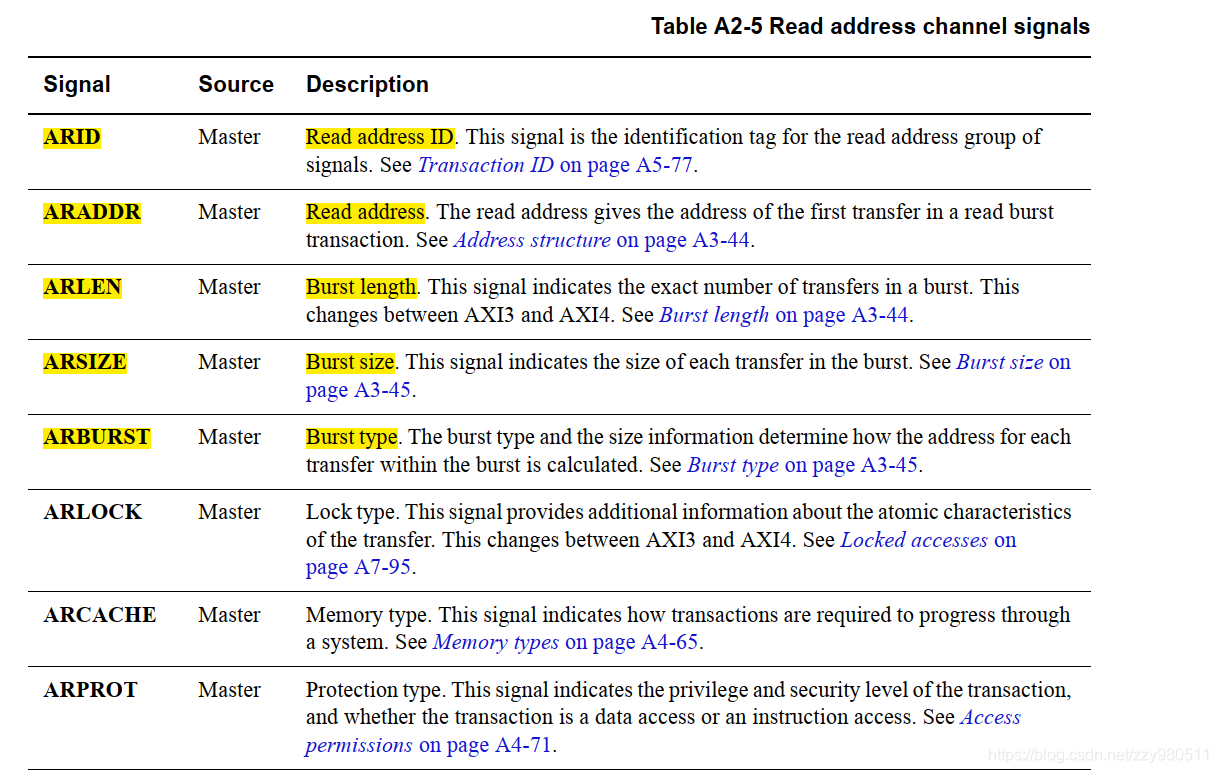

5.读地址通道

读地址通道和写地址通道是十分类似的:

6.读数据通道

六、一对主从接口通信的波形图分析

1.时钟信号(ACLK)

每一个AXI组件都要使用一个时钟信号,ACLK。所有的输入信号将在时钟上升沿进行采样,所有的输出信号变化一定要在时钟上升沿发生。

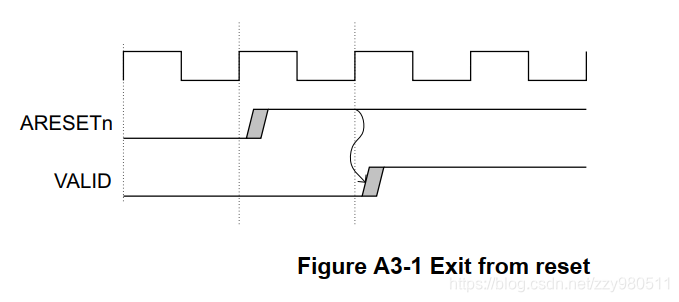

2.复位信号(ARESETn)

复位信号低有效,复位信号的开启可以异步实现(也就是没必要等待全局时钟信号的到来,什么时候都可以拉低复位信号来表示复位)。然而,复位信号的关闭就需要等到一个ACLK的上升沿到来才可以。

在复位信号有效时,要完成以下几个事务:

A.主端口将写地址有效(AWVALID),读地址有效(ARVALID)和写有效(WVALID)电平拉低

B.从端口将读有效(RVALID)和写响应有效(BVALID)电平拉低

C.其他所有信号将被置为不确定值

允许将信号再次置高的最早时间是复位信号(ARESETn)恢复为高电平之后的最早的一个全局时钟上升沿。

3.握手信号

所有的五大传输通道都使用READY/VALID握手过程来实现对控制信息、地址信息、数据信息的传输,双向的握手信号使得主从两端都可以来主动地调节数据传输过程,数据的源端使用VALID信号来表示自己已经准备好,数据的目的端使用READY信号来表示自己已经准备好。一次传输只有在READY和VALID升高时才正式开始。

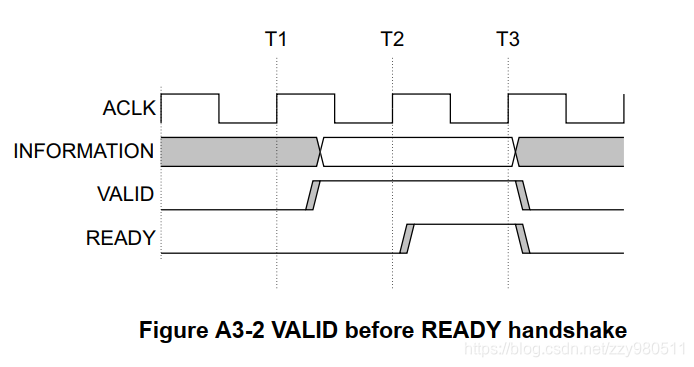

有三种情况的握手:

A.VALID信号先于READY信号被建立

- 在VALID建立之后,READY建立之前,数据源端必须保持VALID信号的高电平,并且保证所有的数据信息(Information)稳定,直至握手发生,数据开始传输。

- 数据源端不允许等到READY信号到来之后再把VALID信号置为高电平,也就是一旦准备好数据就得把VALID升为高电平,源端不允许把READY高电平的到来作为VALID升高的条件。

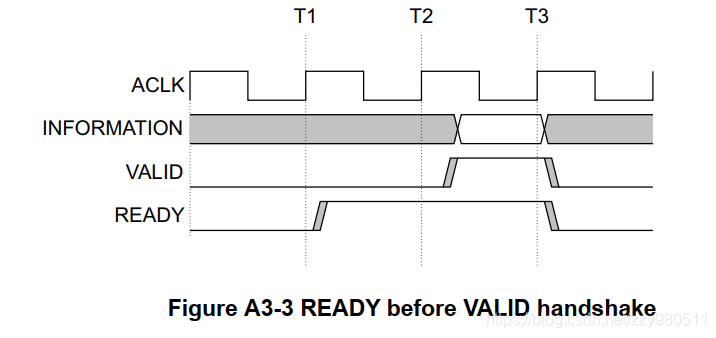

B.READY信号先于VALID信号被建立

- 对于数据目的端,可以将VALID信号的到来作为READY信号升高的条件,甚至就算从机准备好了,升高了READY信号之后,如果这时它检测到VALID信号没有到来,都可以再次拉低READY信号,这点和情况A中完全不同。

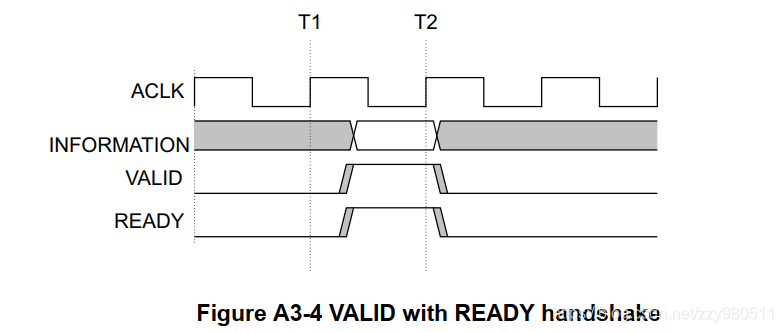

C.VALID信号和READY信号同时建立

这种情况下,第一个检测到VALID和READY信号都处于高电平的时钟上升沿开始数据传输。

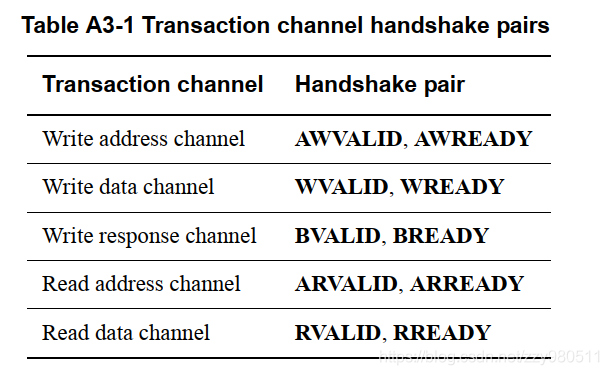

最后,附上五种握手场景下的握手信号对:

七、通道握手信号时序上的依赖关系

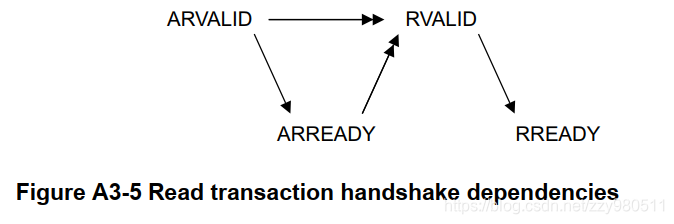

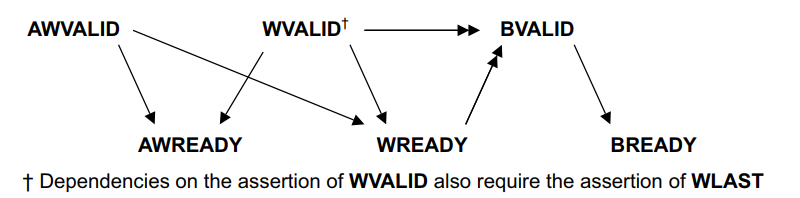

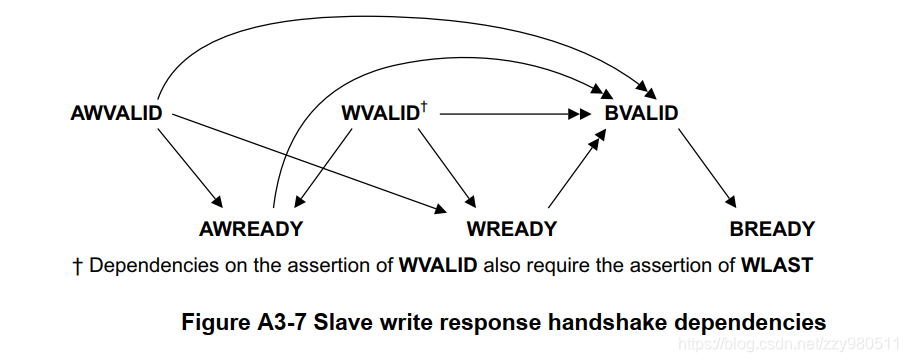

在图例中,单头箭表示不严格的时序关系,双头箭表示严格的时序关系。那么我们可以将几种事务中的依赖关系图表示如下:

-

读事务信号依赖图

-

写事务信号依赖图

注意注释:WVALID信号的建立在最后一个数据传输时依赖于WLAST信号的建立。

3.写响应信号依赖图

同样也需要注意WVALID信号的建立在最后一个数据传输时依赖于WLAST信号的建立。

八、AXI-Lite接口特性

AXI-Lite接口一般用于对控制或状态寄存器的简单读写情景,它有以下一些特点 -

猝发长度均为1

-

所有数据传输均占满数据通道(AXI-Lite只支持32位和64位两种位宽)

-

所有的读写过程不可定制或修改,没有缓冲

-

不支持独占式访问