AXI总线:一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由数据线、地址线、控制线等构成。

AXI接口:接口是一种连接标准,称为物理接口。

AXI协议:传输数据的规则。

在ZYNQ中,支持三种AXI总线,拥有三种AXI接口,

三种AXI总线分别为:

(1)AXI4:(For hign-performance memory-mapped requirements)主要面向高性能地址映射通信的需求,面向地址映射的接口,允许最大256轮的数据猝发传输

(2)AXI4-Lite:(For simple,low-throughput memory-mapped communication)轻量级的地址映射单次传输接口,占用很少的逻辑单元。

(3)AXI4-Stream:(For hign-speed streaming data)面向高速流数据传输,去掉地址项,允许无限制的数据猝发传输规模。

三种AXI接口:

(1)AXI-GP接口:通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过改接口可以访问PS中的片内外设。

(2)AXI-HP接口:是高性能/带宽的标准的接口,PL模块作为主设备,主要用于PL访问PS上的存储器(DDR和on -chip RAM)

(3)AXI-ACP:ARM多核架构下定义的一种接口(加速器一致性端口),用来管理DMA之类的不带缓存的AXI外设,PS端是slave端口

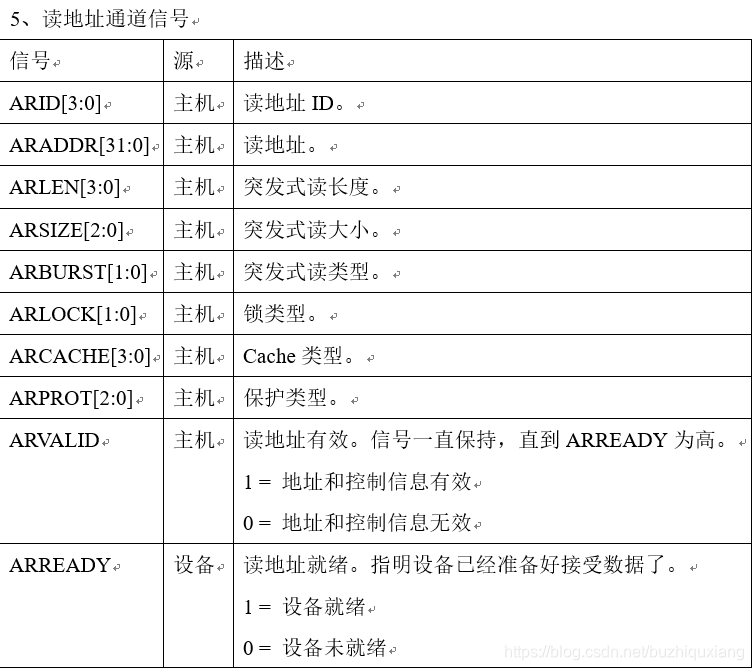

AXI总线由5个通道组成:

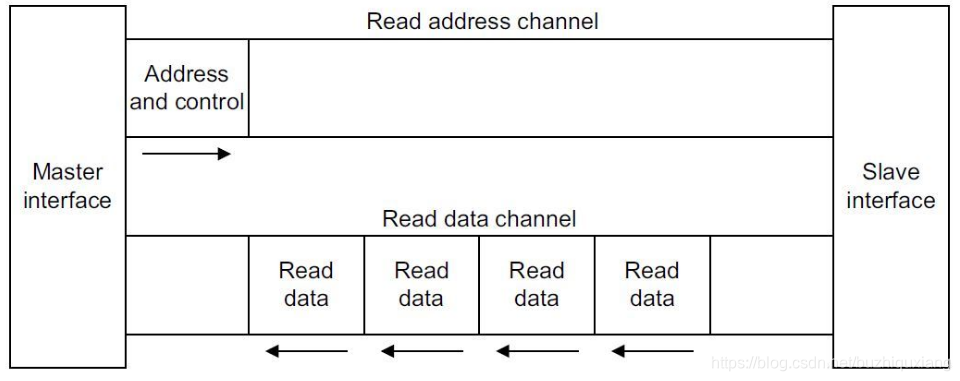

(1)read address 读地址通道:(主机->从机)

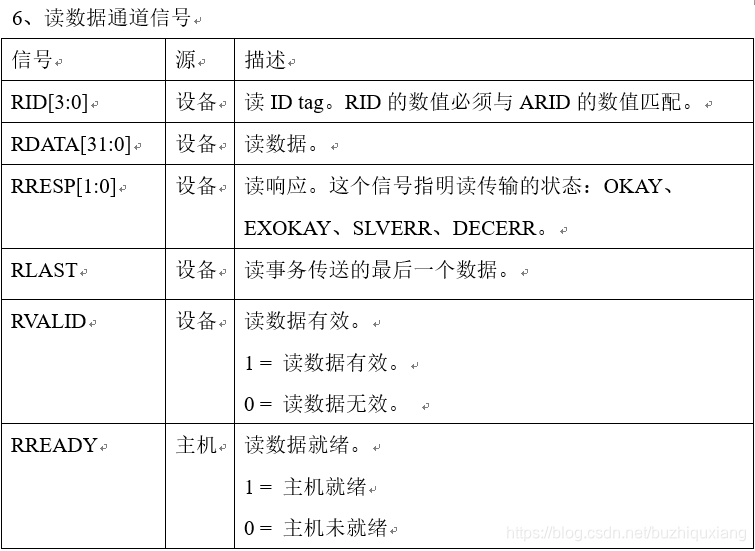

(2)read data 读数据通道(包括数据通道和读响应通道):(从机->主机)

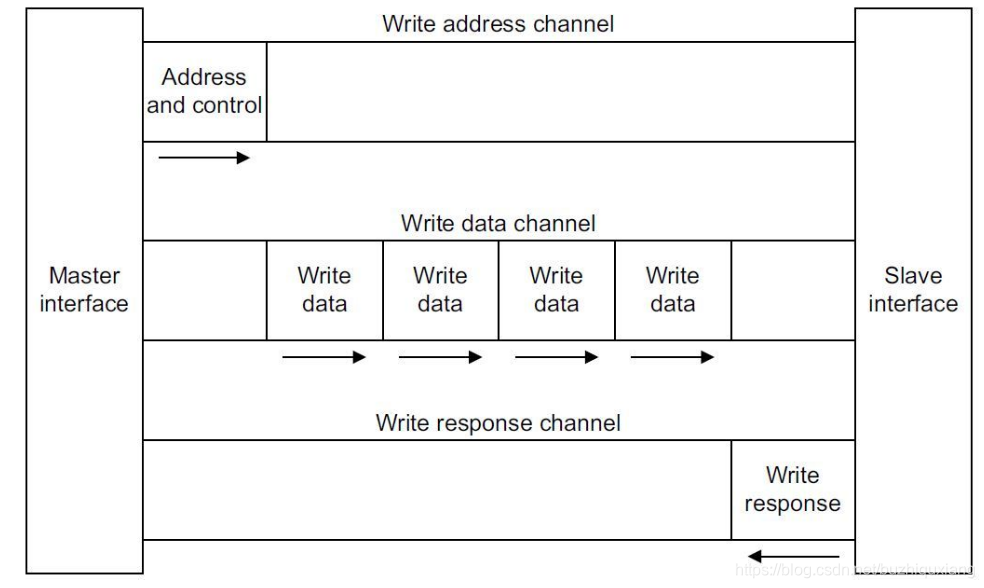

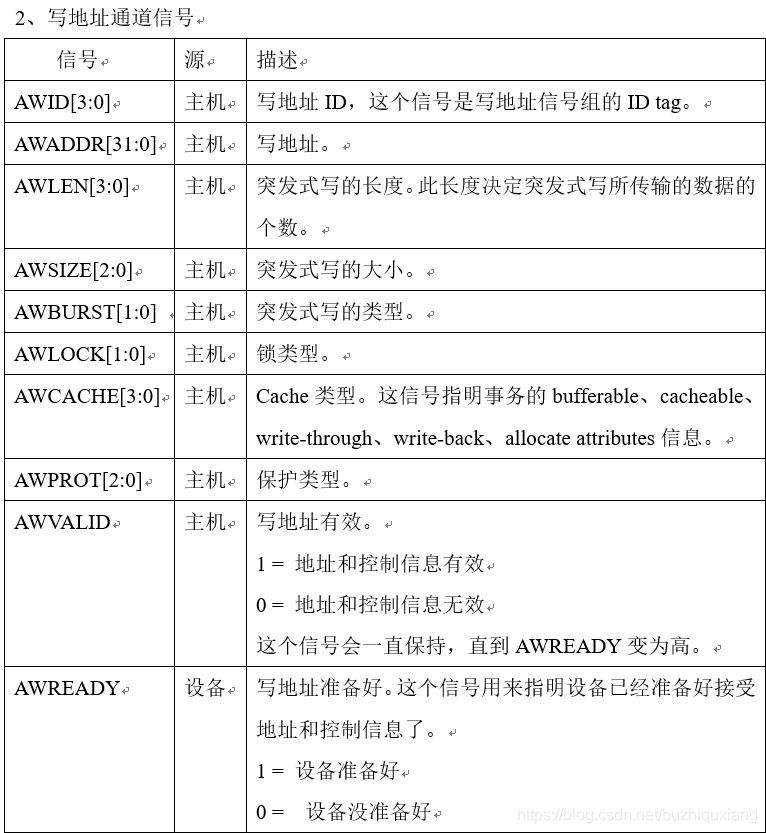

(3)write address 写地址通道 :(主机->从机)

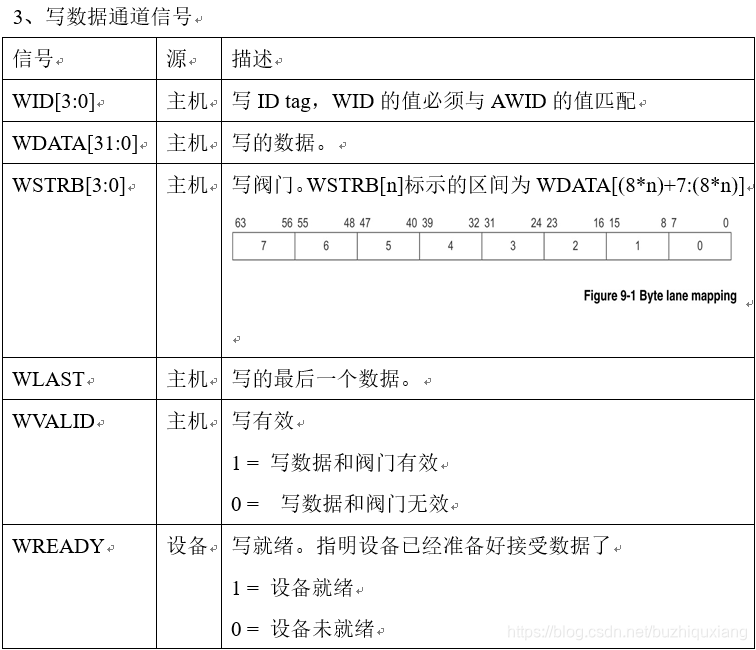

(4)write data 写数据通道(包括写数据通道和写数据有效信号) :(主机->从机)

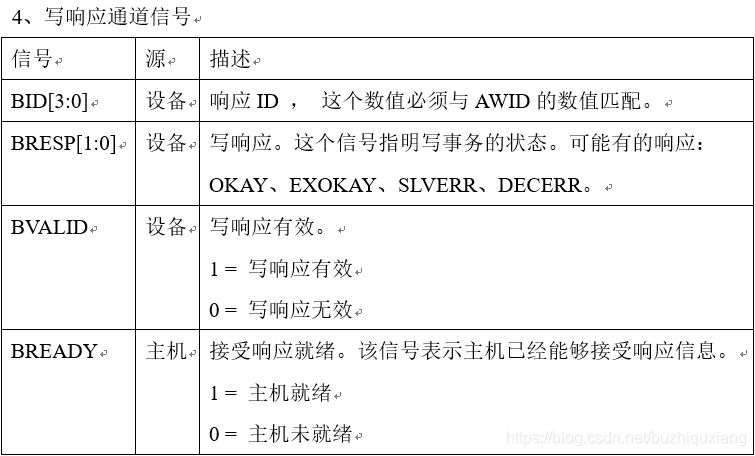

(5)write respone 写响应通道 :(从机->主机)

读操作通道

写操作通道

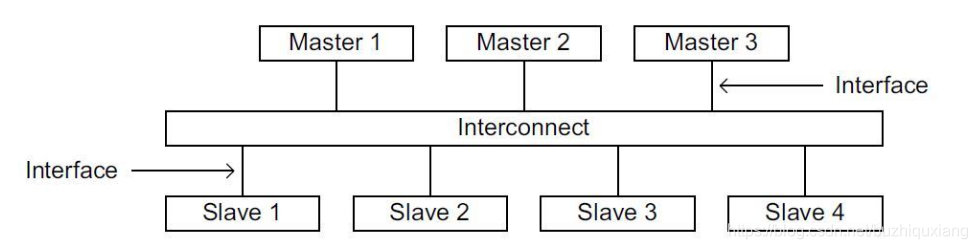

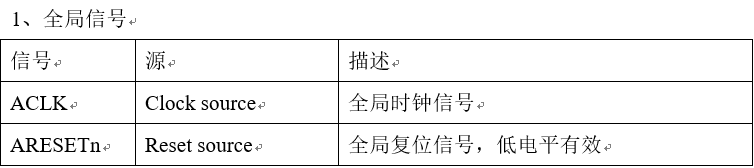

(一)AXI系统

AXI master :AXI 通信主机

AXI slave : AXI 通信从机

AXI interconnect : AXI 通信通路

(二)AXI接口时序

(1)复位

复位信号可以异步复位,但必须同步释放,复位时,信号要求:

- 主机驱动的所有VALID信号(ARVALID(读地址有效,有效时表示ARADDR上地址有效),AWVALID(写地址有效,有效时表示AWADDR上地址有效),WVALID(写有效信号,有效时表示WDATA上数据有效))必须拉低;

- 从机驱动的所有VALID信号(RVALID(读数据有效),BVALID(写响应信号有效))必须拉低

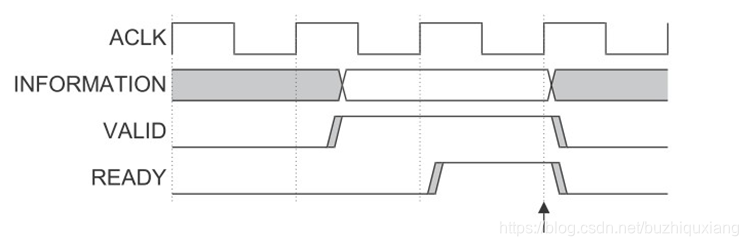

(2)握手信号

握手信号包括VALID和READY信号,**传输行为仅在VALID和READY同时有效时发生。**其中:

VALID信号表示地址/数据/响应总线上的信号是有效的,由传输发起方控制。

READY信号表示传输接收方已经准备好接收,由传输接收方控制。

VALID和READY信号的出现由三种关系:

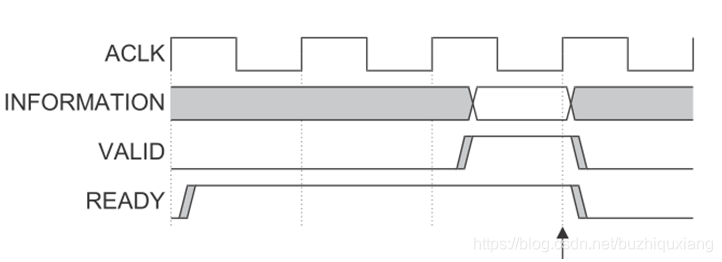

(1)VALID先变高READY后变高(在箭头处信息传输发生)

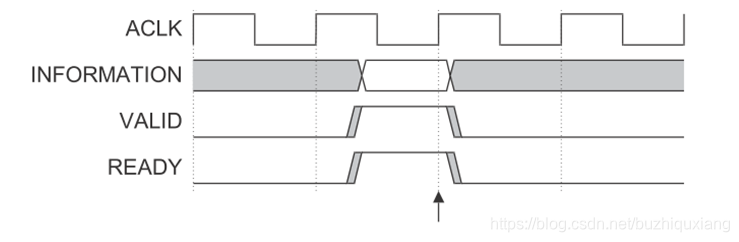

(2)READY先变高VALID后变高

(3)VALID和READY信号同时变高

通道之间的关系:

(1)读数据必须在与其数据相关联的地址之后

(2)写响应必须在与其关联的写通道的之后进行

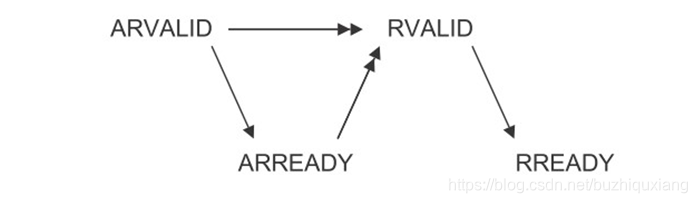

读通道握手依赖关系如图:(单箭头表示可以等待有效再置位,双箭头表示必须等待有效在置位)

(1)设备可以在ARVALID(读地址有效信号)出现时给出ARREADY(写有效信号,表示从机已经准备好接收读地址),也可以先给出ARREADY信号,再等待ARVALID信号。

(2)但是设备必须等待ARVALID和ARREADY信号都有效后才能给出RVALID信号,开始数据传输。

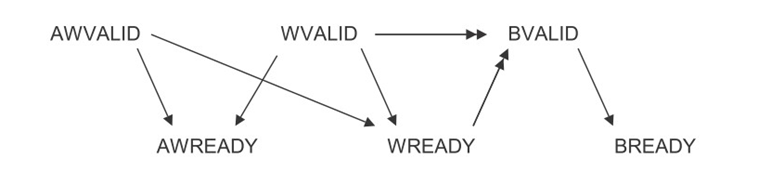

写通道握手依赖关系如图:

(1)写响应通道BVALID,仅当WVALID和WREADY信号同时有效(即数据传输完成)且WLAST信号有效(猝发传输的最后一个数据传输完成)后才会被置位。

(三)AXI猝发读写

(1)与AHB总线一样,猝发传输不能够跨越4KB地址空间

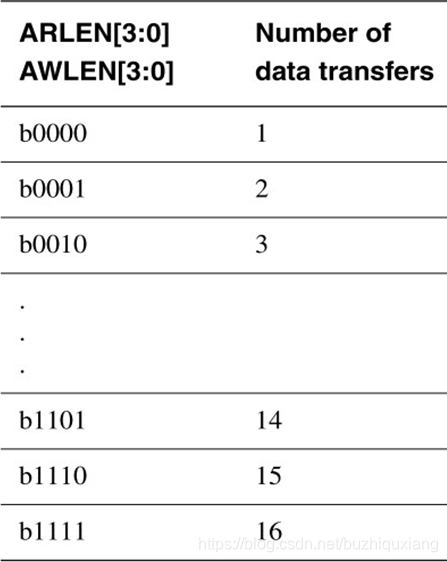

(2)信号AWLEN或者信号ARLEN指定每一次猝发读写所传输的数据个数,范围限制1~16(AXI增量模式为1-256 ->AxLEN[7:0]+1)。

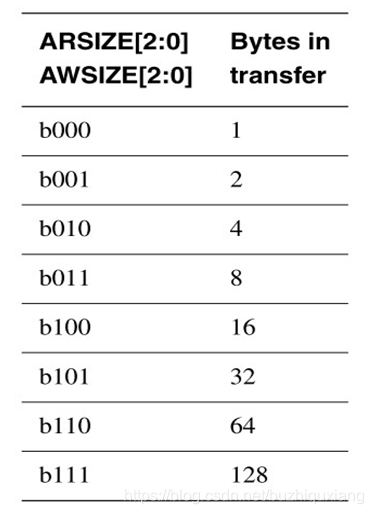

(3)ARSIZE信号或者AWSIZE信号指定每一个时钟节拍所传输的数据的最大位数

(任何传输的SIZE都不能超过数据总线的宽度)

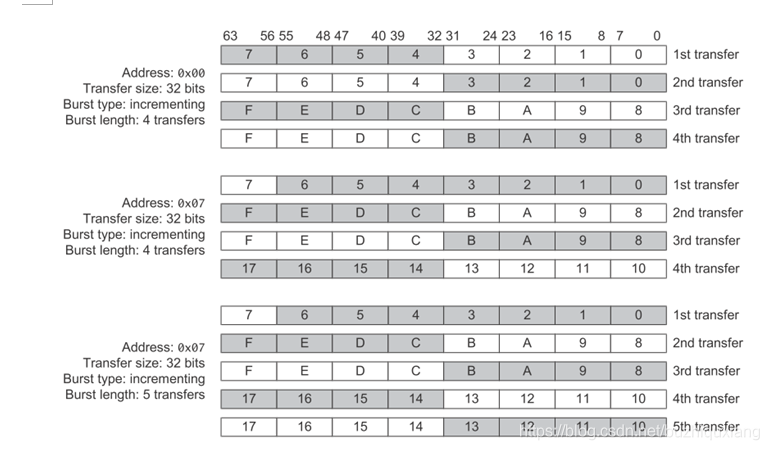

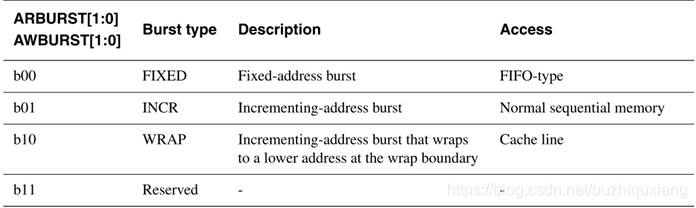

(4)AXI协议定义了三种猝发式读写的类型:

- FIXED:固定猝发模式,每一次传输的地址都不变,这样的猝发式读写时重复对一个相同的位置进行存取,例如FIFO

- INCR:增量式猝发是指每一次读写的地址都比上一次的地址增加一个固定的值

- WRAP:回卷突发模式,突发传输地址可溢出性递增,突发长度仅支持2,4,8,16。地址空间被划分为长度【突发尺寸*突发长度】的块,传输地址不会超出起始地址所在的块,一旦递增超出,则回到该块的起始地址。

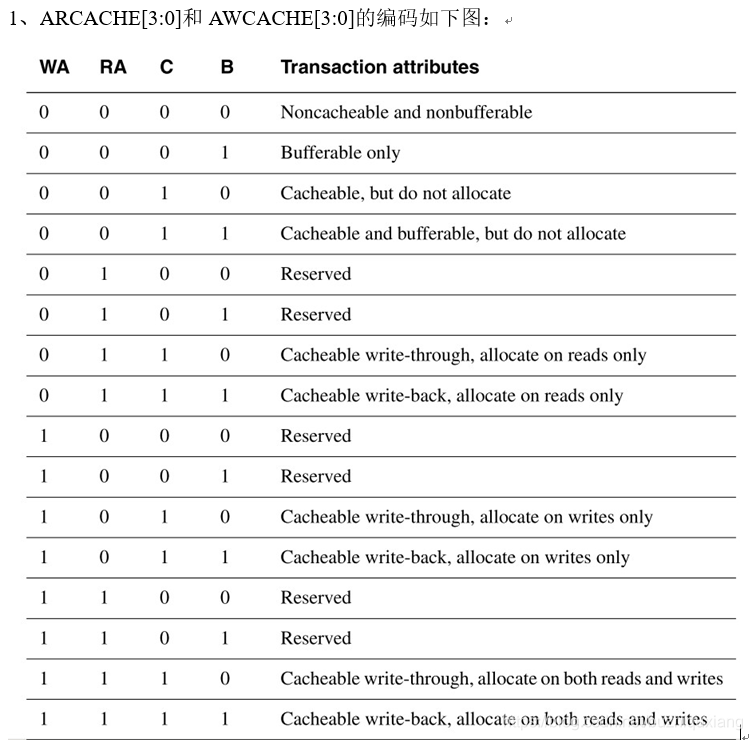

(四)AXI支持系统级的Cache和保护单元

(五)AXI读写通道的四个slave响应

对于读通道,读响应与读数据一起发送给主机;而对于写通道,写响应通过写响应通道传送。

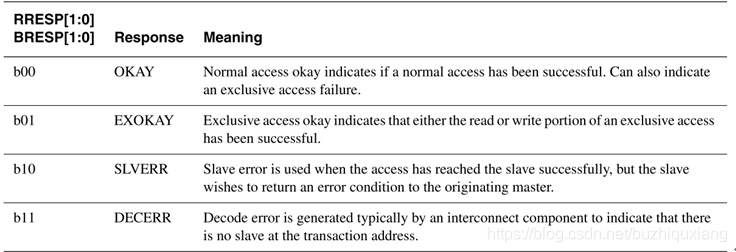

AXI协议的响应类型有:

OKAY(正常存取成功)、EXOKAY(独占式存取)、SLAVERR(slave 错误)、DECERR(译码错误)(通过信号RRESP[1:0]和BRESP[1:0]来编码响应信号)

(6)AXI协议不对齐握手传输

1、AXI协议允许主机使用低阶地址行去标示一个不对齐的起始地址在突发读写中。低阶地址行的信息必须包含byte lane strobes信息。

下面以例子表示数据以对齐或者不对齐的地址为起始地址,分别在32位和64位数据总线上面传输的情况

(1)32bits数据总线 (暗色表示没有传输的数据)

(2)64bits数据总线