inital语句和always语句都是过程结构语句。

initial语句

inital语句只在模块中执行一次。可以理解为初始化,常用于产生仿真测试信号(激励信号)和测试文件,或者用于存储器赋初值。

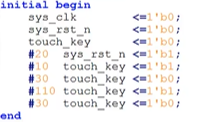

如下图,执行后sys_clk变量被赋值为1位2进制的0;sys_rst_n也被赋值为1位2进制的0

代码块:

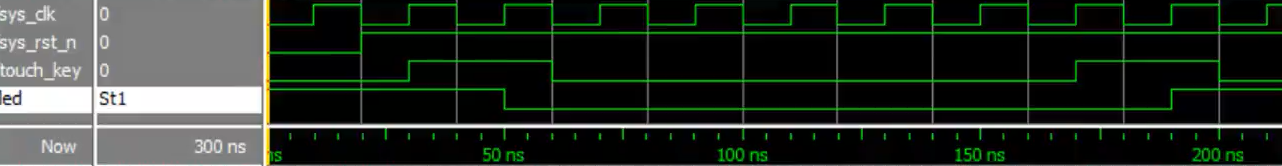

仿真:

always语句

always语句是一直重复执行的,可以理解为循环,类试C语言的while,满足条件时不断重复进行。但是只有和一定的时间控制结合在一起才有用。

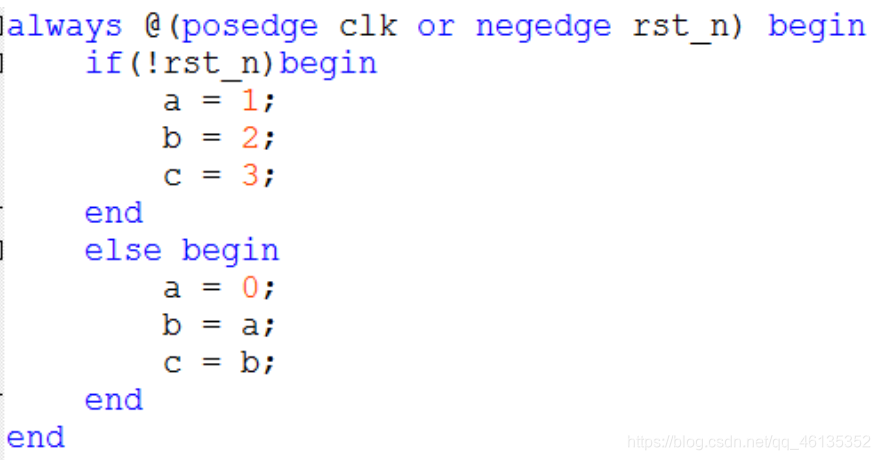

如下图,当满足always后的条件后就会不断执行begin到最后一个end之间的语句

代码块:

always的时间控制可以是边沿触发,也可以是电平触发;可以是单个信号也可以是多个信号,不过多个信号间要用关键字or连接。

边沿触发的always快常常描述时序逻辑行为。由关键词or连接的多个事件名或者信号名组成的列表成为“敏感列表”

always @ (a or b or c or d or e or f or g or h)begin

m1 = a ? b : c

m2 = f ? (d + e) : (g + h)

end

当输入变量有很多的时候,写敏感列表就很繁琐并且容易出错。我们可以用@(*)来代表所有的输入变量,这代表对后面语句块中的输入变量都是敏感的。

always @ (*)begin

m1 = a ? b : c

m2 = f ? (d + e) : (g + h)

end