1、概述

AXI协议是ARM制定的高速接口协议,支持在主从设备间提供高性能、高频率的系统通信。并且在XILINX VIVADO中绝大部分的IP CORE都支持AXI接口,掌握AXI协议意味着你可以很方便的使用赛灵思的各类IP CORE。

1.1、分类

AXI4.0总线主要有以下三类分别适用于不同场景:

- AXI4.0 FULL:面向高性能地址映射,支持突发事件读写,也就是写一次地址,可以传输高达256次数据,数据速率较AXI4.0_LITE高,常用于DDR数据读写。

- AXI4.0_LITE:AXI4.0简化版,轻量级地址映射单次传输接口。

- AXI4.0_STREAM:面向高速数据流数据传输,只传输数据,不含地址。

1.2、特征

AXI4.0 FULL特征如下:

- 独立的地址和数据总线。

- 独立的读写通道。

- 支持不对齐数据传输,使用字节选通。

- 使用基于突发的数据的数据传输。

2、AXI4.0 FULL信号描述

2.1、写数据通道

如下图,写数据通道由三个部分组成。

- 写地址通道;

- 写数据通道;

- 写响应;

信号描述(M端)如下表所示:

2.2、读数据通道

如下图,读数据通道由两个部分组成:

1.读地址通道;

2.读数据通道;

信号描述(M端)如下表所示:

3、读写过程

3.1、握手过程

AXI4.0通信前首先要进行握手建立连接,所有5个通道(写地址、写数据、写响应、读地址、读数据)都是使用相同的握手过程,即源端产生VALID信号表示数据、控制、地址有效,终端产生READY信号表示准备好可以接受这些信号。支持三种握手过程,如下图,都是当VALID和READY同时有效时才能进行数据传输。

1、VALID先于READY

2、READY先于VALID

2、READY和VALID同时有效

3.2、通道要求

1、写地址通道:主端只有在驱动有效的地址和控制后才能拉高AWVALID信号。

2、写数据通道:主端只有在驱动有效的数据和控制后才能拉高WVALID信号。

3、写响应通道:从端只有在驱动有效写响应后才能拉高BVALID信号。

4、读地址通道:主端只有在驱动有效的地址和控制后才能拉高ARVALID信号。

5、读数据通道:从端只有在驱动有效的数据和控制后才能拉高RVALID信号。

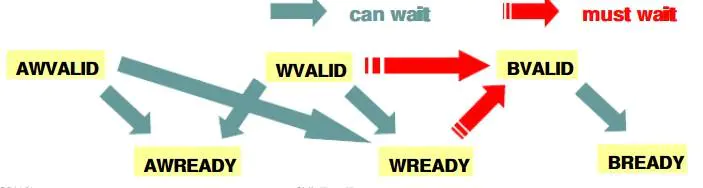

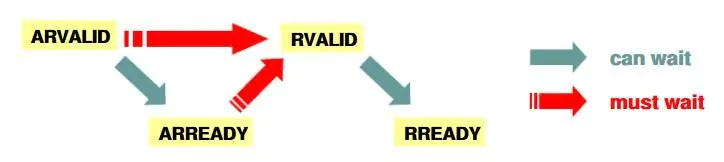

3.3、通道间关系

1、写地址->写数据->写响应

写地址:主机必须不能等待从机产生AWREADY信号再产生AEVALID信号,从机可以等待AWVALID信号有效后再产生AWREADY信号,因此主机首先产生AWVALID信号,从机检测到有效AWVALID后将AWREADY拉高,并保持一个突发周期,主机检测到AWREADY拉高后将AWVALID拉低,整个过程中当AWVALID和AWREADY同时为高时地址和控制信息被从机接收。

写数据:主机必须不能等待从机产生WREADY信号再产生AEVALID信号,从机可以等待WVALID信号有效后再产生WREADY信号,因此一般主机首先产生WVALID信号,从机检测到有效WVALID后将WREADY拉高,并保持一个突发周期,两者同时为高时数据得以传输,当传输最后一个数据时将WLAST拉高,当数据传输完成后将WLAST和WVALID拉低。

写响应:BREADY可以一直拉高,也可以在AWREADY拉高后保持拉高,当从机检测到WLAST信号后将BVALID拉高,主机检测到有效BVALID后将BREADY拉高。

2、读地址->读数据

读地址:主机可以首先产生ARVALID,再等待ARREADY信号,也可以等待ARREADY信号后再产生ARVALID,一般主机可以首先产生ARVALID信号,从机检测到有效ARVALID信号在产生ARREADY信号,当主机检测到ARREADY信号后再将ARVALID拉低,当两者同时为高时地址和控制信号得以传输。

读数据:主机收到RVALID信号后,将RREADY拉高,读出数据,当读取最后一个数据时将RLAST拉高,

4、参数理解

如下图,每个transfer数据宽度WDATA 32 bit,每次突发发送4个transfer,即AWLEN=4-1,每个transfer有四个字节,即AWSIZE='b010,突发类型为增量型,AWBURST='b01,地址为字节地址,初始地址AWADDR为第一个transfer第一个字节地址,每传输一个字节数据,地址加一,下N个transfer的地址NEXT ADDR_N=AWADDR+(N-1)*2^AWSIZE。

AXI支持未对齐transfer(灰色表示未传输数据),可以通过数据选通信号WSTRB信号来指示未对齐地址。

原理同上。

5、BRAM IP CORE

如图调用AXI4接口的数据32位深度1024 BRAM IP,burstsize:2即 4 Byte,burstlen :7 即突发长度为8 ,burst type:incr。

写事务:测试代码是循环写1-8的8个突发数据,地址增量是(N-1)*2^AWSIZE

读事务: