AXI总线和接口

AXI(Advanced eXtensible Interface)总线是AMBA总线架构中,最新并且性能最好的一个总线标准。AXI的设计目标是可以在高时钟频率下运行,并在延滞时间长的状况下仍可达成高数据吞吐率。AXI总线将读/写请求与读/写结果相互分离、将数据写入和数据读出的信号相分离,可以同时进行写入和读出动作,从而最大限度地提高总线的数据吞吐率。

由若干master设备和slave设备通过一些形式的interconnect组成的典型的系统如下图所示,AXI总线即可作为其中的Interface,实现数据通信。

AXI4、AXI4-Lite、AXI4-Stream

ref

https://blog.csdn.net/meng1506789/article/details/111565579

https://www.cnblogs.com/mikewolf2002/p/10322532.html

2 HLS 使用

Vivado HLS支持的AXI4接口包括AXI4- stream (axis)和AXI4- lite(s_axilite)和AXI4 master (m_axi)接口

AXI4-Stream接口:只指定输入参数或输出参数,而不指定输入/输出参数。

AXI4-Lite接口:指定除数组以外的任何类型的参数。你可以在同一个AXI4-Lite接口中添加多个参数。

AXI4-master接口:仅在数组和指针(以及c++中的引用)上指定。你可以将多个参数分组到同一个AXI4接口中。

2.1 AXI4-Stream Interface

AXI4-Stream接口可以应用于任何输入参数和任何数组或指针输出参数。

2.2 AXI4-Lite Interface

使用AXI4-Lite接口来允许由CPU或微控制器控制设计。使用Vivado HLS AXI4-Lite接口,你可以:

1、将多个端口分组到同一个AXI4-Lite接口中。

2、输出C驱动程序文件,以便与运行在处理器上的代码一起使用。

Note:它提供了一组C应用程序编程接口(API)函数,它允许您从软件轻松地控制硬件。这在将设计导出到IP目录时非常有用。

Xilinx建议在AXI4-Lite接口中包含与返回端口相关联的块级I/O协议。

在一个AXI4-Lite接口中,Vivado HLS为块级I/O协议信号和中断控制保留0x0000到0x000C的地址。

HLS会自动给各个使用axilite接口的port分配地址,会在驱动文件里提供地址。

如果想自己显式的指明地址,可以使用offset选项。如上图。注意:hls会保留0x0000 到0x000C的地址给block-level I/O protocol signals and interrupt controls。

综合之后的模块,都会产生一个中断端口。当函数返回的时候,会产生一个中断信号。也可以使用block-level protocols的信号:ap_done(函数完成所有操作), ap_ready(模块准备好等待新的输入)。 这两个信号都可以触发中断。

C Driver Files

AXI4-Lite slave interface综合完成之后,会自动生成驱动文件。C 驱动文件提供了所有通过该AXI4-Lite slave interface 控制模块的操作。驱动包括standalone模式和linux模式。

P116对生成的驱动文件进行了详细的解释。

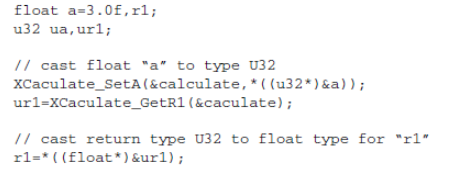

注意生成的驱动文件使用的参数都是U32,使用的时候要注意一下类型转换,以下为类型转换示例:

控制硬件

AXI4-master Interface

对于单个数据传输,Vivado HLS读取或写入每个地址的单个数据元素。下面的示例显示了单个读和单个写操作。在本例中,Vivado HLS在AXI接口上生成一个地址来读取单个数据值,并生成一个地址来写入单个数据值。接口为每个地址传输一个数据值。

在突发模式传输中,Vivado HLS使用一个基址,后跟多个顺序数据样本来读取或写入数据,这使得这种模式能够实现更高的数据吞吐量。当使用C memcpy函数或流水线for循环时,可以使用突发操作模式。

在突发模式中使用for循环,要注意

1、使用 pipeline

2、按递增顺序访问地址

3、不要在条件语句中放置访问

4、对于嵌套循环,不要扁平循环,因为这将抑制突发操作

5、在for循环中只允许一次读和一次写,除非端口被绑定在不同的AXI端口中(bundle)

另外,如果使用slave选项并且使用了几个AXI4-Lite接口,则必须确保将AXI主端口偏移寄存器绑定到正确的AXI4-Lite接口中。在下面的示例中,端口a被实现为一个AXI主接口,带有一个名为AXI_Lite_1和AXI_Lite_2的偏移量和AXI4-Lite接口:

信号

写地址通道,写数据通道和写响应通道

读地址通道的信号:S_AXI_ARADDR,S_AXI_ARPROT,S_AXI_ARVALID,S_AXI_ARREADY;

读数据通道的信号:S_AXI_RDATA,S_AXI_RRESP,S_AXI_RVALID,S_AXI_RREADY;

写地址通道的信号:S_AXI_AWADDR,S_AXI_AWPROT,S_AXI_AWVALID,S_AXI_AWREADY;

写数据通道的信号:S_AXI_WDATA,S_AXI_WSTRB,S_AXI_WVALID,S_AXI_WREADY;

写响应通道的信号:S_AXI_BRESP,S_AXI_BVALID,S_AXI_BREADY。

AXI接口的总线宽度:

C_S_AXI_ADDR_WIDTH : S_AXI数据总线的宽度

C_S_AXI_ADDR_WIDTH : S_AXI 地址总线的宽度

AXI接口的信号详细说明:

S_AXI_ACLK : in std_logic;

总线的输入时钟信号

S_AXI_ARESETN : in std_logic;

全局性的复位信号,这个信号低电平有效

S_AXI_AWADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

写地址通道(由主设备设置发送到从设备)

S_AXI_AWPROT : in std_logic_vector(2 downto 0);

写通道保护类型,此信号表示事务的特权和安全级别,以及事务是数据访问还是指令访问。

S_AXI_AWVALID : in std_logic;

写地址有效,此信号表示主设备正在发送有效的写入地址和控制信息。

S_AXI_AWREADY : out std_logic;

写地址就绪。这个信号表明,从设备将接受地址和相关的控制信号。

S_AXI_WDATA : in std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

写数据(由主设备设置传送到从设备)

S_AXI_WSTRB : in std_logic_vector((C_S_AXI_DATA_WIDTH/8)-1 downto 0);

写数据选通,这个信号表明写数据总线上哪个字节通道存着有效的数据。写数据总线上每八个位对应一个写选通位

S_AXI_WVALID : in std_logic;

写有效,这个信号表明有效的写数据和写选通可用

S_AXI_WREADY : out std_logic;

写准备,这个信号表明从设备可以获取写数据

S_AXI_BRESP : out std_logic_vector(1 downto 0);

写响应,这个信号表明写事务的完成状态

S_AXI_BVALID : out std_logic;

写响应有效。此信号表示信道正在发出有效的写响应。

S_AXI_BREADY : in std_logic;

响应准备,这个信号表明主设备可以接受写响应

S_AXI_ARADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

读地址(由主设备设置传送到从设备)

S_AXI_ARPROT : in std_logic_vector(2 downto 0);

读通道保护类型,此信号表示事务的特权和安全级别,以及事务是数据访问还是指令访问。

S_AXI_ARVALID : in std_logic;

读地址有效,此信号表明读地址通道正在发送有效的读地址和控制信息

S_AXI_ARREADY : out std_logic;

读地址准备,这个信号表明从设备已经准备接受地址和相关的控制信号

S_AXI_RDATA : out std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

读数据(由从设备设置)

S_AXI_RRESP : out std_logic_vector(1 downto 0);

读响应,此信号表明读数据传输的完成状态

S_AXI_RVALID : out std_logic;

读有效,此信号表明读数据通道正在传输需要的读数据

S_AXI_RREADY : in std_logic

读准备,此信号表明主设备可以接受读数据和响应信息

2、AXI 总线通道握手信号之间的依赖性

AXI总共有5个通道,每个通道都有一对valid & ready信号,发送方通过valid信号来指示什么时候数据和控制信息有效,接收方通过ready来指示可以接受数据和控制信息,传输的信息发生在vaild和ready同时为高电平的情况下。每个通道之间可以独立握手,相互之间关系灵活。读数据必须跟在与其数据相关联的地址之后,写响应必须在于其相关联的写事务之后出现。

ref

https://blog.csdn.net/crazyeden/article/details/86594027?utm_medium=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-2.control&depth_1-utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-2.control