实验目的:

利用Quartus II原理图输入方法设计简单组合电路,通过一个8位全加器的设计掌握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

实验原理:

一个8位全加器可以由2个4位全加器构成,加法器间的进位可以用串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

8位加法器的EDA流程:

1、新建工程

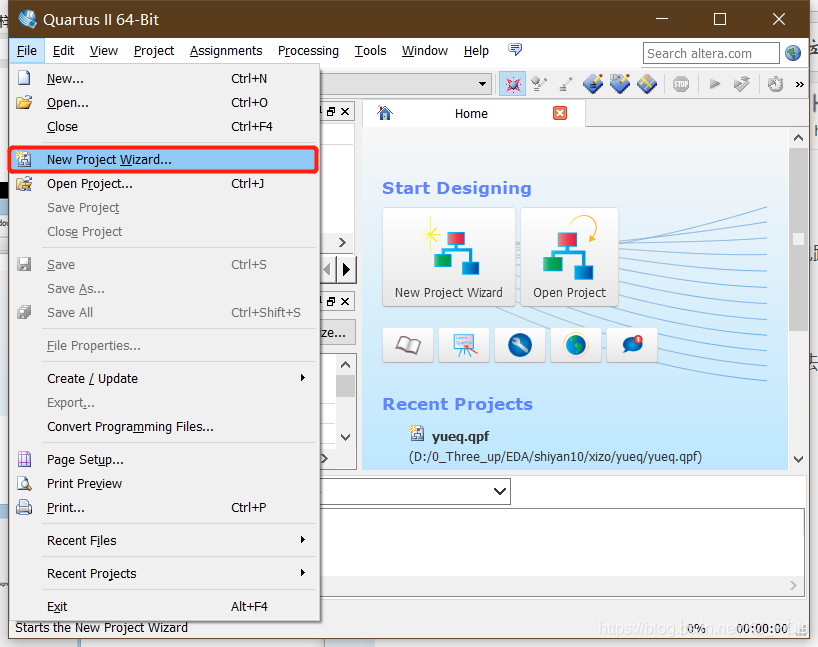

(1)点击打开Quartus II 13.1

(2)打开新建工程向导

(3)点NEXT

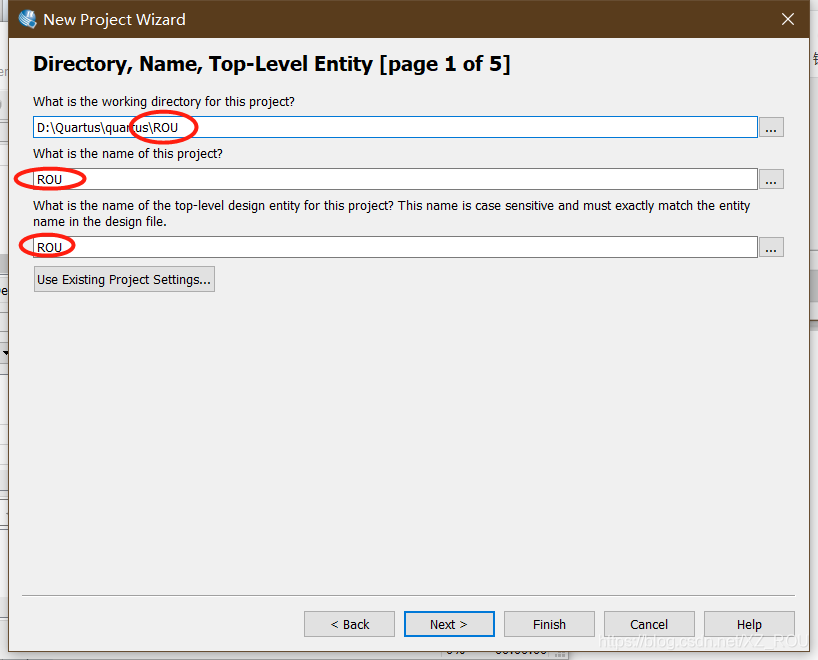

(4)选择合适的路径和工程名,不能使用任何中文,命名要以英文字母开头。

(5)点NEXT。

(6)选择器件如下图所示,特别注意框里面的内容,器件选择错误无法进行后续实验。实验室的开发系统,目标芯片的类型为CycloneV;型号为5CSEMA5F31C6。【不同学校,可能用的芯片不太一样,根据实验室芯片进行选择】

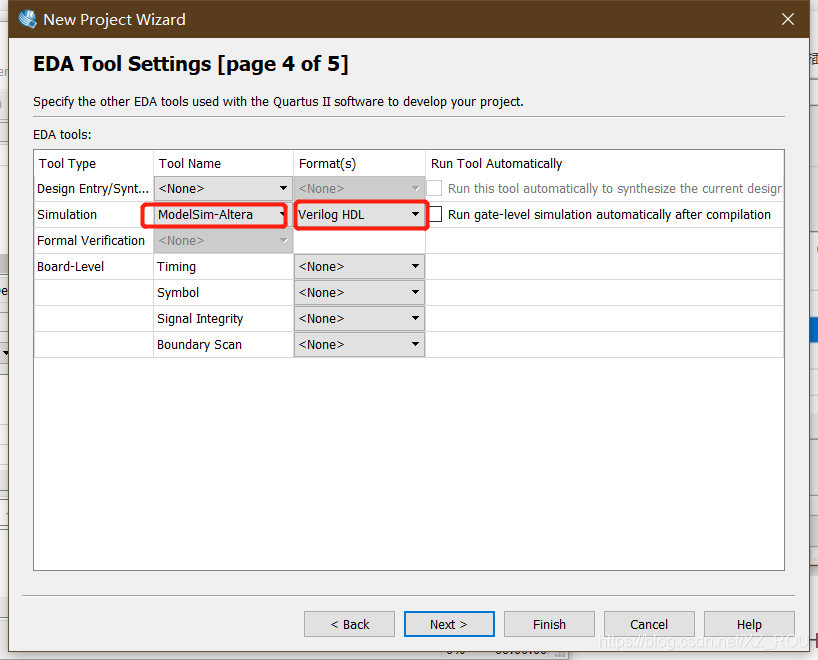

(7)EDA工具设置,每一次实验Simulation选择None。之后的实验选择ModelSim-Altera,Verilog HDL

(8)在生成的summary页面再次检查器件是否选择正确。如正确,点finish。

2、输入设计文件

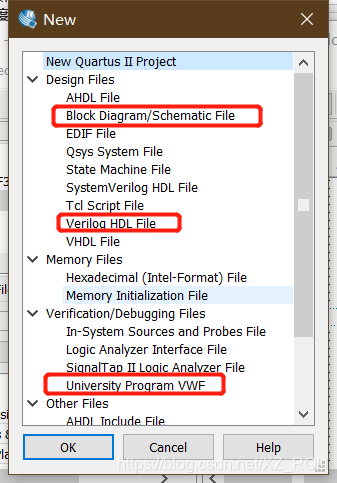

(1)在工程中新建设计文件,第一次实验选择Block Diagram/Schematic File。之后实验选择Verilog HDL File。在做仿真时,选择University Program VWF。

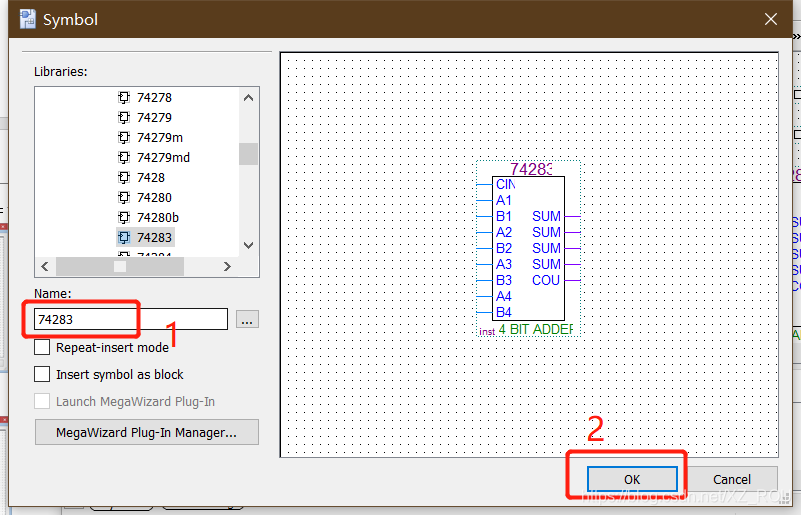

(2)在新建的文件中添加设计内容,第一次实验是添加加法器件74283

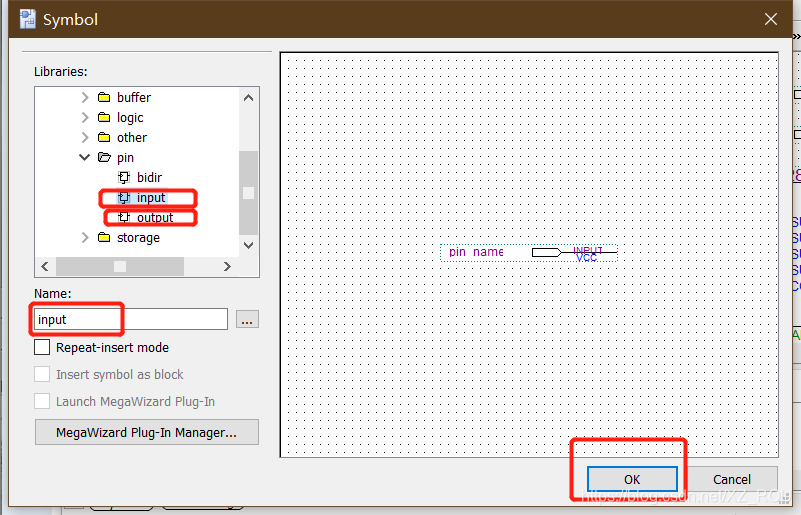

(3)放置好对应的器件后,需要添加输入输出引脚。

或者在下面中选择添加输入or出引脚

![]()

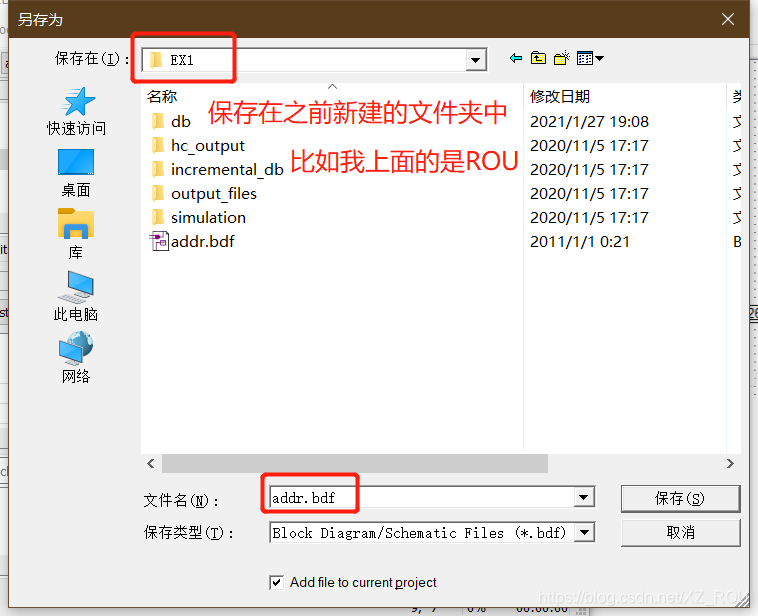

(4)放置完器件和引脚后,完成连线并保存设计文件。

3、编译设计文件

执行QuartusⅡ主窗口中的“Processing” à“Start Compilation”命令,或者在主窗口上直接单击“开始编译”命令按钮,开始对adder8.bdf文件进行编译。编译工具的编译进程可以在如图所示的状态(Status)窗口上看到。编译过程包括分析与综合、适配、编程和时序分析4个环节。

(1)分析与综合(Analysis &Synthesis)

在编译过程中,首先对设计文件进行分析和检查,如检查原理图的信号线有无漏接、信号有无双重来源、文本输入文件中有无语法错误等。如果设计文件存在错误,则报告出错信息并标出错误的位置,供设计者修改。如果设计不存在错误,接着进行综合,通过综合完成设计逻辑到器件资源的技术映射。

注意:一般出现错误,就会在”Processing”页面以红色字体标出,错误的类型和位置一般均会提示。我们修改错误的时候,只用修改第一个错误,修改完成后,需要重新保存,再编译;如果还有错误,请按照上面的修改方法改错。

(2)适配(Fitter)

适配是编译的第二个环节,只有当分析和综合成功完成之后才能进行。在适配过程中,完成设计逻辑在器件中的布局布线、选择适当的内部互连路径、引脚分配、逻辑元件分配等操作。

(3)编程(Assember)

成功完成适配之后,才能进入编程环节。在编程过程中,产生多种形式的器件编程映像文件,如可以通过Masterblaster或Byteblaster电缆将设计逻辑下载到目标芯片中的编程文件。对CPLD来说,是产生熔丝文件,即JEDEC文件(电子器件工程联合会制定的标准格式,简称JED文件);对于FPGA来说,是生产位流数据文件BG(Bit-Stream Generation)。

(4)时序分析(Timing Analyzer)

成功完成适配之后,设计编译还要进入时序分析环节。在时序分析中,计算给定设计与器件上的延时,完成设计分析的时序分析和所有逻辑的性能分析。

在编译结束后,软件自动弹出如图12所示的编译结果概要报告框,报告工程文件编译的相关信息,如下载目标芯片的型号名称、占用目标芯片中逻辑元件le(Logic Elements)的数目、占用芯片的引脚数目等。

4、仿真设计文件

接下来应该测试设计项目的正确性,即逻辑仿真,具体步骤如下:

(1)建立波形文件

执行QUARTUS II主窗口“FILE”菜单的“NEW”命令,选择对话框“Verification/Debugging Files”中的“University Program VWF”,进入QUARTUS II波形编辑方式,弹出新建波形文件编辑窗口界面,如图13所示。

2)输入信号节点

在波形编辑方式下,执行“Edit”菜单下的“Insert Node Or Bus…”命令,或在波形文件编辑窗口的“Name”栏中点击鼠标右键,在弹出的快捷菜单中选择“Insert Node Or Bus…”命令,弹出插入节点或总线(Insert Node Or Bus…)对话框,如图14所示。

在“Insert Node Or Bus…”对话窗口中首先点击“Node Finder…”键,弹出节点发现者(Node Finder)对话框,如图14所示。在“Node Finder”对话框的“Filter”栏目中,选择“Pins:All”项,再点击“List”按钮,这时在窗口左边的“Nodes Found: ”(节点建立)框中将列出该设计项目的全部信号节点。若在仿真中需要观察全部信号的波形,则点击窗口中间的“>>”按钮;若在仿真中只需要观察部分信号的波形,则首先用鼠标左键将信号名点黑选中,然后点击窗口中间的“>”按钮,选中的信号即进入到窗口右边的“Selected Nodes: ”(被选择的节点)框中。如果需要删除“Selected Nodes: ”框中的节点信号,也可以用鼠标将其选中,然后点击窗口中间的“<”按钮。节点信号选择完毕后,点击“OK”按钮。

(3)设置波形参量。图14所示的波形编辑窗中已经调入了8位全加器的所有节点信号,在为编辑窗的8位全加器输入信号a和b设定必要的测试电平之前,首先设定相关的仿真参数。如图16所示,设定仿真时间宽度。Quartus II默认的仿真时间域是1ms,如果需要更长时间观察仿真结果,可执行“Edit”命令菜单中的“ Set End Time…”选项,在弹出的如图16所示的“End Time”设置仿真时间域对话框中,输入适当的仿真时间域(如20mS),后点击“OK”按钮完成设置。

(4) 编辑输入信号

仿真编辑窗口的左侧各种功能选择按钮的主要功能如图17所示,为输入信号编辑测试电平或数据的示意图如图18所示。

![]()

从左到右分别是:【选择工具】,【放大工具】,【强未知】,【0电平】,【1电平】,【高阻】,【弱0】,【弱1】,【反相】,【计数值】,【时钟】,【任意值】,【随机值】,【仿真】。

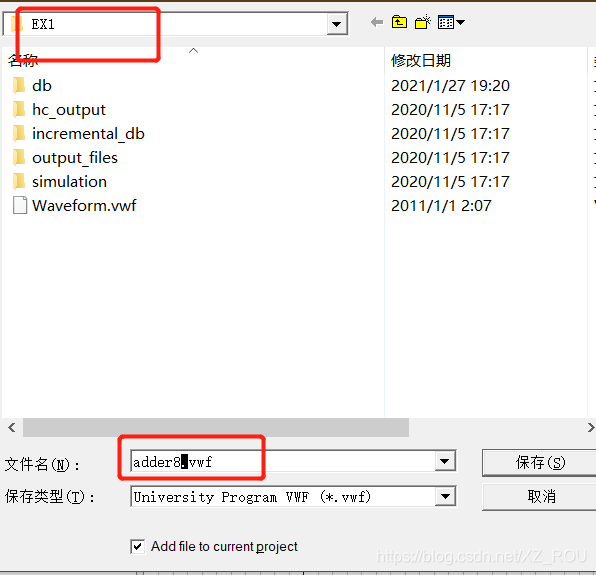

(5)波形文件存盘。选择“FILE”项及其“SAVE AS”选项,按“OK”键即可。存盘窗(图19)中的波形文件名是默认的(这里是adder8.VWF),所以直接存盘即可。

注意:波形文件的名称和原理图文件的名称是一致的,只是后缀不同,切记!

(6)功能仿真和时序仿真

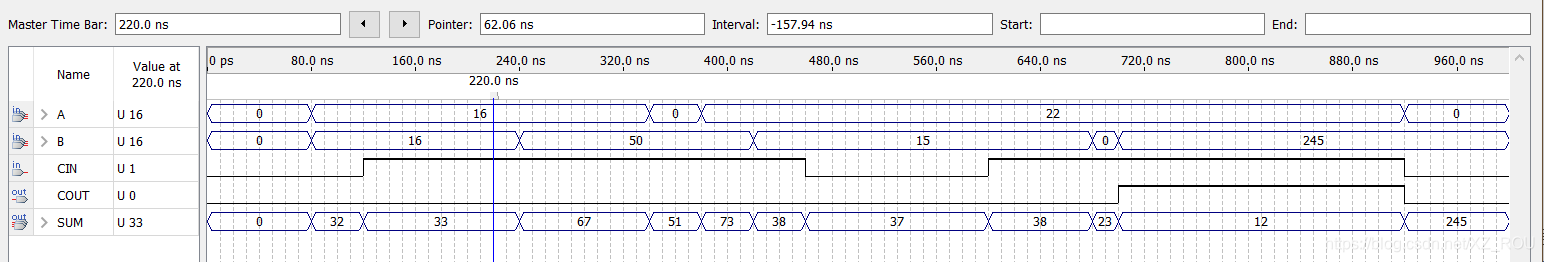

执行“Simulation”中的“Run Functional Simulation” 或者“Run Timing Simulation”命令,对设计电路进行仿真。仿真波形如图20所示。

在图20所示的仿真波形中,8位全加器adder8的执行过程。由图可见,当A、B、cin输入端的数据分别为16、50和1时,输出SUM为67,进位OUT2为0;当A、B、cin输入端的数据分别为22、245和1时,输出SUM为12,进位OUT2为1;【进位为1代表256,想想为什么?】;证明设计是正确的。;;;显然可知,22+245+1=268-256=12+1(1为进位)

5、编程下载设计文件

编程下载是指将设计处理中产生的编程数据文件通过EDA软件放到具体的可编程逻辑器件中去的过程。对CPLD器件来说是将JED文件下载(DOWN LOAD)到CPLD器件中去,对FPGA来说是将位流数据BG文件配置到FPGA中去。

下面介绍KX-CDS5S系列的编程下载过程。

KX-CDS5S系列结构和功能可参考《EDA技术实验讲义》,这里仅以8位全加器的设计实例,介绍其编程下载过程。编程下载的操作过程包括设置实验模式、引脚锁定、编程下载和硬件验证四个部分。

(1)设置实验模式

如果目标器件是Cyclone V,建议选择实验电路模式1,键1、2和键3、4分别负责输入两个加数A和B;且能在数码管1、2和3、4上显示;两个加数的和在数码管5、6显示;发光管D1显示进位输出。

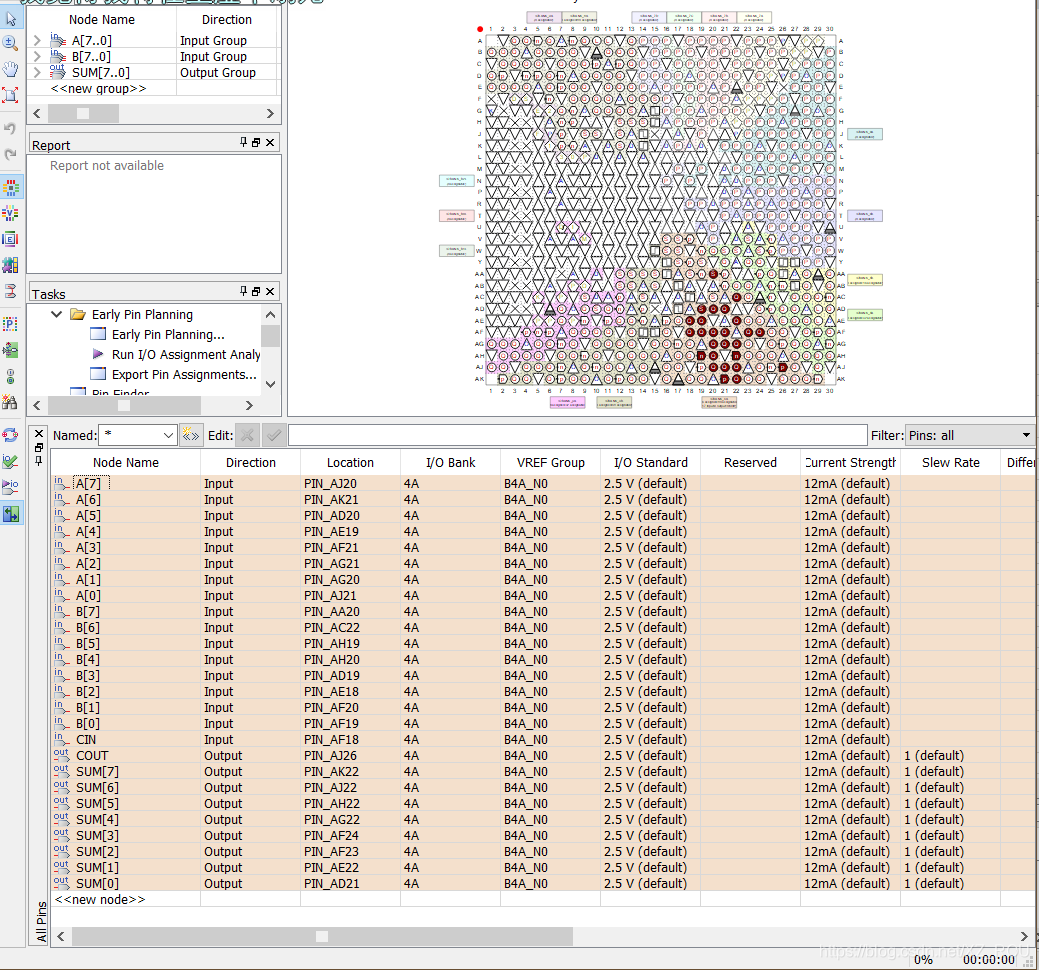

(2)引脚锁定

执行QUARTUSⅡ的“Assignments” “Pins Planner”命令,弹出如图21所示的赋值编辑(Pin Planner)对话框。在对话框的上部是目标芯片的引脚排列俯视图;对话框左边的“Groups” 栏中列出了设计电路的输入/输出群组端口,如8位加法器的A[7..0]、B[7..0]等;对话框的下方是全部引脚的列表(All Pins List)。在列表的“Node Name”栏内列出了设计电路的全部输入/输出端口的名称,如A[7]、A[6]等;列表的“Location”栏是将要锁定的引脚序列。双击“Location”栏下某个端口对应的小方框,弹出一个目标芯片引脚序列的下拉菜单(见图21的中部),根据8位全加器与目标芯片引脚的连接关系,选择该端口的引脚序号(如A[7]选择PIN_AJ20,A[6]选择PIN_AK21等),或者在小方框直接从键盘输入引脚的序号(如AJ20、AK21等)按回车键结束,完成引脚锁定。赋值编辑操作结束后,将引脚锁定文件存盘,并再次通过编译,完成整个设计电路的引脚锁定。

(3)编程下载

在QUARTUSⅡ软件界面上执行“Tools” ,“Programmer”命令或者直接单击“Programmer”命令按钮,弹出如图所示的设置编程方式窗口。

下载设计文件之前需要设定编程方式,在Mode栏中有4种编程模式可以选择:JTAG、Passive Serial、Active Serial和In-Socket,为了直接对FPGA进行配置,在编程窗的编程模式Mode中选JTAG。单击“Hardware Setup”硬件设置对话框。在对话框中单击“Add Hardware”按钮,在弹出的添加硬件对话框中选择“DE-Soc[USB-1]”编程方式。

完成上述操作后,点选Program/ Configure,执行“Processing” à“Start”命令,或者单击设置编程方式窗口左边开始编程按钮“Start”,实现设计电路到目标芯片的编程下载。当Progress显示出100%,表示编程成功。

(4)硬件验证设计电路

选择实验电路模式“NO.1”后,通过按下键1(A[3..0]输入端)、键2(A[7..4]输入端)、键3(B[3..0]输入端)和键4(B[7..4]输入端)按钮,观察7段数码管5、6(SUM[7..0]输出端)和发光管D1,验证8位加法器设计的正确性。【设置不同模式,对应不同的引脚,不同的按键和数码管】

实验总结