原文地址:点击打开链接

ARM体系结构第二篇,主要理解CPU的内存接口,ARM启动过程。

内存映射

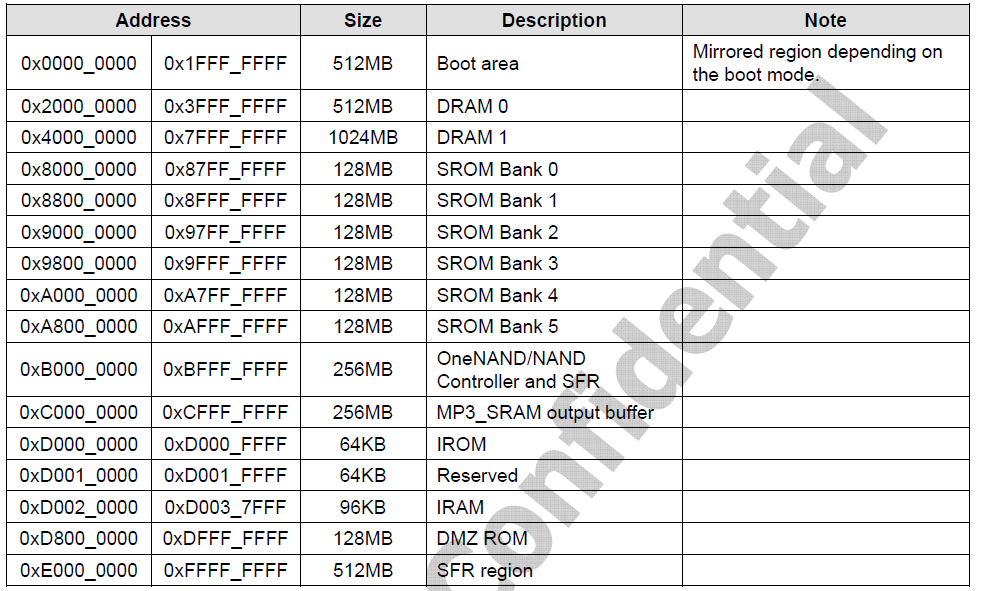

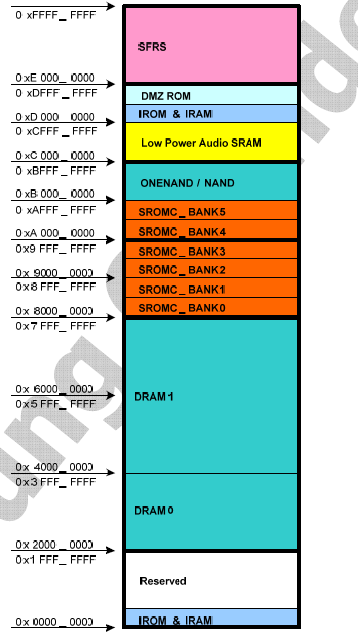

S5PV210属于Cortex-A8架构,有32位地址线和32位数据线,所以CPU的地址空间为4G,但是由于使用了统一编址,外设占用了一部分地址空间,实际供内存使用的地址空间将小于4G,那么对于这个4G的地址空间的分配,就是内存映射,或者说叫地址映射,下图是S5PV210的内存映射分布图,来自于用户手册:

内存分布的描述:

- iROM:internal ROM,内部只读存储器,集成到SOC内部的ROM

- iRAM:internal RAM,内部的随机读写存储器,集成到SOC内部的RAM

- DRAM:动态RAM

- SRAM:静态RAM

- ONENAND/NAND:ONENAND是三星发明的一种NAND Flash的变种,提高了一些存取特性

- SFR:特殊功能寄存器

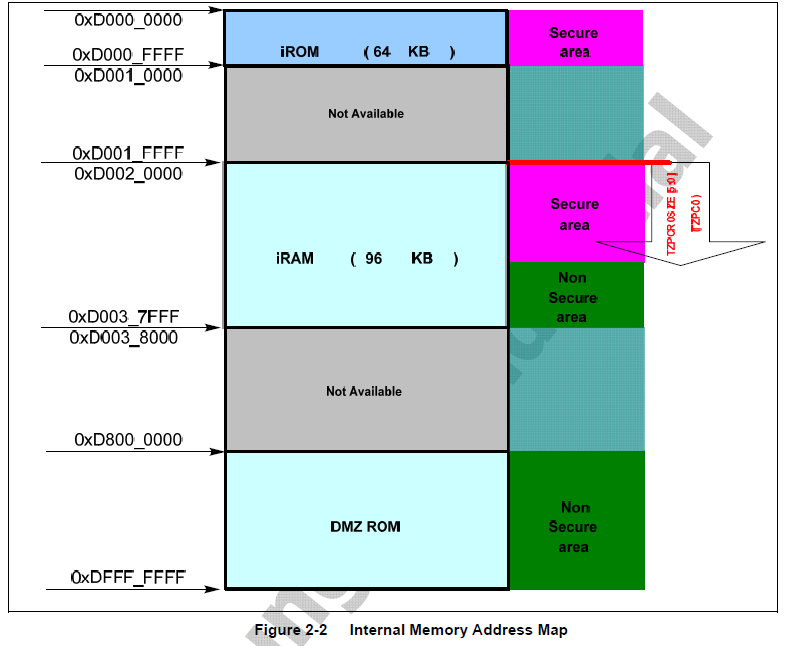

来看一下iROM段的内存分布图:

iROM用于存放代码,iRAM用于存放数据,所以iROM和iRAM之间用Not Available来分割开,也是哈佛结构的体现,我们还可以看到区分的有Secure和Not Secure区域。

外部存储器接口

存储器分类

内存:内部存储器,用于程序运行空间,例如DRAM,SRAM,DDR

外存:用于存储的ROM,例如硬盘,Flash,NAND,iNAND,ONENAND,U盘,SD卡,SSD,光盘等

存储器访问方式

内存需要直接访问,所以通过地址总线和数据总线的方式直接连接来访问,好处是随机访问速度快,但是占用的总线位数多,访问的空间有限,通过用户手册看出,DRAM0和DRAM1加起来,S5PV210的内存地址空间为1.5G,

外存不是通过地址总线来直接连接访问的,而是通过外存接口来连接,不会占用过多的内存地址空间,S5PV210的外存地址空间段为:0xB000_0000~0xBFFF_FFFF的ONENAND/NAND区域,通过外存接口可以扩充数据存储容量,但是速度没有内存快,访问要分几个周期,时序比较复杂

常用外部存储器

- NorFlash:可以总线方式访问,可以接到CPU的地址空间中,以内存的方式来访问,S5PV210就可以将一块NorFlash接到SROMC_BANK区域,实现内存方式的总线访问(网卡其实也可以接到这个SROMC_BANK区域来访问),台式机上的BIOS其实就是一块NorFlash,CPU如果要从NorFlash访问,就需要这样接入SROMC_BANK区域,

- NandFlash:不能通过总线方式访问,需要使用命令接口通过时序来访问,iROM区域就是用于NAND Flash来启动的,分为SLC和MLC两种工艺

- SLC:容量不大,价格高,时序简单,访问简单,稳定性高

- MLC:容量可以做很大,价格低,容易出现坏块和位翻转,需要做ECC校验,访问比较复杂

- eMMC/iNand/moviNand:同属于eMMC,iNAND是SanDisk出产的eMMC,moviNand是三星出产的eMMC

- oneNand:三星出的Nand标准

- SD/TF/MMC卡:同属于SD卡系列

- eSSD:属于SSD固态硬盘的嵌入式MLC的NandFlash

- SATA/IDE/SCSI硬盘:机械访问,速度慢

S5PV210启动

内存

- SRAM:静态内存,容量小,价格高,不需要软件初始化,直接上电就可以使用

- DRAM:容量大,价格低,就是我们平常见的DDR,上电后不能直接使用,需要软件初始化

外存

NorFlash:容量小,价格高,可以通过总线直接访问,上电后可以直接读取,一般用作启动介质

NandFlash:容量大,价格低,不能以总线方式访问,上电之后需要通过软件进行初始化,然后才能使用时序接口进行访问

嵌入式系统启动

嵌入式的启动介质:外接NandFlash + 外接DRAM + 内置SRAM(iRAM)

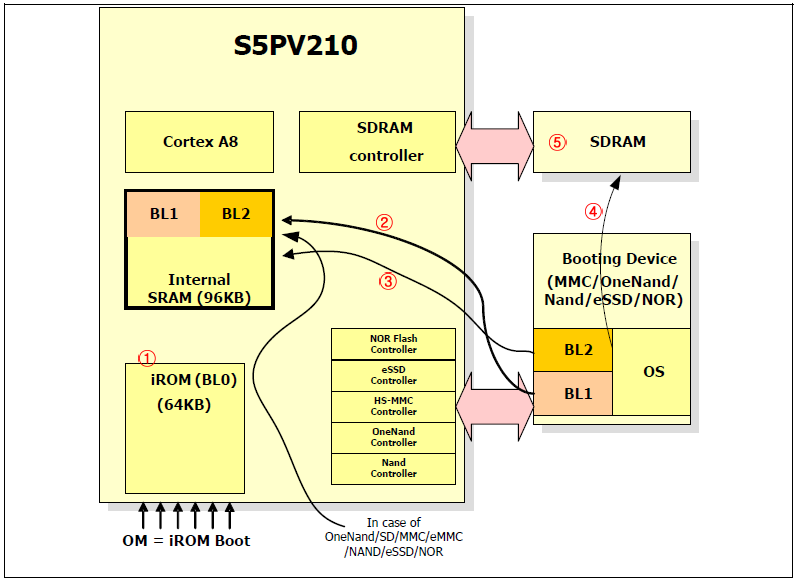

S5PV210:210内置了96KB的iRAM(SRAM),和一块64K的iROM(NorFlash),启动过程如下

- CPU上电后从iROM中读取预先设置的代码(BL0),地址在:0xD000_0000~0xD000_FFFF,这段代码进行

- 初始化指令Cache,堆,栈,块设备复制函数(读取外部启动方式),PLL和系统内部时钟,关看门狗,复制BL1(16K)到iRAM中并检查BL1的校验和,安全启动相关设置,并跳转到BL1去执行

- 这段代码在出厂前设置的,所以暂时还不能初始化NandFlash和DRAM,然后判断我们通过硬件跳线设置的启动模式,从相应的外部存储器读取启动代码(bootloader)到iRAM中,但是一般启动代码都超过了iRAM的96K的容量,三星的解决方案是把启动代码分2部分,依次读取:

- BL1(可配置,最大16K):iRAM运行该段代码,来初始化Flash,然后把BL2读取到iRAM中

- BL2(占用剩余80K的空间):初始化DRAM,将OS读取到DRAM中,从而启动OS

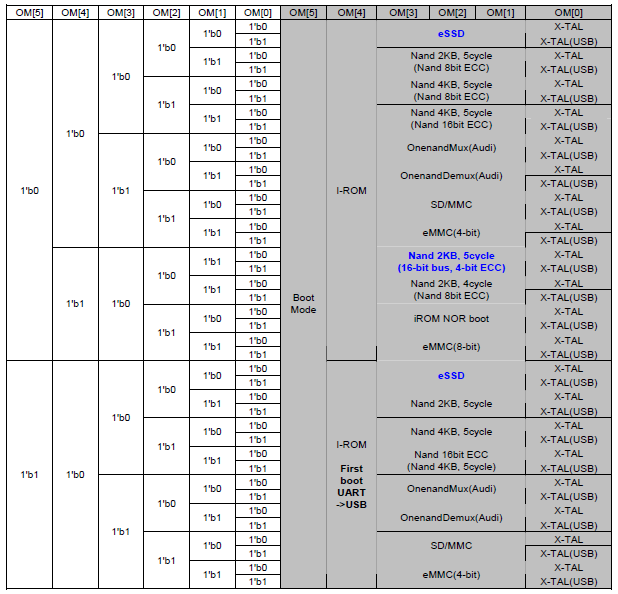

- 启动方式可以根据这个图来看:

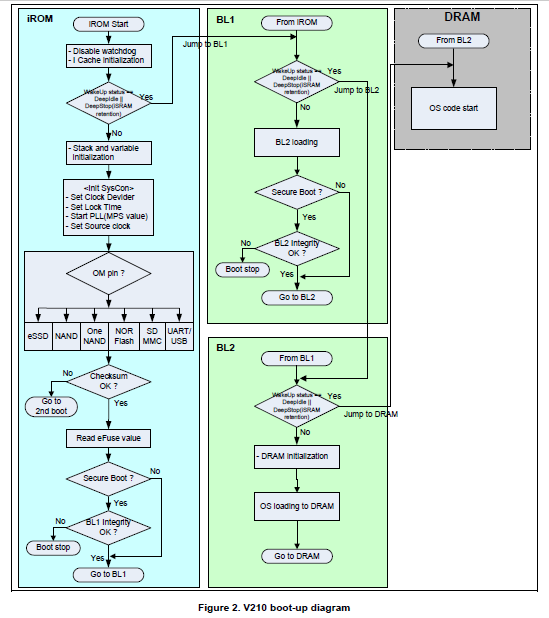

- 启动流程图是这样的:

- WakeUp status:复位状态,深度休眠或者深度停止

- OM pin:拨码开关

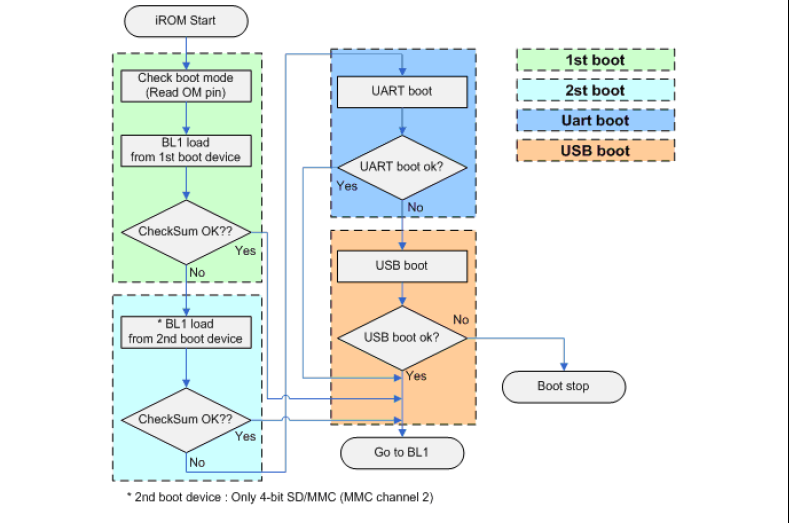

- 如果第一次启动失败,则会进行第二次启动,第二次启动会走SD卡的通道2,如下图所示:

- 如果SD卡通道2启动失败,则会执行UART启动,

- 如果UART启动失败,则会执行USB启动,

- 如果都失败了,则彻底启动失败

开发板启动方式选择

通过OM pin可以设置启动方式,通过配置pin来设置,具体设置如图所示:

对照图片来设置。

ARM架构和工作模式

- ARM采用32位架构

- Byte:8bit

- Halfword:16bit(2Byte)

- Word:32bit(4Byte)

- 大部分ARM提供三种指令集

- ARM指令集(32bit)

- Thumb指令集(16bit)

- Thumb2指令集(16&32bit)

- Jazelle Core还提供了Java ByteCode的支持

- 7中工作模式

- USER:非特权模式,大部分任务执行在这种模式下

- FIQ:快速中断模式,高优先级的中断产生时会进入这种模式

- IRQ:中断模式,普通中断产生时进入这种模式

- SUPERVISOR:复位或者软中断指令被执行时进入这种模式

- ABORT:存取异常时进入这种模式

- UNDEF:执行到未定义指令时进入这种模式

- SYSTEM:系统模式,内核运行在这种模式下,使用和USER模式相同的寄存器

- 除USER是Normal模式之外,其他都是Privilege特权模式

- 除SYSTEM之外其他特权模式都是异常模式

- 可以通过写CPSR寄存器主动切换模式,也可以由CPU自动切换

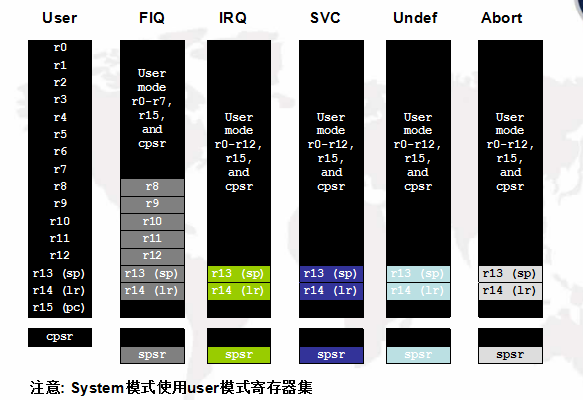

- 各种模式下权限和可访问的寄存器是不一样的

ARM内部通用寄存器

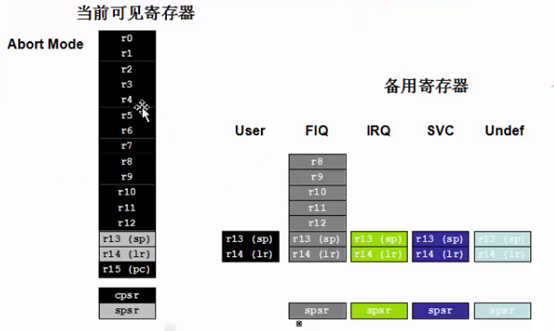

ARM的CPU内部有17个基本通用寄存器,根据不同的工作模式可以定义成37个寄存器,每个寄存器都是32位,相对于其他设备的SFR来说,会更复杂一些,通用型寄存器通过寄存器的名字来访问:

每种模式下最多看到18个寄存器,其他寄存器虽然名字相同,但都属于该模式的专用寄存器,在当前模式看不见。

例如USER模式下的r13(sp)和r14(lr),是不重复的,是用户模式专用的寄存器,这两个寄存器在模式切换的时候是不需要考虑重复问题的,所有模式下的寄存器见下图:

CPSR程序状态寄存器

该寄存器一共32bit

- 0~4是模式位,表示处理器的7中模式之一

- 5是T位,切换处理器状态,0是ARM状态,1是Thumb状态

- 6~7分别表示I,F中断禁止位,I= 1,禁止IRQ,F= 1,禁止FIQ

- 8~23未定义

- 24是J位,处理Jazelle状态,J = 1,支持Jazelle,仅支持ARM 5TE/J架构

- 25~26未定义

- 27是Q位,指示饱和状态,Q = 1,饱和,仅支持ARM 5TE/J架构

- 28~31是V,C,Z,N条件位:

- V = 1:表示ALV运算溢出

- C = 1:表示ALV运算的进位标识位溢出

- Z = 1:表示ALV运算得到了一个0

- N = 1:表示ALV运算得到了一个Negative负结果

PC程序状态寄存器

- 称为程序指针,PC指向哪里,CPU就会执行哪条指令,

- 例如程序跳转时把目标地址放在PC中,

- 整个CPU只有一个PC

ARM异常处理方式

异常

异常是指程序在运行过程中,发生了正常工作之外的流程,异常会打断正在执行的工作,且希望异常处理完成之后回来继续进行原来的工作,中断也是异常的一种,7中工作模式中除了USER和SYSTEM之外的工作模式都是用来处理异常。

异常向量表

- 异常向量表是CPU处理异常的手段,所有CPU都有异常向量表,属于硬件设计范围,

- 当异常发生时,CPU会自动动作,由PC跳向异常向量处(异常处理地址)来处理异常,有时还会伴随一系列辅助动作,

- 异常向量表是硬件想软件提供的处理异常的支持

ARM异常处理机制

- 当异常产生时,ARM Core需要:

- 拷贝CPSR到SPSR_<对应模式>

- 设置适当的CPSR

- 改变处理器状态进入ARM状态

- 改变处理器模式进入相应的异常模式

- 设置中断禁止位禁止响应中断,以防异常处理被打断

- 保存返回地址到LR_<对应模式>

- 设置PC为相应的异常向量

- 当异常返回时,ARM Core需要

- 从SPSR_<对应模式>恢复CPSR

- 从LR_<对应模式>恢复PC

- 以上操作都在ARM状态进行

- 异常处理有一些是CPU自动动作,有一些是需要程序员手动操作的,CPU设计时提供的异常向量表,一般属于一级向量表,有的CPU为了支持多个中断,还会提供二级向量表,处理的方式和一级向量表类似。