文章目录

1.绪论

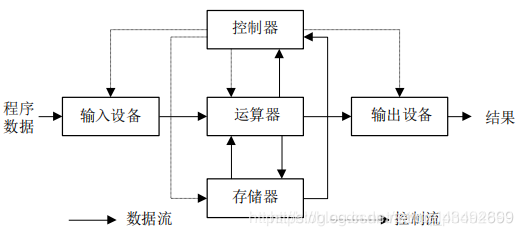

1.1.冯·诺依曼计算机

- 二进制:信息均是用二进制编码来表示的。

- 程序控制:在冯·诺依曼计算机工作过程中,总是一条指令接一条指令地执行,执行指令

会产生控制流,在控制流的驱动下完成指令的功能。在此过程中,数据(流)则是

被动地调用。 - 程序和数据存储在一起:当时的计算机由运算器、控制器、存储器、输入设备和输出设备五大部分构成。运算器用以实现算术运算和逻辑运算;控制器根据指令的功能产生相应的控制信号,控制其他部分的工作以便实现指令的功能;存储器用来存放数据和程序;输入设备可将外部的信息输入到计算机中;

1.2.CPU时间

总指令数目IC=所有指令的和

总指令执行周期数=所有指令 x 对应时间的和

一条指令执行完的平均时钟周期数CPI=总指令执行周期数 ÷ 总指令数目IC

时钟周期=1 ÷ CPU频率

程序执行时间=总指令执行周期数 x 时钟周期

每秒钟执行指令的百万条数MIPS=总指令数目 ÷ (程序执行时间x106)

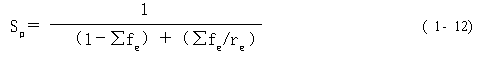

1.3.Amdahl定律

2.计算机中的数据表示

2.1.数据编码

原码:最直观的表示方法,整数原码的表示范围为-(2n-1-1)~(2n-1-1)

而小数原码的表示范围为-(1-2-(n-1))~(1-2-(n-1))

其中,小数原码范围的含义,假如有8位数位,表示的最大小数即为0.1111111,而这个二进制数也可以表示为,1.0000000-0.0000001,而0.0000001即2-(n-1)其中n=8。

补码:在加减运算上最为方便的表示方法,n位补码表示的整数数值范围为-2n-1~+(2n-1-1),

小数数值范围为-1~+(1-2-(n-1)),补码与原码最大的区别在于0是唯一的,同时补码可以将减法运算转化为加法运算,对减数进行求补运算,即可将减法转化为加法。补码在未超过表示范围时,左移代表x2,右移代表/2。

反码:正数的反码,补码都与原码一致,但是负数的反码为原码除符号位全部取反,某负数数值的反码最低位+1即可获得该数值的补码。整数反码的表示范围为-(2n-1-1)~(2n-1-1)

而小数反码的表示范围为-(1-2-(n-1))~(1-2-(n-1))

移码:移码的使用是为了解决补码不能直观判断出真值大小的问题,得出移码的方法即求出补码后将符号位取反。移码的大小即代表了真值的大小。

2.2.浮点数表示

浮点数的表示:F=M x RE

M为尾数,E为阶码,R为基数,基数可取2,4,8,16等。阶码是整数,阶符是阶码的符号位,决定阶码的正负,采用补码表示。尾数是小数,尾符是尾数的符号为,决定正负,采用补码表示。

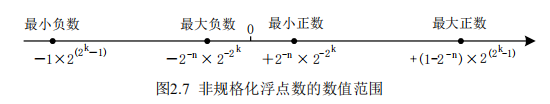

非规格化浮点数的表示范围:

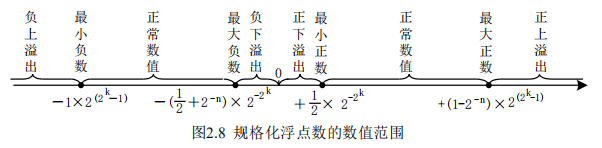

规格化浮点数:尾数M>=0时,规格化尾数必须为M=0.1XXXXX,当M<0,规格化尾数必须为M=1.0XXXXXX,规格化尾数的最小负值为-1,尾数的最大负值为-(1/2+2-n),最小正值为+1/2,最大正值为+(1-2-n)

规格化时,尾数左移一位,阶码减 1,(这种规格化叫做向左规格化,简称左规);尾数右移一位,阶码加 1

(这种规格化叫做向右规格化,简称右规)。

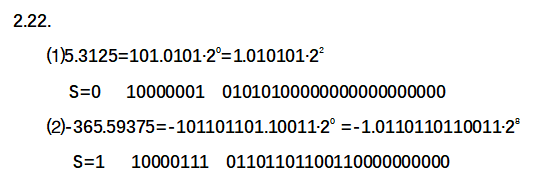

2.3.IEE-754标准

若将某数转化为IEE754标准,首先转化为2进制数,并用浮点数的方式表示。

结果分为三部分,

数符,正数S=0,负数S=1。

阶码,将原数中阶码的数加上127,比如22即为01111111+000000010得到10000001

尾数,原本求得的小数点后的尾数补0补至23位

三部分一共32位即为IEE754标准

2.4.BCD码

分为8421码,2421码,5211码,4311码。其中,对BCD数直接进行加减会得到错误的结果,必须进行校正,比如两8421BCD数相加,结果必须加上06H。

2.5.奇偶校验码

水平奇校验定义为:c⊕x0⊕x1⊕…⊕xn-1 =1

水平偶校验定义为;c⊕x0⊕x1⊕…⊕xn-1 =0

⊕的含义为逐位相加

从上面的描述中可以想到,奇偶校验可以检测出 1 位错误(或奇数位错误,但多于 1 位错的几率很小)。但无法检测出 2 位或偶数位错,也无法识别错误信息的位置。但是,由于奇偶校验原理简单,实现起来非常容易。因此,这种方法得到广泛地应用。

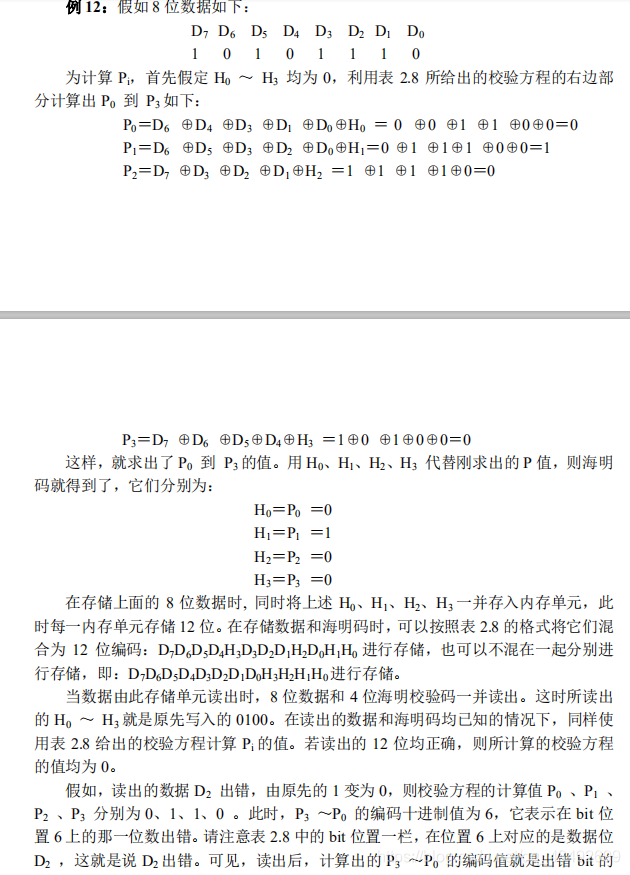

2.6.海明码

海明码即为存储进内存单元的H0,H1,H2,H3,当读取数据时,按原本求海明码的方法再次求一遍,若与存储进的海明码不同,则数据出错,要利用4-16译码器进行纠正。

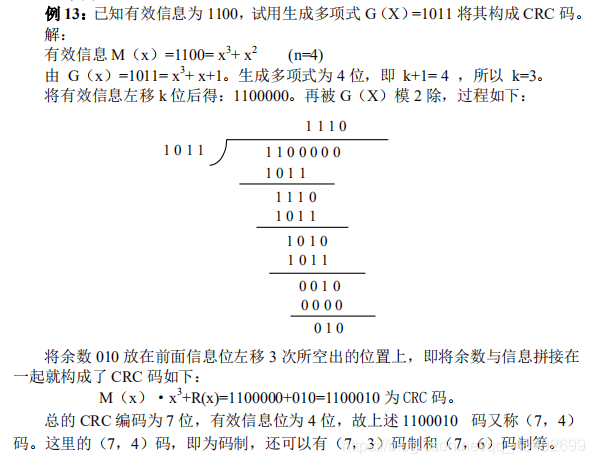

2.7.CRC码

先将有效信息转化成多项式,有1的为x对应幂次,无1的不写出来。其次判断多项式生成的位数为几位,得出k的值(k即为图中x3+x),将有效信息左移k位,然后使用模2除法得出余数,与有效信息拼接得到CRC码。

模 2 减法 按位减,不考虑借位:0-0=0,0-1=1,1-0=1,1-1=0。例如 1101-1011=0110。

模 2 除法 按模 2 减求部分余数,不借位,每求一位商应使部分余数减少一位。

进商的规则是:余数首位为 1 商取 1,余数首位为 0 商取 0。当余数位数小于除数位数时即为最后余数。

3.运算方法与运算器

3.1.加减运算

补码加法: [X+Y]补=[X]补+[Y]补

补码减法:[X-Y]补=[X]补+[-Y]补 =[X]补+[[Y]补]求补

求补运算不等于求补码,求补运算为所有位取反+1,包括符号位。

移码的加减法:结果要对符号位取反,才能得到正确的结果。

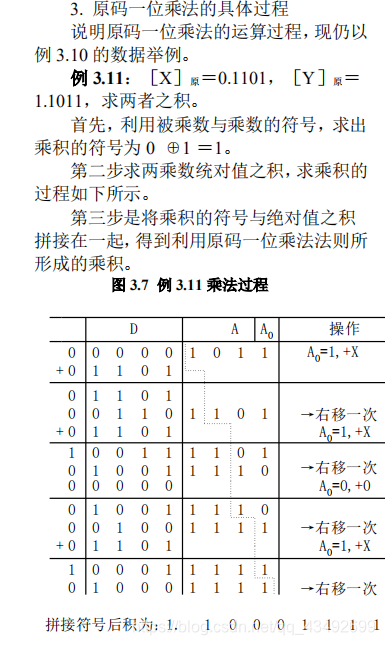

3.2.纯小数乘法

原码一位乘法:

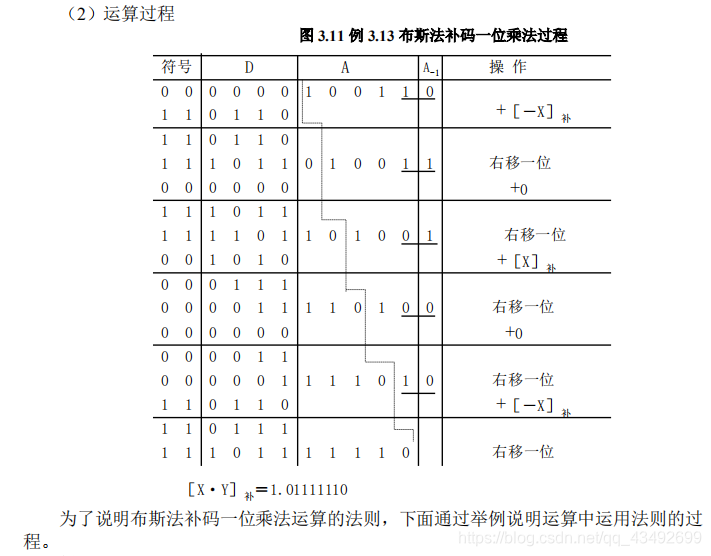

布斯法(补码一位乘法):

3.3.纯小数除法

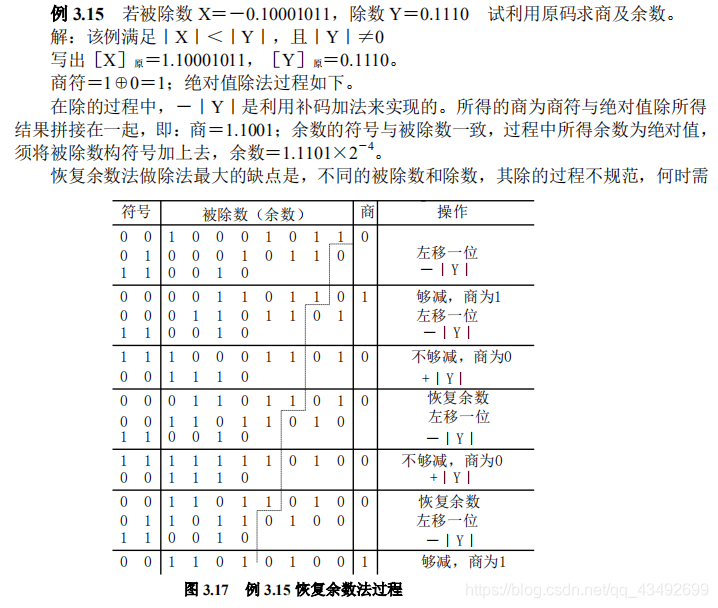

恢复余数法:

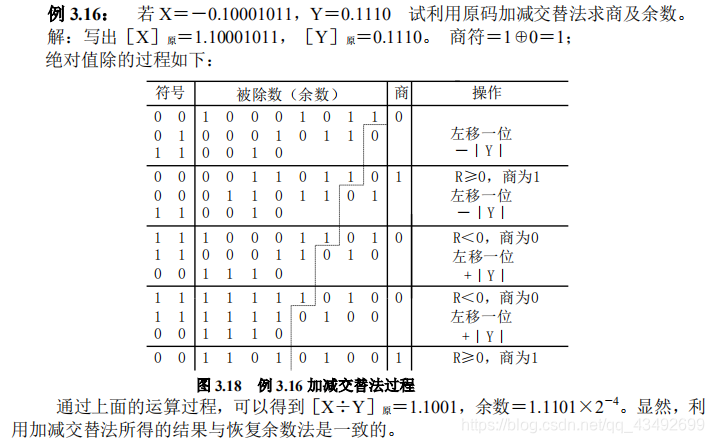

加减交替法:

3.4.浮点数运算实例

例题.两浮点数为:

X=0.110101×2010

Y=-0.101010×2-001

求两数之和及差。

- 对阶

首先将两数的尾数和阶码均转化为补码的形式

﹝X﹞浮=1110 00.110101

﹝Y﹞浮=1111 11.010110

求阶差:﹝△E﹞补=﹝EX﹞补 +﹝-EY﹞补 ﹦1110+0001﹦1111。即 X 的阶码比 Y

的阶码小。

因此,X 尾数右移一次,使两者阶码相同。这时的 X 为:﹝X﹞′浮=1111;00.011011,

采用的是 0 舍 1 入法。

对阶的原则是小阶对大阶,小阶直接加上△E,同时小阶尾数右移△E位,损失的精度采用0舍入1法补齐 - 尾数求和

对阶完成后,两浮点数的尾数直接列竖式相加或者相减,得出计算结果。

相加的结果为11.110001,相减的结果为01.000101。 - 规格化

前面提到过浮点数的规格化问题,即尾数M>=0时,规格化尾数必须为M=0.1XXXXX,当M<0,规格化尾数必须为M=1.0XXXXXX。

从相加的结果可以看到结果为一非规格化尾数。需将尾数左移 2 位,变为 11.000100。

同时,阶码减 2,则阶码变为 1101。

最后,得到两数相加结果为;﹝X+Y﹞浮=1101;11.000100。

同样,从两者相减的结果看到尾数也不是规格化数。此时需右规,将尾数右移一次,

变为 00.100011,采用的是 0 舍 1 入法。同时,阶码需加 1,则阶码为 0000。得到两数相

减结果为;﹝X-Y﹞浮=0000;00.100011。

此处注意,相加的结果11.110001要进行规格化,如果右移是得不到M=1.0XXXXXX的格式的,故只能左移两位,同时,尾数左移了两位,阶码就要减2,如果右移了两位,阶码就要加2

4.指令系统

4.1.指令格式

人们将具有复杂指令系统的计算机称为复杂指令集计算机(CISC)。

复杂指令集计算机的主要特点是:

⑴ 指令系统复杂,指令数目多达200~3000条。

⑵ 指令长度不固定,有更多的指令格式和更多的寻址方式。

⑶ CPU内部的通用寄存器比较少。

⑷ 有更多的可以访问主存的指令。

⑸ 指令种类繁多,但各种指令的使用频度差别很大。

⑹ 不同的指令执行时间相差很大,一般都需要多个时钟周期才能完成。

⑺ 控制器大多采用微程序控制器来实现。

⑻ 难以用优化编译的方法获得高效率的目的代码。

精减指令集计算机(RISC)精减指令集计算机的主要特点罗列如下:

⑴ 只设置使用频度高的一些简单指令,复杂指令的功能由多条简单指令的组合来实现。

⑵ 指令长度固定,指令种类少,寻址方式种类少。

⑶ 访存指令很少,有的RISC只有LDA(读内存)和STA(写内存)两条指令。多数指令的操作在速度快的内部通用寄存器间进行。

⑷ CPU中设置大量的通用寄存器,一般有几十个甚至几百个。

⑸ 控制器用硬件实现,采用组合逻辑控制器。

⑹ 采用流水线技术,大多数指令1个时钟周期即可完成。

⑺ 有利用优化编译程序。

⑻ 可简化硬件设计,降低设计成本。

确实是要将CPU的指令系统精减,只采用最经常使用的指令系统中20%的指令。同时,通过指令的减化可以使CPU的结构更加简单、更加合理,从而提高执行速度。

4.2.寻址方式

- 立即寻址 将操作数直接存在指令之中,MOV AX 0100H

- 寄存器寻址 将操作数存在寄存器之中,指令中存储寄存器 MOV AX BX

- 直接寻址 将操作数地址存在指令之中,由操作数地址访问主存得到操作数 MOV AX [0100H]

- 寄存器间接寻址 将操作数存在主存之中,而操作数的地址存在寄存器之中,指令先访问寄存器得到地址再访问主存得到操作数 MOV AX [BX]

- 寄存器相对寻址 与间接寻址类似,但是较间接寻址增加了一个地址的偏移量 MOV AX,0100H [BX]

- 基址寻址 操作数的地址为指令内的两个地址相加的合 MOV AX ,[BX] [CX]

- 基址变址寻址 与基址寻址类似,但是较基址寻址增加了一个地址的偏移量 MOV AX,0100H [BX] [CX]

4.3.汇编语言

5.中央处理器CPU

5.1.微指令

一.水平型微指令

1.直接表示法

在微指令的控制域字段中,直接表示法就是直接用一个二进制位表示一种微命令。

2.字段译码法(字段编码)

一种性能良好而普遍使用的控制域编码方法是字段译码法,它是不译码法和译码法的结合。它将控制域分为若干字段。若各字段的编码相互独立,则通过各字段独立译码就可以获得计算机系统的全部控制信号,这被称作直接译码方式。若某些字段的编码相互关联,则关联字段要通过两级译码才能获得相关的控制信号,这被称作间接译码方式。

二.垂直型微指令

垂直型微指令的控制域变得非常紧凑、短小,是减小微指令长度的有效设计方法。

垂直型微指令的控制字段一种极端情况是:如果CPU执行机器指令只需50余种微命令,则可用6位二进制编码构成微指令的控制字段。

例题:

- 某微程序控制器采用的微指令字长为 24 位。微命令生成部分由 4 个字段构成,各字段所包括的互斥微命令分别为 5 个、8 个、14 个和3 个。另外控制产生次地址的条件有 3 种。试说明该微控制器最多可用几位来表示次地址?控制存储器 的容量为多少?

互斥微命令所需的最少位数分别是3位,4位,4位,2位,根据二进制表示的最大值,其次,控制产生次地址的条件有3种,则至少需要2位,则最多的空余地址位为24-3-4-4-2-2=9位,控制存储器的容量为29=512位

5.2.微操作流程与微流程

- 微操作流程:

PC→AR

AR→AB,RD,PC+1

DB→DR

DR→IR

AX→S

BX→IB,ADD

ALU→T

T→AX

- 微流程:

① PCout,ARin

② AR→AB,RD,PC+1

③ MD→DB,DRin

④ DRout,IRin

⑤ BXout,ARin

⑥ AR→AB,RD

⑦ MD→DB,DRin

⑧ DRout,Sin

⑨ S→ALU

⑩ AXout→ALU

11.ADD→T,Tin

12.Tout,AXin

T,S为暂存器

IR为指令寄存器

AR,DR分别为单向地址寄存器和双向地址寄存器

不论是微操作流程还是微流程,其大概都可以分为以下几个过程

- 将指令存入指令寄存器IR

- 根据寻址方式,将操作数存入暂存器S

- 根据指令的内容控制ALU进行对应的操作

- 将结果存入相应的寄存器或是主存单元中(WR)