概述

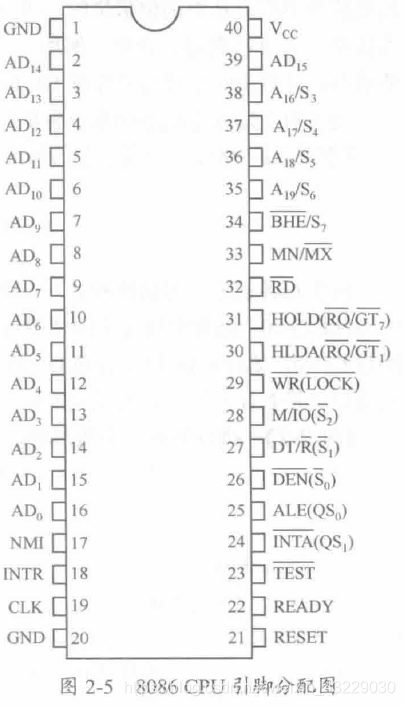

8086 是 16 位 CPU , 采用高性能的 N 沟道、耗尽型负载的硅栅工艺(HMOS) 制造。由于受当时制造工艺的限制,为了解决功能多和引脚少的矛盾,部分引脚采用 分时复用 的方式,构成了 40 条引脚的双列直插式封装。

分时复用: 在同一根传输线上,在不同时间传送不同的信息

这些功能引脚有两种情况:一种是采用了分时复用的地址/数据总线;另一种是根据不同的工作模式定义不同的引脚功能。

引脚介绍

8086 CPU 可以工作在最小模式和最大模式下, 因此有8 条引脚(2 4 〜3 1 ) 在上述两种工作模式中具有不同的功能,括号中所示为最大模式下被重新定义的控制信号。

最小模式: 单处理模式,指系统只有一个8086微处理器,所有的总线控制信号都由8086微处理器直接产生,构成系统所需的总线。控制逻辑部件最少的

最大模式: 系统可以有一个以上的微处理器,除了8086,还可以配置用于数值计算的数值协处理器 8087 和用于 I/O 管理的 I/O 协处理器 8089 。各个处理器发往总线的命令统一送往总线控制器,由它仲裁后发出。

是什么模式由引脚 M N / M X ‾ MN / \overline{MX} MN/MX 决定

引脚介绍1:打头阵

M N / M X ‾ MN / \overline{MX} MN/MX (Minimum / Maximum mode control,模式控制信号,输入)

M N / M X ‾ MN / \overline{MX} MN/MX 为高电平,表示 CPU 工作在最小模式系统中: M N / M X ‾ MN / \overline{MX} MN/MX 为低电平,表示 CPU 工作在最大模式系统中。

引脚介绍2:两种模式共享的引脚信号

两种模式共享的引脚信号

G N D 、 V C C GND 、 VCC GND、VCC (输入)

GND为接地端,VCC为电源端,采用的电源为 5V±10%

A D 15 〜 A D 0 AD_{15}〜AD_0 AD15〜AD0 ( Address Data Bus,地址/数据复用线,双向、三态 )

分时复用的地址数据总线。传送地址时以三态输出,传送数据时可以以双向三态输入/输出。

A 19 / S 6 〜 A 16 / S 3 A19/S6〜A16/S3 A19/S6〜A16/S3 (Address/Status,地址状态复用总线,双向、三态)

分时复用的地址/状态线。作为地址线用时 A D 15 〜 A D 0 AD_{15}〜AD_0 AD15〜AD0和 A 19 〜 A 16 A_{19}〜A_{16} A19〜A16起构成访问存储器的 20 位物理地址当 CPU 访问 I/O 端口时, A 19 〜 A 16 A_{19}〜A_{16} A19〜A16保持为 “0 ”(低电平)。作为状态线用时, S 6 〜 S 3 S_6〜S_3 S6〜S3 用来输出状态信息,其中 S 3 S_3 S3 和 S 4 S_4 S4表示当前使用的段寄存器名。

| S 4 S_4 S4 | S 3 S_3 S3 | 段寄存器 |

|---|---|---|

| 0 | 0 | ES |

| 0 | 1 | SS |

| 1 | 0 | CS或未使用任何段寄存器(I/O、INT) |

| 1 | 1 | DS |

B H E ‾ / S 7 \overline{BHE}/S7 BHE/S7 ( Bus High Enable/Status,高8位数据总线允许/状态复用引脚,输出、三态,低电平有效)

表示当前高 8 位数据总线上的数据有效。当读/写存储器或据 I/O 端口以及中断响应时, B H E ‾ \overline{BHE} BHE与地址线 A D 0 AD_0 AD0 配合表示当前总线使用情况,如下表所示。非数据传送期间, S 7 S_7 S7 输出状态信息,低电平有效,在 CPU 处于保持响应期间被设置为高阻抗状态。

| B H E ‾ \overline{BHE} BHE | A D 0 AD_0 AD0 | 总线使用情况 |

|---|---|---|

| 0 | 0 | 16位数据总线 |

| 0 | 1 | 高8位数据总线上进行字节传送 |

| 1 | 0 | 低8位数据总线上进行字节传送 |

| 1 | 1 | 无效 |

8086微处理器存储库(1MB的存储空间)

8086 系统中的存储器是一个最多 1MB 的序列,即可寻址的存储空间为 1MB , 系统为每字节分配一个 20 位的物理地址(对应的十六进制数地址范围为 00000H〜FFFFFH )。

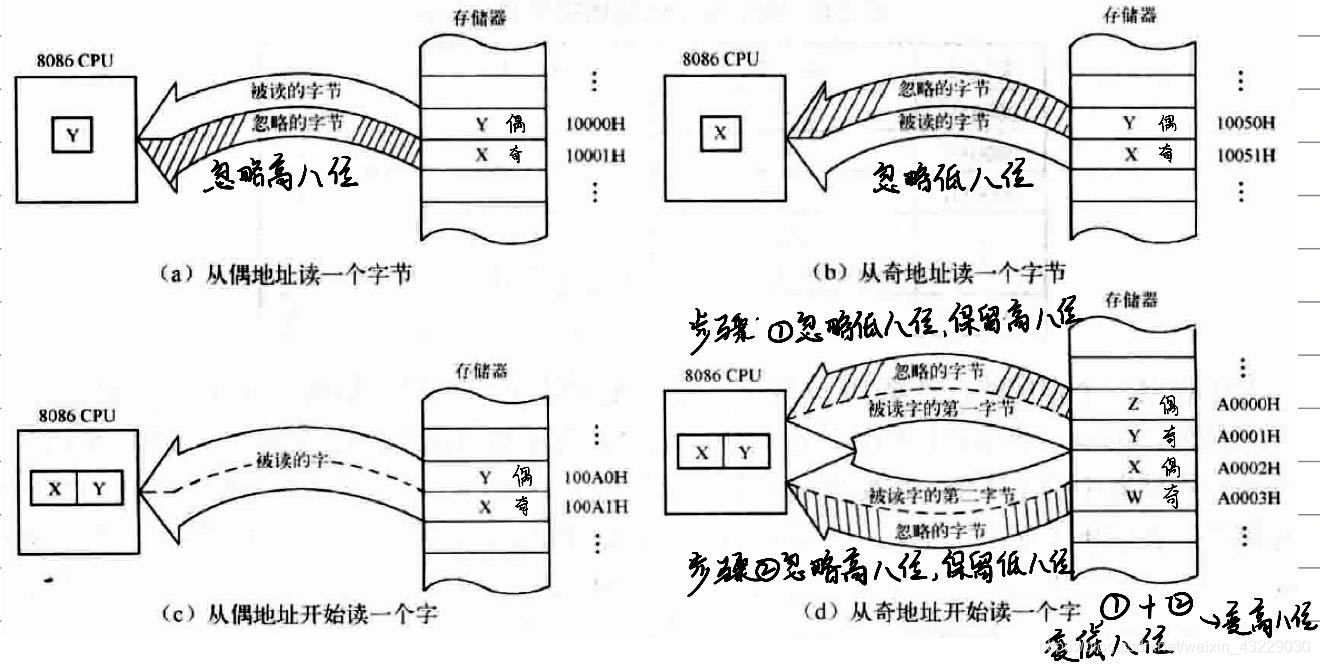

在存储器中任何两个相邻的字节被定义为一个字。在一个字中,每字节都有一个地址,并且这两个地址中的较小的一个被用来作为该字的地址。一个字的起始地址可以从偶地址开始,也可以从奇地址开始,并且较高存储器地址的字节存放该字的高 8 位,较低存储器地址的字节存放该字的低 8 位。

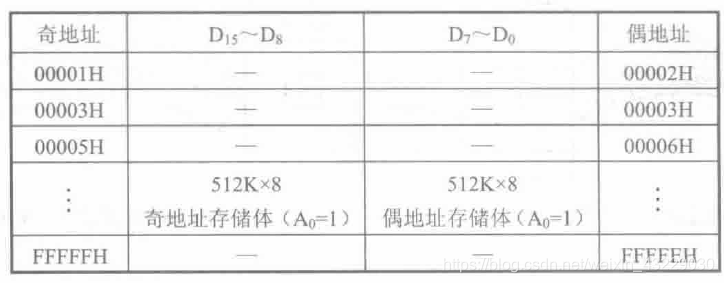

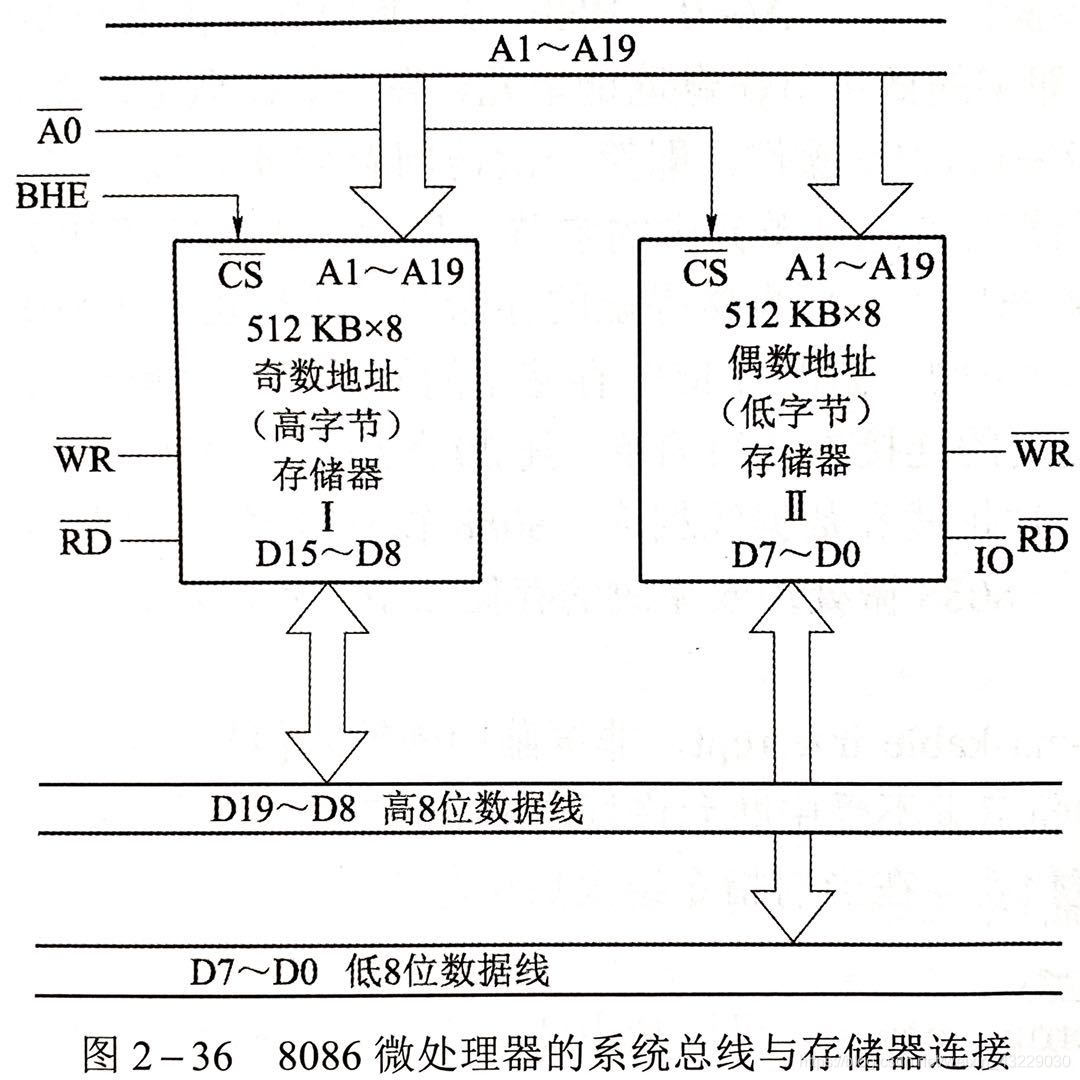

8086微处理器中的 1MB 存储空间实际上分为两个 512KB 的存储体,分别叫做高位库和低位库。低位库与数据总线 D7~D0 相连,该库中每个存储单元的地址为偶地址(低字节存储体);高位库与数据总线 D15~D8 相连,该库中每个存储单元的地址为奇地址(高字节存储体)。两个存储体采用字节交叉编址方式,如下表所示:

对于任何一个存储体,只要 19 位地址 (A19~A1) 就够了,地址总线 A19~A1 可同时对高、低位库的存储单元寻址,最低位地址码 A 0 A_0 A0 和 B H E ‾ \overline{BHE} BHE 配合起来表示用于对库的选择,分别连接到库选择端CS上,如下图所示

A 0 A_0 A0 和 B H E ‾ \overline{BHE} BHE相配合。使 CPU 可以访问一个存储体中的 1 字节或同时访问两个存储体中的 1 个字

| B H E ‾ \overline{BHE} BHE | A 0 A_0 A0 | 对应的操作 |

|---|---|---|

| 0 | 0 | 从偶地址读/写1个字 |

| 0 | 1 | 从奇地址读/写1个字 |

| 1 | 0 | 从偶地址读/写1个字节 |

| 0 | 1 | 从奇地址读/写1个字(分两次读写,这是第一次) |

| 1 | 0 | 从奇地址读/写1个字(分两次读写,这是第二次) |

如上所述,在字访问情况下,对奇地址存放的字需要进行两次读/写操作,而对偶地址存放的字,仅需要一次读/写操作。这样,为了加快程序的运行速度,希望被访问的存储器的字地址为偶地址。通常,这种从偶地址开始的字称为“对准字”,而从奇地址开始的字称为“非对准字”。

R D ‾ \overline{RD} RD ( Read,读信号,三态输出,低电平有效)

表示当前 CPU 正在读存储器或 I/O 端口。——如何区分?:取决于 M / I O ‾ M/\overline{IO} M/IO信号,引脚介绍3会说明

R E A D Y READY READY (准备就绪信号,由外部输入,高电平有效 )

用来使 CPU 和低速的存储器或 I/O 设备之间实现速度匹配的信号。当 R E A D Y READY READY 为高电平时表示 CPU 访问的存储器或 I/O 端口已准备好传输数据,可立即进行一次数据传输。当 R E A D Y READY READY 无效时,要求 CPU 插入一个或多个等待周期 T w T_w Tw ,直到 R E A D Y READY READY 信号有效为止。

I N T R INTR INTR (Interrupt Request,可屏蔽中断请求信号,输入)

中断请求信号(由外部输入,电平触发,高电平有效)。 I N T R INTR INTR 有效时,表示外部设备向 CPU 发出中断请求,CPU 在每条指令的最后一个时钟周期对 I N T R INTR INTR 进行测试。一旦测试到有中断请求,并且当中断允许标志 IF = 1 时,则暂停执行下条指令,转入中断响应周期。

N M I NMI NMI (Non-Maskable Interrupt Request,不可屏蔽中断请求信号,输入,边沿触发,正跳变有效)

NMI 不受中断允许标志的限制,CPU — 旦测试到 NMI 请求信号,待当前指令执行完,就自动从中断入口地址表中找到类型 2 中断服务程序的入口地址,并转去执行。NMI 是一种比INTR 高级的中断请求,不受 IF 标志位的控制,也不能用软件进行屏蔽。NMI 中断经常由电源掉电引起

C L K CLK CLK (Clock,主时钟信号)

由时钟发生器 8284 输入。8086 CPU 可以使用的时钟频率随芯片型号不同而异,8086 为 5MHz , 8086-1 为 10MHz , 8086-2 为 8MHz

R E S E T RESET RESET(复位信号由,外部输入,高电平有效)

至少要保持4 个时钟周期的高电平,才能停止时钟周期的现行操作。CPU 接收到该信号后,停止进行操作,并对寄存器 FR 、IP、DS 、SS 、ES 及指令队列清零,而将 CS 设置为 FFFFH 。当复位信号变为低电平时,CPU 从 FFFF0H(FFFF:0000H) 开始执行程序。由此可见,采用 8086 CPU 计算机系统的启动程序就保持在开始的存储器中。当变为低电平是,CPU重新启动执行程序。

T E S T TEST TEST (测试信号,外部输入,低电平有效)

与等待指令 W A I T WAIT WAIT 配合使用,当CPU 执行 W A I T WAIT WAIT 指令时( W A I T WAIT WAIT 指令使处理器与外部硬件同步),每隔 5 个时钟周期对 T E S T TEST TEST 进行一次测试,若测试到该信号无效,则 CPU 继续执行 W A I T WAIT WAIT 指令,即处于空闲等待状态;若 CPU 测到 T E S T TEST TEST 输入为低电平,则转而执行 W A I T WAIT WAIT 的下一条指令。 T E S T ‾ \overline{TEST} TEST 用于多处理器系统中,实现8086/8088 主 CPU 与协处理器(8087 或 8089)间的同步协调功能,由此可见, T E S T TEST TEST 对 W A I T WAIT WAIT 指令起到监视的作用。

引脚介绍3:最小模式下的引脚信号

W R ‾ \overline{WR} WR (Write,写信号,三态输出,低电平有效)

表示当前 CPU 正在写存储器或 I/O 端口。

M / I O ‾ M/\overline{IO} M/IO (Memory/input and output,存储器或输入输出操作选择信号,输出、三态)

存储器或 I/O 端口访问信号(三态输出)。 M / I O ‾ M/\overline{IO} M/IO 为高电平时,表示当前 CPU 正在访问存储器; M / I O ‾ M/\overline{IO} M/IO 为低电平时,表示当前 CPU 正在访问 I/O 端口。

- 在DMA(direct memory access)方式下, M / I O ‾ M/\overline{IO} M/IO为高阻状态

D E N ‾ \overline{DEN} DEN (Data Enable,数据允许信号,三态输出,低电平有效)

在最小模式系统中作为数据收发器 8286 / 8287 的选通信号。它在每一次存储器访问、I/O访问或中断响应周期有效。

- 在DMA(direct memory access)方式下,为高阻状态

D T / R ‾ DT/\overline R DT/R (Data Transmit/Receive):数据发送/接收控制信号(三态输出)

在最小模式系统中用来控制数据收发器 8286 / 8287 的数据传送方向。当 D T / R ‾ DT/\overline R DT/R 为高电平时,表示数据从 CPU 向外部输出,即完成写操作; D T / R ‾ DT/\overline R DT/R 为低电平时,表示数据从外部向 CPU 输入,即完成读操作。

I N T A ‾ \overline{INTA} INTA ( Interrupt Acknowledge,中断响应信号,向外部输出,低电平有效 )

表示 CPU 响应了外部发来的 INTR 信号。在中断响应总线周期,它可作为选通信号。

A L E ALE ALE (Address Latch Enable,地址锁存允许信号,向外部输出,高电平有效)

在最小模式系统中作为地址锁存器 8282 / 8283 的片选信号。ALE 输出有效电平(实际上是一个正脉冲),以表示当前地址 / 数据、地址 / 状态复用总线上输出的是地址信息,并利用它的下降沿将地址锁存到锁存器。ALE 信号不能浮空。

H O L D HOLD HOLD (Hold Request,总线请保持请求信号,输入,高电平有效)

向 CPU 请求使用总线。

最小模式下系统中除了主 CPU 以外的其他总线控制器(如 DMA 控制器)申请使用系统总线的请求信号。

H L D A HLDA HLDA (Hold Acknowledge,总线保持响应信号,输出,高电平有效)

对 H O L D HOLD HOLD 的响应信号,当 CPU测得 H O L D HOLD HOLD 脚为高电平,如果 CPU又允许让出总线,就在当前总线周期结束时,使 H L D A HLDA HLDA 有效,表示响应这一总线请求,CPU 放弃对总线的控制权,并立即使 3 条总线都置为高阻状态。CPU 中的 EU 可以继续工作到下一次要求使用总线为止。申请使用总线的控制器在收到 H D L A HDLA HDLA 信号后,就获得了总线控制权。在此后的一段时间内, H D L A HDLA HDLA 和 H O L D HOLD HOLD 均保持高电平。当获得总线使用权的其他控制器用完总线后,使 H O L D HOLD HOLD 变为低电平表示放弃对总线的控制权,CPU 只有当 H O L D HOLD HOLD 无效时,才将 H L D A HLDA HLDA 置成无效,并且收回对总线的使用权,继续自己的操作。

引脚介绍4:最大模式下的引脚信号

S 2 ‾ 、 S 1 ‾ 、 S 0 ‾ \overline{S2} 、\overline{S1} 、\overline{S0} S2、S1、S0 ( Bus Cycle Status,总线周期状态信号,三态输出)

在最大模式系统中由 CPU 传送给总线控制器 8288 , 8288 对它们译码后代替 CPU 输出相应的控制信号。

| S 2 ‾ \overline{S2} S2 | S 1 ‾ \overline{S1} S1 | S 0 ‾ \overline{S0} S0 | 经总线控制器 8288 产生的控制信号 | 操作功能 |

|---|---|---|---|---|

| 0 | 0 | 0 | I N T A ‾ \overline{INTA} INTA | 发中断响应信号 |

| 0 | 0 | 1 | I O R C ‾ \overline{IORC} IORC | 读 I/O 端口 |

| 0 | 1 | 0 | I O W C ‾ 、 A I O W C ‾ \overline{IOWC}、\overline{AIOWC} IOWC、AIOWC | 写 I/O 端口 |

| 0 | 1 | 1 | 无 | 暂停 |

| 1 | 0 | 0 | M R D C ‾ \overline{MRDC} MRDC | 取指令 |

| 1 | 0 | 1 | M R D C ‾ \overline{MRDC} MRDC | 读内存 |

| 1 | 1 | 0 | M W T C ‾ 、 A M W C ‾ \overline{MWTC}、\overline{AMWC} MWTC、AMWC | 写内存 |

| 1 | 1 | 1 | 无 | 无效状态 |

S 2 ‾ 、 S 1 ‾ 、 S 0 ‾ \overline{S2} 、\overline{S1} 、\overline{S0} S2、S1、S0 至少有一个信号为低电平的时候称为有效状态。

R Q ‾ / G T 0 ‾ 和 R Q ‾ / G T 1 ‾ \overline{RQ}/\overline{GT0}和\overline{RQ}/\overline{GT1} RQ/GT0和RQ/GT1 (request/grant,总线请求信号(输入)/总线请求允许信号(输出),双向,低电平有效)。

该信号为输入时,表示其他主控者向 CPU 请求使用总线;为输出时,表示 CPU 对总线请求的响应信号。这两个信号是最大模式下系统中主CPU和其他协处理器(8087/8089)之间交换总线使用权的联络控制信号。 R Q ‾ / G T 0 ‾ 和 R Q ‾ / G T 1 ‾ \overline{RQ}/\overline{GT0}和\overline{RQ}/\overline{GT1} RQ/GT0和RQ/GT1 是两个同类型的信号,表示可以同时连接两个协处理器,其中

优先级: R Q ‾ / G T 0 ‾ > R Q ‾ / G T 1 ‾ \overline{RQ}/\overline{GT0}>\overline{RQ}/\overline{GT1} RQ/GT0>RQ/GT1

L O C K ‾ \overline{LOCK} LOCK (封锁信号,三态输出,低电平有效)

有效时,表示 CPU 不允许其他总线主控者占用总线。这个信号由软件设置。当在指令前加上 L O C K LOCK LOCK 前缀时,则在执行这条指令期间保持有效,即在此指令执行期间,CPU 封锁其他主控者使用总线。当含有 L O C K LOCK LOCK 前缀的指令执行完毕之后, L O C K ‾ \overline{LOCK} LOCK 变成高电平,从而撤销了总线封锁。此外在CPU 处于 2 个中断响应周期期间, L O C K ‾ \overline{LOCK} LOCK 会自动变成有效的低电平,以防止其他总线模块在中断响应过程中占有总线而使一个完整的中断响应过程被间断。

Q S 1 和 Q S 0 QS1 和 QS0 QS1和QS0 (Instruction Queue Status,指令队列状态,向外部输出),

用来表示 CPU 中指令队列当前的状态,如下表所示。设置这两个引脚的目的是让外部的设备监视 CPU 内部的指令队列,可让协处理器 8087 进行指令的扩展处理。

| Q S 1 QS1 QS1 | Q S 0 QS0 QS0 | 指令队列状态 |

|---|---|---|

| 0 | 0 | 无操作,未从指令队列中取指令 |

| 0 | 1 | 从指令队列中取出当前指令的第一个字节(操作码字节) |

| 1 | 0 | 指令队列空,由于执行转移指令,队列重新装填 |

| 1 | 1 | 从指令队列中取出指令的后续字节 |