4.2 利用MATLAB实现OFDM系统及仿真分析

通过上面几节内容,我们基本了解的OFDM的系统特点,下面我们利用MATLAB来实现OFDM系统的基本工作,并对每个模块做简单的分析。

4.2.1 信源产生模块

每个系统都有信号源,这里我们为了体现系统的系能,就利用随机的0,1信号做为系统的信号源。

message = randsrc(1,N)>0.5;

在这里,我们为了方便观察,取N为32,即产生32个随机数,当其大于0.5则产生信号1否则产生信号0。其仿真结果如图4-1所示。

图4-1 发送信号

通过上面的图,可以看到其产生的信号为1101-1001-1101-1010-0111-1011-1110-1010。当然由于我们是利用随机函数来完成信源的产生的,所以实际操作时产生的信号不一定就是上面我们给出的信号。

4.2.2 QPSK调制

下面我们将产生的信号通过QPSK进行调制,四相相移键控信号简称“QPSK”。它分为绝对相移和相对相移两种。由于绝对移相方式存在相位模糊问题,所以在实际中主要采用相对移相方式QDPSK。它具有一系列独特的优点,目前已经广泛应用于无线通信中,成为现代通信中一种十分重要的调制解调方式。是目前最常用的一种卫星数字信号调制方式,它具有较高的频谱利用率、较强的抗干扰性、在电路上实现也较为简单。

message_PSK = QPSK(message);

这里QPSK是我们自定义的一个函数,通过这个函数,可以完成信号的QPSK调制,其仿真结果如下所示:

图4-2 QPSK调制信号

为了对比OFDM的系统性能,利用系统的星座图进行性能分析是一种比较好的方法,这里我们利用MATLAB内部的一个函数来分析系统的星座图,scatterplot(message_PSK),我们可以得到如下的仿真结果:

图4-3 系统星座图

4.2.3 IFFT变换模块

IFFT是OFDM系统中的重要环节,通过IFFT变化,将信号的频率变换到时域上来,这里IFFT函数是自定义的函数。

message_IFFT = myIFFT(message_PSK,N/2);

其仿真结果如下图所示:

4.2.4 发送端低通滤波器模块

为了使得到的信号尽可能的保持质量,我们必须保证发送出去的信号是接近理想的信号,即发送出去的信号没有毛刺,边带的平滑的,而且在信号的频域上没有高频分量。所以我们必须将信号通过一个低通滤波器。

filter=rcosine(Fd,Fs,'sqrt',R,3);

message_cos1_real = rcosflt(real(message_upsmp),Fd,Fs,'filter/Fs',filter,1,3);

message_cos1_imag = rcosflt(imag(message_upsmp),Fd,Fs,'filter/Fs',filter,1,3);

message_cos1 = message_cos1_real + message_cos1_imag*j;

通过上面的代码我们将信号通过一个根升余弦滤波器。从而完成信号的滤波,最后将信号发送出去。

图4-5 通过发送端低通滤波器的信号

4.2.5 接收端滤波器模块

在实际系统中,无论发送出去的信号多么完美,都会受到信道中噪声的影响,应此在OFDM系统的接收端,我们必须再加上一个低通滤波器,使接收到的信号更加的平滑。

filter=rcosine(Fd,Fs,'sqrt',R,3);

message_cos2_real = rcosflt(real(message_awgn),Fd,Fs,'filter/Fs',filter,1,3);

message_cos2_imag = rcosflt(imag(message_awgn),Fd,Fs,'filter/Fs',filter,1,3);

message_cos2 = message_cos2_real + message_cos2_imag*j;

这里代码的具体实现和发送端的低通滤波器相同,在这里就不做介绍了其仿真如下所示:

图4-6 通过接收端低通滤波器的信号

4.2.6 FFT变换模块

OFDM系统接收部分最重要的就是FFT变化了,即将信号的时域变回到信号的频域。这里我们利用自定义的FFT函数对接收的信号进行FFT变化。

message_FFT = myFFT(message_downsmp,N/2);

其仿真结论如下所示:

图4-7 FFT变化仿真图

4.2.7 QPSK解调和信号还原

最后对FFT变换后的信号进行QPSK解调,还原得到原始的发送信号。这里QPSK解调的函数是自定义函数。

message_real = D_QPSK(message_FFT);

scatterplot(message_FFT);

其仿真结果如下所示:

图4-8 QPSK解调后的信号以及信号眼图

其接收到的信号为1101-1001-1101-1010-0111-1011-1110-1010,说明信号的正确性。

4.3 总结

本章,我们利用MATLAB在前面理论知识的指导下,基本实现了OFDM系统的基本过程,通过MATLAB的系统性能仿真,验证了我们系统总体方案的正确性。为一步使用FPGA来实现OFDM系统奠定了基础。

第五章 OFDM的FPGA实现

5.1 FPGA简介

FPGA是近几年出现的新型可编程逻辑器件,它不仅具有很高的速度和可靠性,而且具有用户重复定义的逻辑功能,即具有可编程的特点。它的出现不仅使数字电路系统的设计非常灵活,而且大大缩短了系统研制周期,缩小了数字电路系统的体积和所用芯片的种类。

当今社会是数字化的社会,是数字集成电路广泛应用的社会。数字集成电路本身在不断地进行更新换代。它由早期的电子管、晶体管、小中规模集成电路、发展到超大规模集成电路(VLSIC,几万门以上)以及许多具有特定功能的专用集成电路。但是,随着微电子技术的发展,设计与制造集成电路的任务已不完全由半导体厂商来独立承担。系统设计师们更愿意自己设计专用集成电路(ASIC)芯片,而且希望ASIC的设计周期尽可能短,最好是在实验室里就能设计出合适的ASIC芯片,并且立即投入实际应用之中,因而出现了现场可编程逻辑器件(FPLD),其中应用最广泛的当属现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。

早期的可编程逻辑器件只有可编程只读存贮器(PROM)、紫外线可删除只读存贮器(EPROM)和电可擦除只读存贮器(EEPROM)三种。由于结构的限制,它们只能完成简单的数字逻辑功能。其后,出现了一类结构上稍复杂的可编程芯片,即可编程逻辑器件(PLD),它能够完成各种数字逻辑功能。典型的PLD由一个“与”门和一个“或”门阵列组成,而任意一个组合逻辑都可以用“与-或”表达式来描述,所以, PLD能以乘积、和的形式完成大量的组合逻辑功能。这一阶段的产品主要有PAL(可编程阵列逻辑)和GAL(通用阵列逻辑)。 PAL由一个可编程的“与”平面和一个固定的“或”平面构成,或门的输出可以通过触发器有选择地被置为寄存状态。 PAL器件是现场可编程的,它的实现工艺有反熔丝技术、EPROM技术和EEPROM技术。还有一类结构更为灵活的逻辑器件是可编程逻辑阵列(PLA),它也由一个“与”平面和一个“或”平面构成,但是这两个平面的连接关系是可编程的。 PLA器件既有现场可编程的,也有掩膜可编程的。

20世纪80年代中期。 Altera和Xilinx分别推出了类似于PAL结构的扩展型 CPLD(Complex Programmab1e Logic Dvice)和与标准门阵列类似的FPGA,它们都具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点。 这两种器件兼容了PLD和通用门阵列的优点,可实现较大规模的电路,编程也很灵活。与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

FPGA与 CPLD都是可编程逻辑器件,它们是在PAL、GAL等逻辑器件的基础之上发展起来的。同以往的PAL、GAL等相比较,FPGA/CPLD的规模比较大,它可以替代几十甚至几千块通用IC芯片。

积。此外Altera公司的Cyclone系列的FPGA在通信行业具有广泛的应用,这是一款低成本的FPGA产品。

MaxPlusII是ALTERA公司较早的一款软件,它的界面非常的简单,是初学者比较容易接受的一款软件,但是Altera公司已经停止了对其的升级,所以MaxPlusII所支持的器件比较少,而且对于一些大型项目开发就不太适用了[21,22,23,24,25]。

图5-1 MaxPlusII界面

QuartusII是ALTERA公司的新一代开发软件,它拥有两种界面,一种是QuartusII的界面,另一种是用有QuartusII全部功能的MaxPlusII界面,从而使原有的MaxplusII的用户更快的适应新的开发环境。目前 QuartusII 最高版本好似QuartusII7.2。相对于MaxPlusII,QuartusII支持更多的器件,而且也支持Altera最新的一些器件如Straix、Straix GX系列。在本课题中,我们采用QuartusII开发软件,在功能上比MAXplusII更加强大,在本课题,我使用的是 QuartusII 7.2。

图5-2 QUARTUSII 7.2界面

文中,对于一些简单的小模块,给出的仿真图是用maxplusII的,而对于一些较大的模块和最后结果仿真,则采用QuartusII给出。

5.2 利用FPGA实现OFDM系统及仿真分析

在本节,我们将介绍如何利用FPGA来实现OFDM系统并对整个系统做仿真分析其性能,并将仿真结果和MATLAB仿真结果进行对比从而验证FPGA设计的正确性。

5.2.1 基于FPGA的OFDM系统的基本结构

OFDM系统的基本结构如下所示,当然我们这里只设计其主要几个部分。

图5-1 OFDM简化模块

因此,我们设计的重点就是IFF,FFT和并串、串并转化模块。

5.2.2 基于FPGA的OFDM系统实现

通过以上的分析,OFDM系统最重要的就是FFT和IFFT模块的设计,因此我们主要通过ISE中的FFT/IFFT的IP核来设计这个两个模块。通过简单的配置得到所要的模块。

首先,我们简单的介绍一下如何配置FFT的IP核。ALTERA公司推出的IP核,都会冠以“MegaCore”的商标,其实FFT MegaCore就是一个可以实现FFT/IFFT功能的IP核。FFT MegaCore的使用非常方便,可以大大加速产品的设计周期。它可以应用在 ALTERA 的主流 FPGA系列芯片上,包括Cyclone、Stratix和HardCopy。而且因为是ALTERA自己设计的IP,所以专门为这些FPGA芯片做了优化,相对于个人编写的FFT电路来说,ALTERA的IP具有更高的性能,占用更少的资源。毕竟最了解这些 FPGA器件的还是ALTERA公司自己。FFT MegaCore支持超过300M的时钟频率。

整个 FFT MegaCore的应用流程非常简单。可以在 Quartus软件中非常方便地进行配置并把FFT模块加入到自己的工程设计中。本小节对使用的流程进行了介绍。

使用FFT MegaCore需要新建一个工程或者在一个已有的工程中。在本文中我们新建一

个工程作为范例。要在工程中应用 FFT MegaCore,需要先启动 IP Toolbench,一个FFT MegaCore的参数配置程序。 先点击 “Tool” 菜单下的 “MegaWizard Plug-In Manager…” 。如下图所示。

图5-2 IP核设计界面一

应此我们设计的数字系统是一个OFDM 通信系统中的基带数据处理部分,就是不包括变频,射频电路部分的设计,甚至没有加入同步的部分,而是只包括信道编码、交织、星座映射、FFT 和插入循环前缀的部分。这离一个完整的 OFDM 系统还差得很远,不过我觉得自己已经尽力了,也许以后有机会还可以在此基础上再做得更好些。下面叙述一下发射和接收端的具体结构。

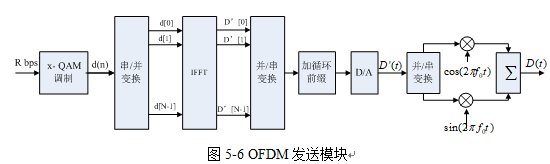

OFDM发送模块,其主要包括信号调制模块(QAM/QPSK),串并转换,IFFT变化,并串转换,编码模块。

图5-7 OFDM接收模块

OFDM接收模块,其主要包括解码模块,串并转换,FFT变化,并串转换,信号解调模块(QAM/QPSK)。

5.2.3 系统仿真分析

上面我们基本完成了OFDM系统的FPGA实现,下面我来分析其仿真结果。下图是整个系统的仿真示意图。

图5-8 系统仿真图

为了便于观察,我们来详细介绍每一个部分的仿真结果,首先来看发送信号,我们在这里发送1,7,3,4,5,6这几个数字。

然后在发送端,最重要的部分就是IFFT变换,其仿真结果图如下所示:

![]()

图5-10 IFFT仿真图

而在接收端,最重要的部分就是FFT变换,其仿真结果图如下所示:

图5-11 FFT仿真图

我们可以看到,发送信号通过OFDM系统以后,又还原得到了原来的信号了,说明这个系统是正确的。

图5-12 接收信号的结果仿真图

5.3 总结

本文在对OFDM(正交频分复用)调制解调方式进行研究的基础上,在ALTERA公司FPGA上的实现了一个基带的OFDM调制解调系统。并着重讨论了用FFT/IFFT来实现OFDM的解调问题。在FPGA上实现的OFDM系统分为调制和解调两个子系统,分别完成了子信道的IFFT的OFDM调制, FFT变换的OFDM解调。最后使用QUARTUSII8完成了整个OFDM调制解调电路的设计、仿真和实现,与MATLAB实现结果的比较,运算结果良好。