- 范围

本文档介绍了SylixOS在Xilinx Zynq-7000开发板上如何进行L2 Cache划分。

在AMP模式中,core 0与core 1共用512K L2 Cache,这势必会引起两个核的Cache竞争问题。 - 用处

通常情况下,L2 Cache被core 0,core 1共享。

core 0的内存访问操作可能会清除core 1所使用的L2缓存内容,从而使core 1的软件性能有不确定性。

有时,我们需要为core 0 或core 1提供更多的确定性行为。

尤其是架构为AMP时。

L2 Cache划分可以满足这种需求。

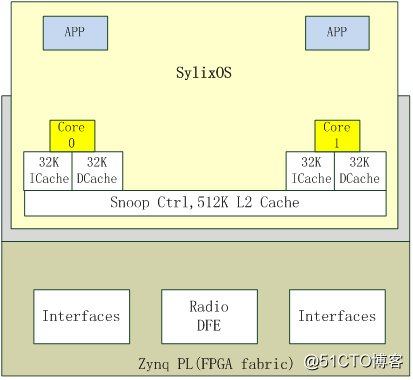

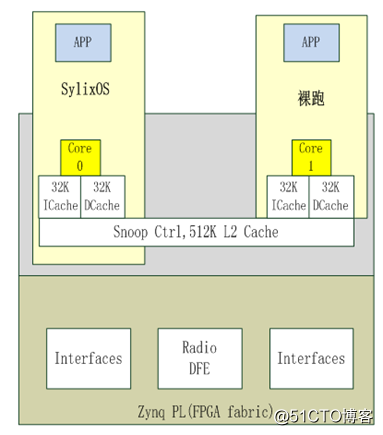

如图 2.1、图 2.2为SMP与AMP架构图。

图 2.1 SMP架构图

图 2.2 AMP架构图 - 原理

通过寄存器的控制可以将L2 Cache锁定在不同core上。

这让用户可以将L2 Cache的功能保留在特定的core上。

Cache way是分区的宽度,Zynq的L2 Cache有8 Cache ways。

L2 Cache控制器只能被锁定8个不同的方式。

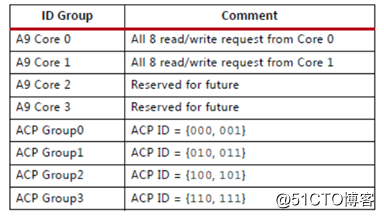

如图 3.1所示,在Zynq 7000中,Cortex-A9 MP核的64个AXI被分为8个可以锁定的组。

图 3.1分组 - 配置

具体寄存器说明参照Xilinx 官方数据手册UG585。

配置1:通常情况(L2 Cache 被core 0和core 1共享)。

Reg9_d_lockdown0 = 0x0;

Reg9_1_lockdown0 = 0x0;

Reg9_d_lockdown1 = 0x0;

Reg9_1_lockdown1 = 0x0;

配置2:4-0-4方式,每个核用一半(core 0使用Cache way【0..3】;core 1使用Cache way【4..7】)。

reg9_d_lockdown0 = 0xFFF0;

reg9_1_lockdown0 = 0xFFF0;

reg9_d_lockdown1 = 0xFF0F;

reg9_1_lockdown1 = 0xFF0F;

配置3:2-4-2方式(core 0使用Cache way【0..1】;core 1使用Cache way【6..7】;两个核共享Cache way【2..5】)。

reg9_d_lockdown0 = 0xFFC0;

reg9_1_lockdown0 = 0xFFC0;

reg9_d_lockdown1 = 0xFF03;

reg9_1_lockdown1 = 0xFF03;

SylixOS在ZYNQ7000上划分CACHE

猜你喜欢

转载自blog.csdn.net/liuzq/article/details/80457285

今日推荐

周排行