D触发器的输出有些需要注意到的地方。

首先以下面的东西做个例子,0-7的计数器,有一个控制计数端en,en控制计数的起始发生。

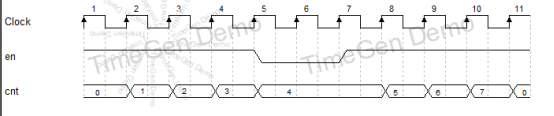

我们目标电路的波形图我们设为:

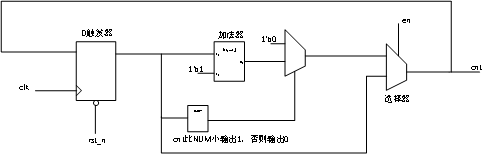

这个原理图是错误的,首先输出结果是从1开始的,不是从0开始计数的;其次在cnt为3时,3传输回到D触发器,在第五个上升沿处,D触发器输出3,然后此刻en为低电平(在D触发器输出结果后en就是采到0,在D触发器工作过程中en为1),则此刻cnt输出结果为3,且3应该保持到第7个上升沿处,在第七个上升沿处cnt发生变化,cnt变为4.

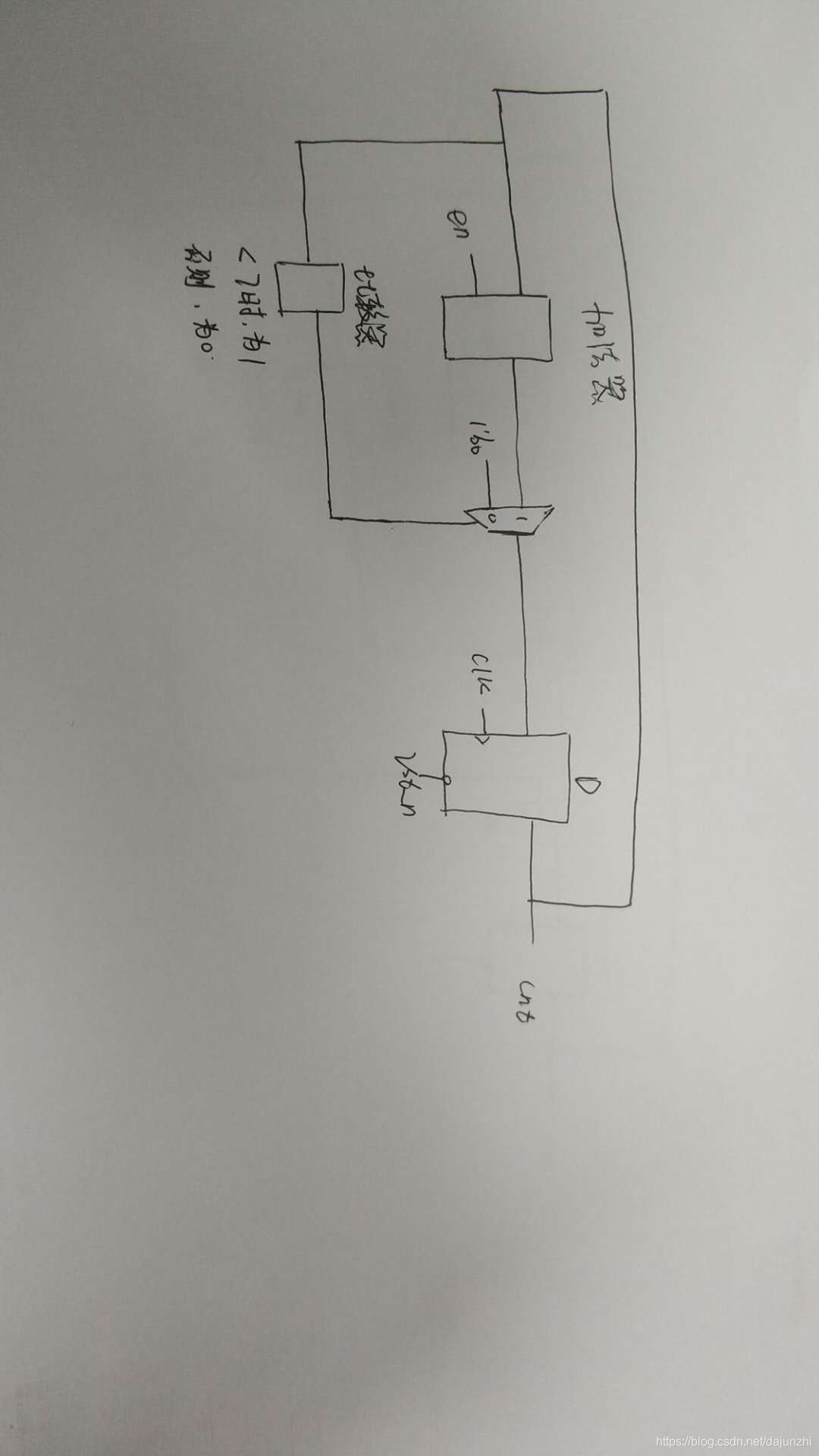

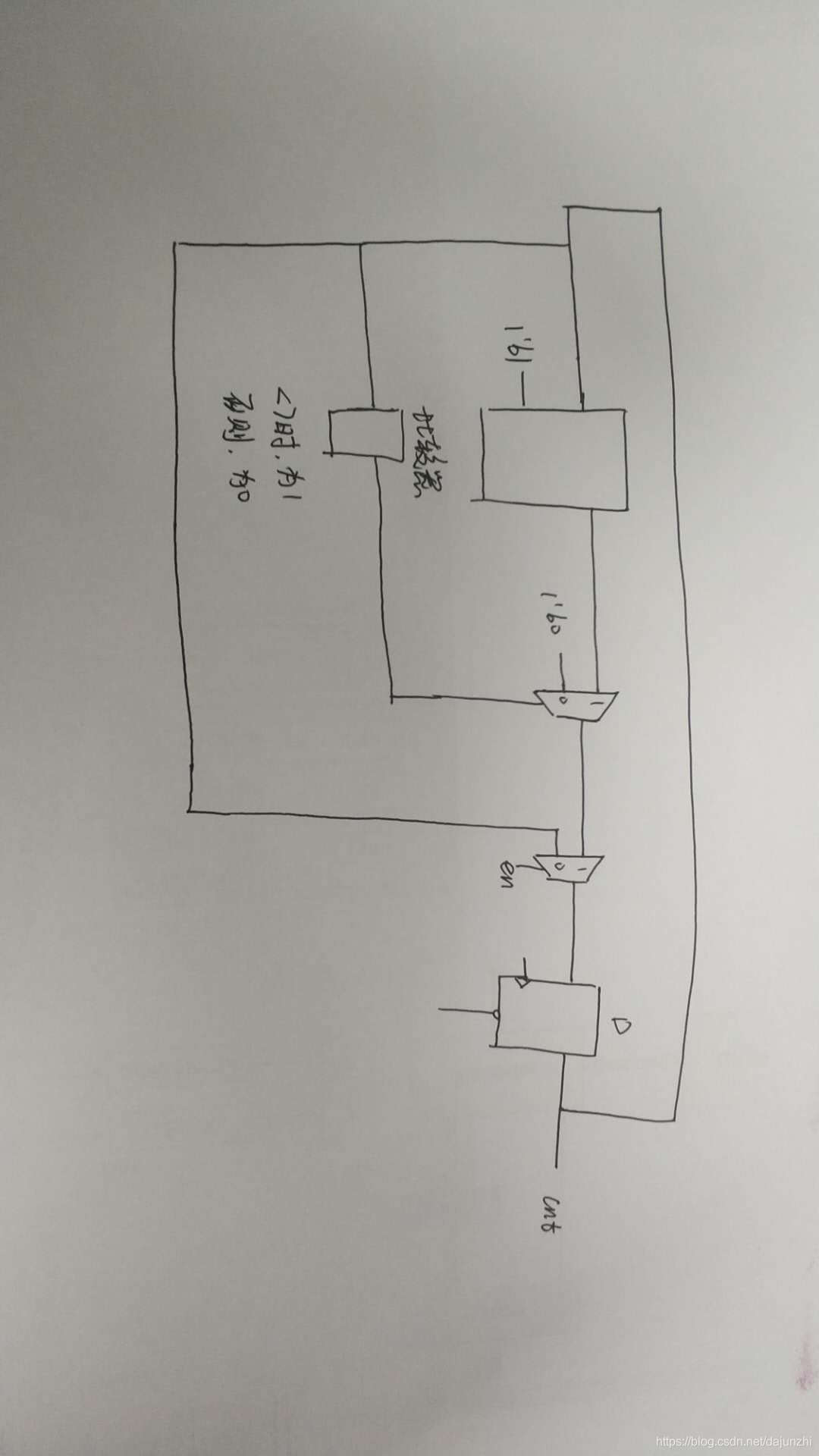

根据波形图,可将电路画为:

上面两个原理图都可以实现原理中的波形图,但是图二中能够实现en为0时系统暂停工作的目的,达到减少功耗的目的。

最开始的原理图实现的波形图如下:

(上图所有的波形中输入都经过了D是、触发器处理之后再输入)