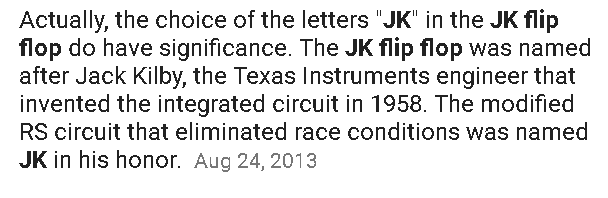

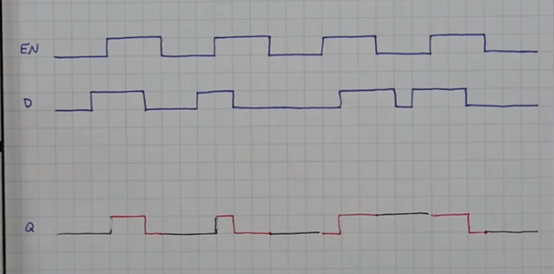

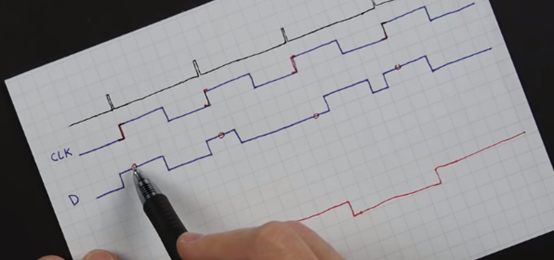

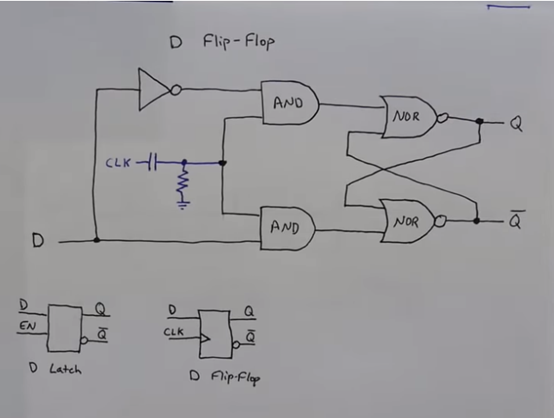

之前搞了一个 D-Latch,看一下下图是怎么变化的

In D-latch anytime its enabled the input D is going to be output at Q

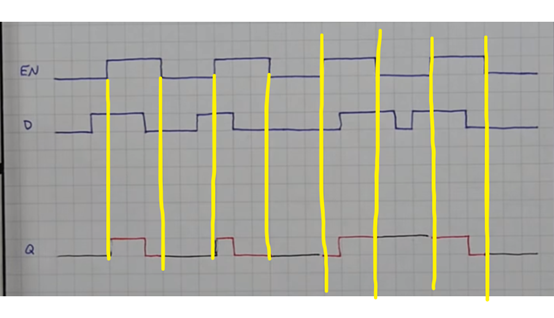

使用clk

通常情况下clk输入是这样的,很短很短的一下:

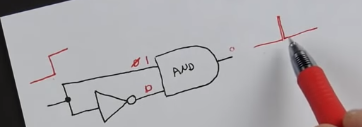

这个很短的脉冲是怎么实现的呢?

答案:

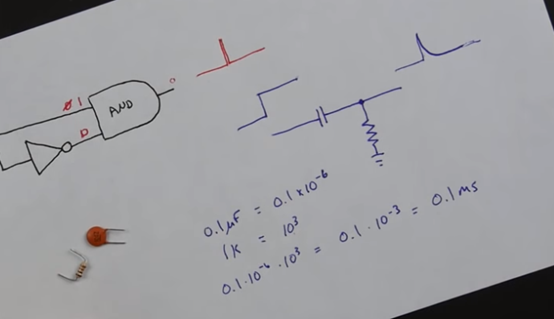

可以用下面的东西:

输入为0的时候inverter里面是1 当从0切换到1的时候 invertor里面的1不是瞬间变成0的,此时会产生一个很短的脉冲

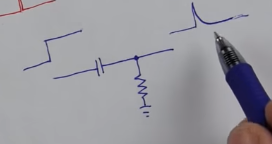

还可以用电容加电阻来实现:

这个脉冲的时间公式是C*R(电容乘电阻)

下面介绍D-Flip-Flop(D触发器)

Very similar to the D-Latch:

锁存器与触发器区别:

锁存器同其输入信号相关,当输入信号变化锁存器产生变化,没有时钟端

触发器受时钟控制,时钟触发时才采样当前的输入,产生输出

** ...

JK触发器: