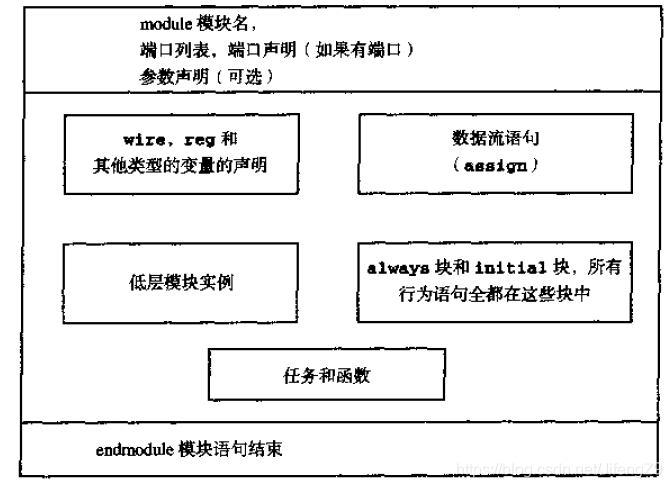

-verilog模块组成:

-端口:模块与外界环境交互的接口。所有端口隐含地声明为wire类型。若希望输出端口保存数值,则需要显式的声明为reg类型;输入与双向端口不能被声明为reg类型。

三种端口类型如下:

input:输入;

output:输出;

inout:输入/输出双向端口;

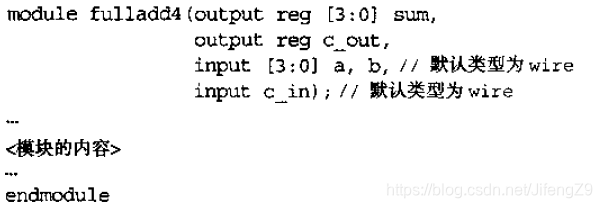

在声明端口数据类型时可以在模块端口列中声明(将端口声明嵌入到端口列表):

在模块中定义的所有过程块(initial、always等、连续赋值语句、实例引用都是并行的。

-端口连接规则:

模块之间通过端口互联时需要遵从以下规则:

1、

2、位宽匹配:允许内外两个部分具有不同位宽。

3、允许模块实例的端口保持未连接状态,例如作为测试端口

![]()

-端口连接方式:

1、顺序端口连接:需要连接到模块实例的信号必须与模块声明时目标端口在端口列表中的位置保持一致。

2、命名端口连接:端口和相应的外部信号按照其名字进行连接,其中括号内部的是该模块的端口,括号外部的是原模块的端口(即下面的fulladd4的端口)。

![]()

若某端口悬空,则忽略即可

![]()

-层次命名:顶层模块不能被其他模块调用,以顶层模块作为根,通过“.”连接对其他模块命名,即层次路径名。每个标识符都具有唯一的层次名。