上节讲到采用并联的方式巧妙解决了输入信号达不到两个电源轨的问题,在当今轨至轨运放中得到广泛应用。

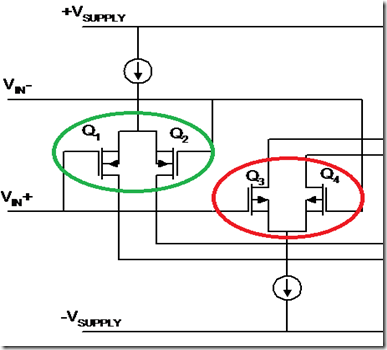

但这种并联差分输入级有一个先天的问题:输入失调电压交越问题,如下面的并联差分输入结构的运放输入前级图所示:

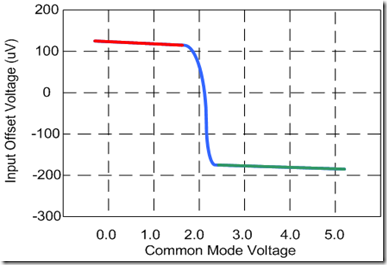

下图是这种运放的输入失调电压,可以看出:随着共模电压的升高,PMOS在2V左右将关闭,而NMOS即将打开,就在这个点上,运放的输入失调电压发生了跳变。这个可以理解,两组不同结构的输入级输入失调电压是不同的,在交接棒时,这个失调电压也完成了交接棒。对于直流信号,这个问题会引起误差突变,对于正弦交流信号,这个问题会引起信号的失真,在交越点引入一个小台阶。

为了解决这个问题,TI公司设计了两种领先的差分级输入。第一种结构如下,PMOS差分输入级能达到负电源轨但达不到正电源轨,于是在内部将输入级的电源提高1.8V(足够了)。这样输入级就能达到正电源轨了。而且只有一组差分输入级,并不会存在输入失调电压交越问题。

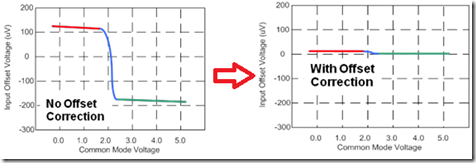

第二种就是自调零技术(MOSFET Zero Drift)。下图是自调零前后的对比图,效果很明显吧。