提升的历程

01 早期的提升 是通过加快 晶体管的切换速度来进行提升, 但是很快遇到的瓶颈.

02 增加各种复杂的指令,如: 加密,压缩,直接除,游戏等, 指令太多, 如何快速传递数据给CUP呢, RAM成为瓶颈

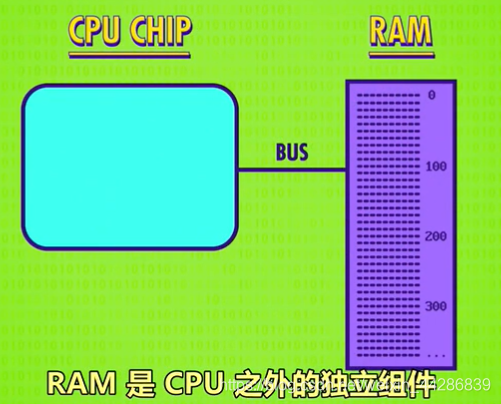

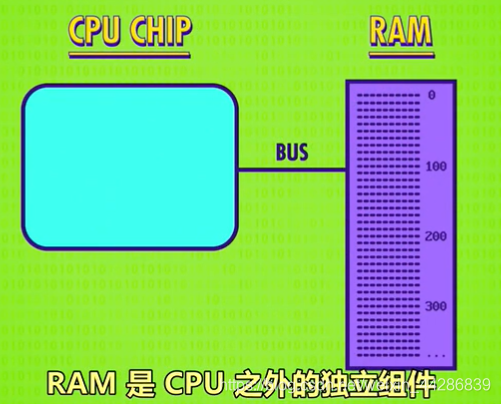

数据要用线来传递, 叫"总线", 长度只有几厘米,电信号几近光速.,但是CPU每秒可以出来 上亿条指令, 很小的延迟也会成为问题

RAM 还需要时间找地址,取数据,配置,输出数据

一条"从内存读取数据"的指令可能需要多个时钟周期, CPU需要等数据

方式一 缓存

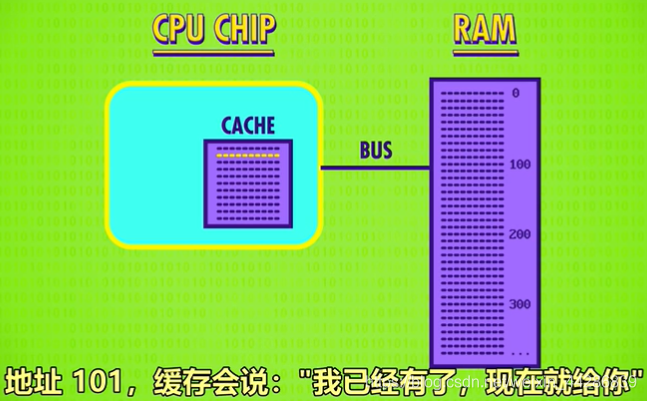

新的架构: 给CPU增加缓存, 这样,RAM给CPU数据时可以一次传一批,而不是一个一个传.

当然,开始会比较慢,但是后面会加速.因为内存的指令是按照顺序执行的.

因为距离问题, 缓存一个时钟周期就可以给数据.

如果缓存的数据已经缓存了,叫 缓存命中, 如果数据不再缓存中, 叫 缓存未命中

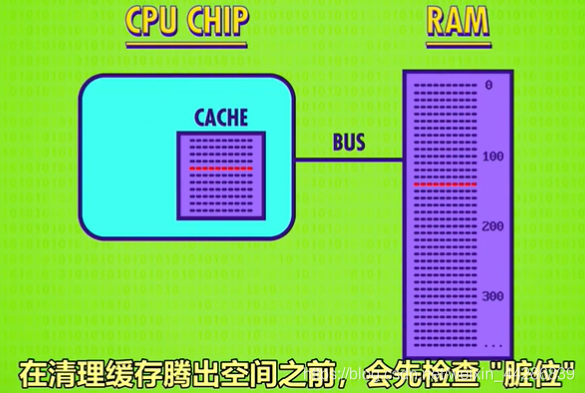

当然CPU的计算结果也会存在缓存中, 这样 缓存和RAM中的数据就会不一致, 这种不一致必须记录下来, 之后要同步.

缓存的每个位置都有一个特殊标记, 叫 脏位

一般缓存满了, CPU又需要缓存时, 就会发生同步.

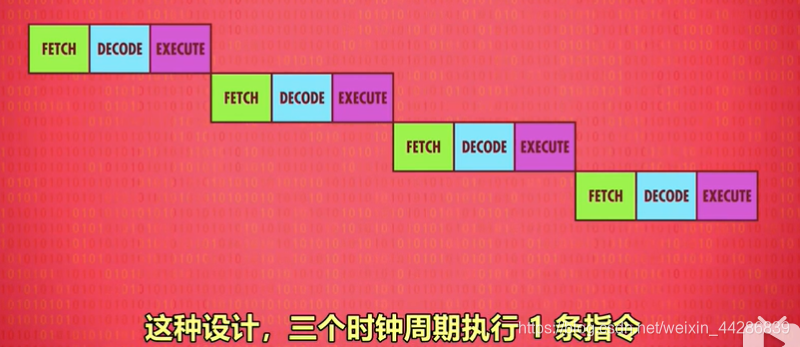

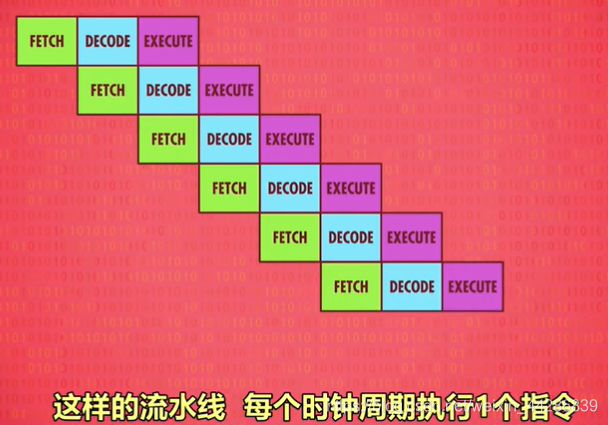

方式二 指令流水线

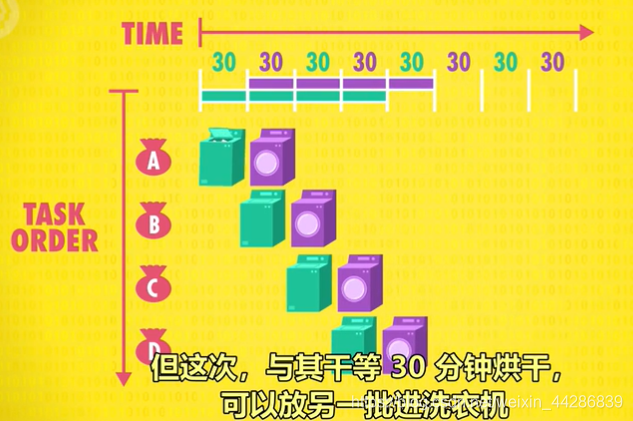

那么可以流水进行.

问题是: 这个首先需要弄清楚各个指令的依赖关系, 必要时需要停止流水线,避免出现问题

很多高端CPU设备会动态排序 有依赖的指令, 叫 乱序执行

因为高效, 几乎现代所有的处理器都有流水线

但是遇到JUMP时, 流水线就会有分支, 这时出现了 “分支预测”, 就是猜测哪个分支的可能性比较大. 目前的CPU正确率高达90%

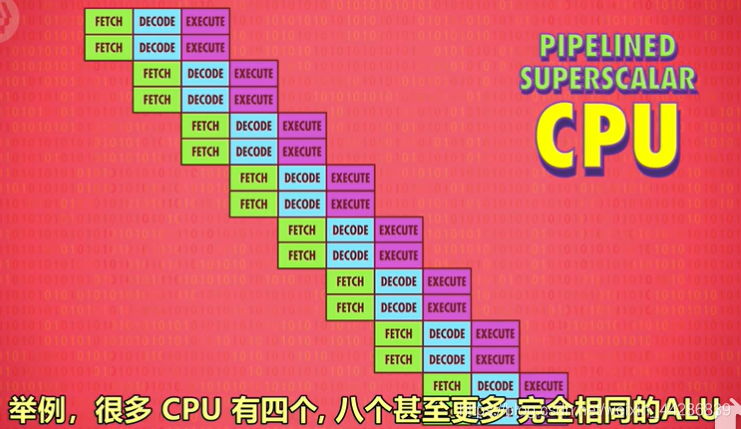

进一步提升 一 ALU

超标量处理器: 一个时钟周期完成多个指令

多条指令要ALU的不同部分,就多条指令同时执行, 多加几个相同的线路.

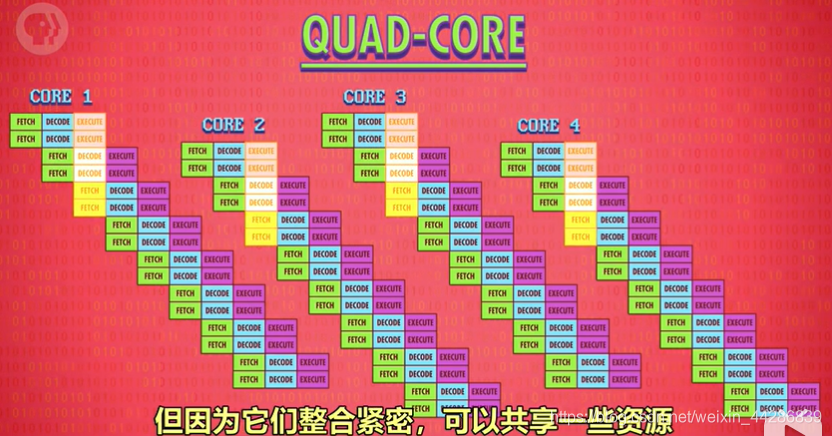

进一步提升 二 多核处理器

多指令流, 用多个独立的CPU核进行处理

可以 共享 缓存!

内核不够使时, 可以增加 CPU.

计算宇宙的形成, 需要更多的CPU

每秒 9亿亿次浮点运算