Learning chip: EP4CE6F17C8

This study uses a common cathode digital tube, that is, the digital tube is lit with a low level. It is also known that the anodes of the common anode digital tube are connected together, that is, the digital tube is lit with a high level.

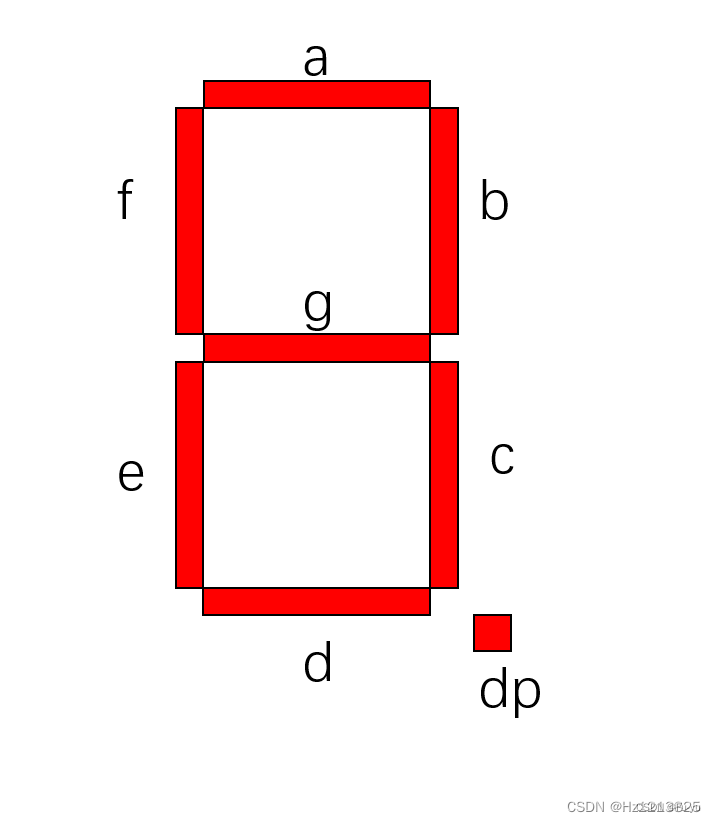

Schematic diagram of eight-segment digital tube:

When a,b,c,d,e,f,g,dg represent an eight-segment digital tube, a is the lowest bit, and dp is the highest bit

The eight-segment digital tube is represented by 8-bit binary. Since this experiment uses a common cathode digital tube, 0 means on, and 1 means off. That is, the digital tube displays the number 0, which we can use to represent, and the number F to represent. In the same way, the common cathode digital tube and the common anode digital tube are the opposite of each 8'b1100_0000other 8'b1000_0111.

1. Verilog programming enables six digital tubes to display 0-f at the same time, with a time interval of 0.5s

code show as below:

module seg_dynamic(

input wire clk,

input wire rst_n,

output wire [7:0] seg,//选择哪一段亮

output wire [5:0] sel//选择哪一个数码管亮

);

localparam CNT_0_5S_MAX = 25'd25_000_000;//0.5s

localparam CNT_20NS_MAX = 16'd50_000;//20ns

parameter ZERO = 8'b1100_0000,

ONE = 8'b1111_1001,

TWO = 8'b1010_0100,

THREE = 8'b1011_0000,

FOUR = 8'b1001_1001,

FIVE = 8'b1001_0010,

SIX = 8'b1000_0010,

SEVEN = 8'b1111_1000,

EIGHT = 8'b1000_0000,

NINE = 8'b1001_0000,

A = 8'b1000_1000,

B = 8'b1000_0011,

C = 8'b1100_0110,

D = 8'b1010_0001,

E = 8'b1000_0110,

F = 8'b1000_1110;

reg [24:0] cnt_0_5s;

reg [3:0] cnt_num;

reg [19:0] cnt_delay;

reg [2:0] cnt_seg;

reg [7:0] seg_r;

reg [5:0] sel_r;

//0.5s计数

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

cnt_0_5s <= 25'd0;

end

else if(cnt_0_5s == CNT_0_5S_MAX-1'd1)begin

cnt_0_5s <= 25'd0;

end

else begin

cnt_0_5s <= cnt_0_5s +1'd1;

end

end

//20ms计数

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt_delay <= 16'd0;

end

else if(cnt_delay == CNT_20NS_MAX -1'd1)begin

cnt_delay <= 16'd0;

end

else begin

cnt_delay <= cnt_delay +1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt_num <= 4'd0;

end

else if(cnt_num == 4'd15 && cnt_0_5s == CNT_0_5S_MAX-1'd1)begin

cnt_num <= 4'd0;

end

else if(cnt_0_5s == CNT_0_5S_MAX-1'd1)begin

cnt_num <= cnt_num +1'd1;

end

else begin

cnt_num <= cnt_num;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt_seg <=3'd0;

end

else if(cnt_seg == 3'd5 && cnt_delay == CNT_20NS_MAX -1'd1)begin

cnt_seg <= 3'd0;

end

else if (cnt_delay == CNT_20NS_MAX -1'd1)begin

cnt_seg <= cnt_seg + 1'd1;

end

else begin

cnt_seg <=cnt_seg;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

sel_r <= 6'b111_110;

end

else if(cnt_seg == 3'd0 && cnt_delay == CNT_20NS_MAX -1'd1)begin

sel_r <= 6'b111_101;

end

else if(cnt_seg == 3'd1 && cnt_delay == CNT_20NS_MAX -1'd1)begin

sel_r <= 6'b111_011;

end

else if(cnt_seg == 3'd2 && cnt_delay == CNT_20NS_MAX -1'd1)begin

sel_r <= 6'b110_111;

end

else if(cnt_seg == 3'd3 && cnt_delay == CNT_20NS_MAX -1'd1)begin

sel_r <= 6'b101_111;

end

else if(cnt_seg == 3'd4 && cnt_delay == CNT_20NS_MAX -1'd1)begin

sel_r <= 6'b011_111;

end

else if(cnt_seg == 3'd5 && cnt_delay == CNT_20NS_MAX -1'd1)begin

sel_r <= 6'b111_110;

end

else begin

sel_r <= sel_r;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

seg_r <= 8'b1111_1111;

end

else begin

case (cnt_num)

4'd0: seg_r <= ZERO;

4'd1: seg_r <= ONE;

4'd2: seg_r <= TWO;

4'd3: seg_r <= THREE;

4'd4: seg_r <= FOUR;

4'd5: seg_r <= FIVE;

4'd6: seg_r <= SIX;

4'd7: seg_r <= SEVEN;

4'd8: seg_r <= EIGHT;

4'd9: seg_r <= NINE;

4'd10: seg_r <= A;

4'd11: seg_r <= B;

4'd12: seg_r <= C;

4'd13: seg_r <= D;

4'd14: seg_r <= E;

4'd15: seg_r <= F;

default: seg_r <= seg_r;

endcase

end

end

assign seg = seg_r;

assign sel = sel_r;

endmodule

Running result graph:

2. Verilog programming six digital tubes display 0-f in turn, the interval time is 0.5s

code show as below:

module seg_dynamic1(

input wire clk,

input wire rst_n,

output wire[7:0] seg,//选择哪一段亮

output wire[5:0] sel//选择哪一个亮

);

parameter MAX_0_5S = 25'd25_000_000;//0.5s

localparam CNT_20NS_MAX = 16'd50_000;//20ns

reg [7:0] seg_r;

reg [5:0] sel_r;

reg [24:0] cnt_0_5s;

reg [15:0] cnt_delay;

reg [3:0] cnt_num;

parameter ZERO = 8'b1100_0000,

ONE = 8'b1111_1001,

TWO = 8'b1010_0100,

THREE = 8'b1011_0000,

FOUR = 8'b1001_1001,

FIVE = 8'b1001_0010,

SIX = 8'b1000_0010,

SEVEN = 8'b1111_1000,

EIGHT = 8'b1000_0000,

NINE = 8'b1001_0000,

A = 8'b1000_1000,

B = 8'b1000_0011,

C = 8'b1100_0110,

D = 8'b1010_0001,

E = 8'b1000_0110,

F = 8'b1000_1110;

//0.5s倒计时

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt_0_5s <= 25'd0;

end

else if(cnt_0_5s == MAX_0_5S -1'd1) begin

cnt_0_5s <= 25'd0;

end

else begin

cnt_0_5s <= cnt_0_5s +1'd1;

end

end

//20ns倒计时

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt_delay <= 16'd0;

end

else if(cnt_delay == CNT_20NS_MAX -1'd1)begin

cnt_delay <= 16'd0;

end

else begin

cnt_delay <= cnt_delay +1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt_num <= 4'd0;

end

else if(cnt_num == 4'd15 && cnt_0_5s == MAX_0_5S -1'd1)begin

cnt_num <= 4'd0;

end

else if( cnt_0_5s == MAX_0_5S -1'd1)begin

cnt_num <= cnt_num + 1'd1;

end

else begin

cnt_num <= cnt_num;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

sel_r <= 6'b111110;

end

else if(cnt_0_5s == MAX_0_5S -1'd1)begin

sel_r <= {sel_r[4:0],sel_r[5]};

end

else begin

sel_r <=sel_r;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

seg_r <= 8'b1111_1111;

end

else begin

case (cnt_num)

4'd0: seg_r <= ZERO;

4'd1: seg_r <= ONE;

4'd2: seg_r <= TWO;

4'd3: seg_r <= THREE;

4'd4: seg_r <= FOUR;

4'd5: seg_r <= FIVE;

4'd6: seg_r <= SIX;

4'd7: seg_r <= SEVEN;

4'd8: seg_r <= EIGHT;

4'd9: seg_r <= NINE;

4'd10: seg_r <= A;

4'd11: seg_r <= B;

4'd12: seg_r <= C;

4'd13: seg_r <= D;

4'd14: seg_r <= E;

4'd15: seg_r <= F;

default: seg_r <= seg_r;

endcase

end

end

assign seg = seg_r;

assign sel = sel_r;

endmodule

The running result graph is as follows: