Clock frequency setting description of STM32F407 timer TIM3

clock tree

First it is an external clock, then it becomes 1MHz after /M, 366MHz after xN, and 168MHz after /P. At this time, it is the clock frequency of SYSCLK. After /1, it becomes the clock frequency of AHB HCLK=SYSCLK, and after /4, it becomes The clock frequency of APB1 is 42MHz, and after /2, the clock frequency of APB2 becomes 84MHz. TIM3 is mounted on APB1, but because of the /4 frequency division, it follows the clock tree if(APB1 presc=1){x1}else{x2 }, the TIM3 clock needs to be multiplied by X2 to become 42x2=84MHz.

Settings related

The MCU runs the startup file first. In the startup file, a clock initialization function will be run before the main function. The SystemInit

SystemInitfunction is as follows. The clock-related frequency division coefficients PLL_M, PLL_N, and PLL_P are defined in the file

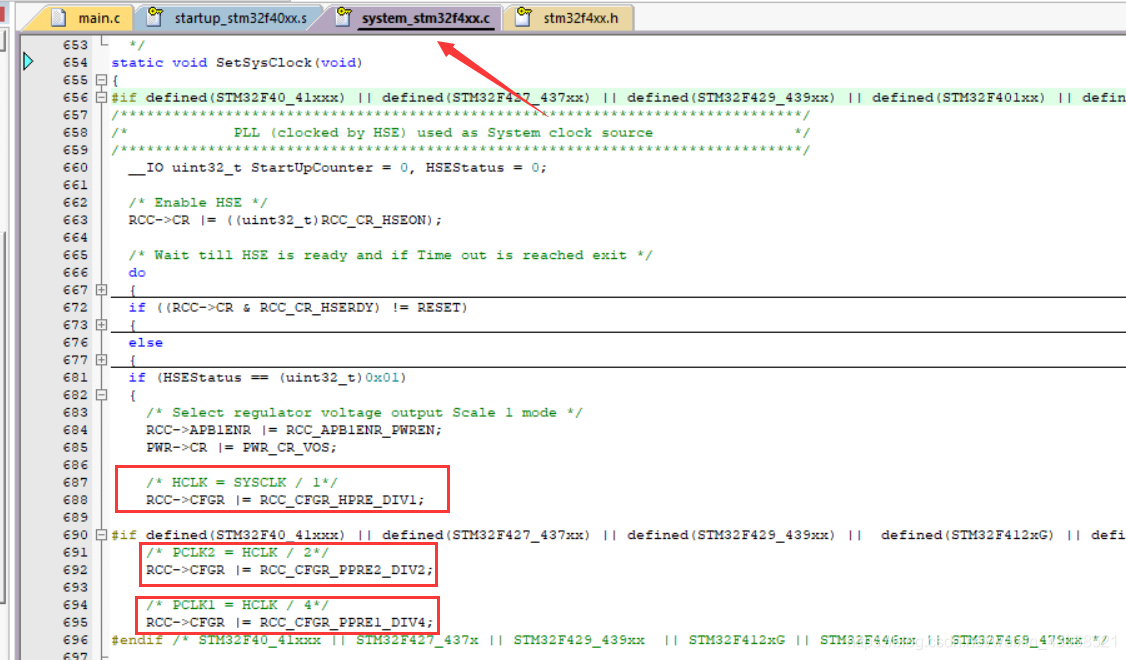

. The external clock frequency is defined in the file, here it is 25MHz (It should be consistent with the external crystal oscillator on the board) The middle function includes setting frequency division settings, as shown below, AHB clock is set to SYSCLK/1, APB1 is SYSCLK/4, APB2 is SYSCLK/2, TIM3 is mounted on APB1 , but the APB1 clock is divided by 1/4 on the basis of SYSCLK, which is consistent with the clock tree when the frequency division is not 1. The timer clock needs to be multiplied by 2, so the final TIM3 clock frequency is (SYSCLK /4)*2.system_stm32F4xx.c

stm32f4xx.h

system_stm32f4xx.cSystemInit