实验数据:之前的B1,B2,C级实验已经全部完成,得到的结果如下所示:

| C级得到的针脚号和存储结果 |   |

|---|---|

| B1得到的存储显示结果 |  |

| B2得到的队列存储结果 |  |

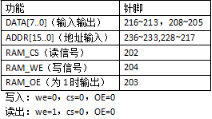

| C级实验只不过是要求我们找到针脚号并进行使用,实际上只要把HM62256芯片当做一个可读可写的RAM就可以进行设计了,我是用bdf进行设计,在设计过程中主要要注意tri8,即两个三态门的使用 |   |

| B1级实验要求我们通过tools定制一个可读可写的RAM(产生VHDL语言),生成模块后在bdf中进行线路连接,然后在小板子上实现即可 |  |

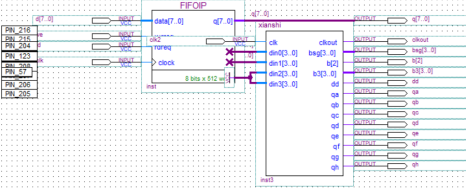

| B2级实验要求我们学会如何定制FIFO元件。FIFO元件是一个先进先出的队列式存储器,只要定制完毕(产生VHDL语言),生成模块后在bdf中进行线路连接,通过仿真了解其原理就可以进行使用 |  |

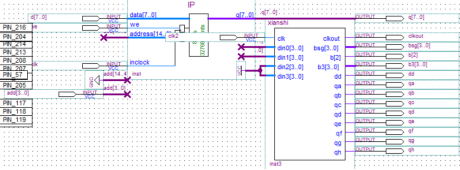

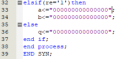

通过B,C级实验了解了基础的原理后,就可以开始A级实验,这里我和我的搭档对A级实验的要求有一点偏,之前我们认为A级是要求我们将FIFO元件与HM62256芯片相结合,即先将输入的数据存入FIFO元件中,然后再输出到HM62256芯片中进行存储,然后从HM62256芯片中读取存入的数据。但后来和一些同学商量过后发现应该是通过HM62256芯片来实现一个FIFO队列存储器,这也不难,只要通过VHDL编写一个模块用来控制地址就可以了,具体如下:

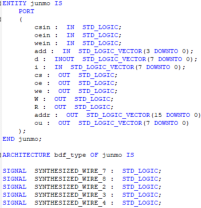

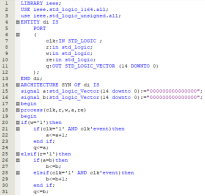

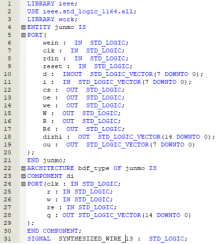

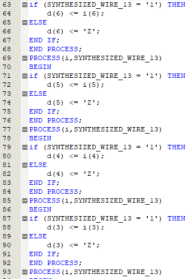

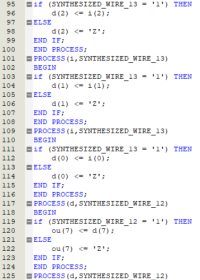

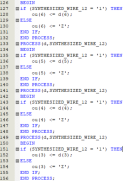

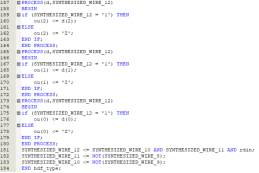

地址控制模块:

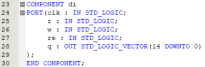

然后在顶层实体中调用即可:

可以看到之前我们对A级实验的理解基本上就是实验C和实验B2的结合体,所以只要做出来了前两个实验,A级的设计并不难。

而后来我们对A级的新的理解也不难,主要是生成队列一样的地址,用来控制数据的存储位置,最终实现一个队列型的存储器。

这里我设计的FIFO是上升沿进行触发,注意时钟信号最好选取时钟周期最长的152Q24这样方便我们进行实验和测量。

通过wein信号控制数据在时钟信号中写入HM62256芯片中,注意这里是按照地址的递增顺序写入到芯片;再通过rdin信号控制数据在时钟信号中从HM62256芯片读出,注意这里也是按照地址从低到高从芯片中读出;最终通过reset信号控制地址初始值归零。

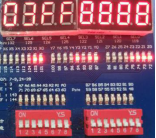

下载到实验箱进行检测,发现结果如下:

| 第一个存入FIFO |  |

第二个存入FIFO |  |

第三个存入FIFO |  |

|---|---|---|---|---|---|

| 第一个数据输出 |  |

第二个数据输出 |  |

第三个数据输出 |  |

可以看到实验结果与实验期望相吻合,证明实验成功,实验完成度100%

实验总结:

本次实验的主要特色在于对于存储器的学习和使用,但是由于时钟频率的原因,恐怕很难看到结果,这里也是可以拓展的地方,希望我在五一假期中可以思考到一种简单明了的方法可以解决这个问题(PS已经解决了,可以用152号时钟进行解决,只是要求操作的时候要控制每次操作的时机)。

这次实验我做地特别快,可能是因为我也比较着急,最近的事情太多还需要赶一篇论文,所以整个实验是在老师布置了实验要求的当天晚上完成的,但可以说我并没有偷工减料,而是仍旧做出了我能够做出来的水平,实验大体上的知识点已经完备,但部分细节还需要打磨加工,计划在我完成了竞赛论文后用五一假期再研究一下,并冲击一下S级。