静态存储器

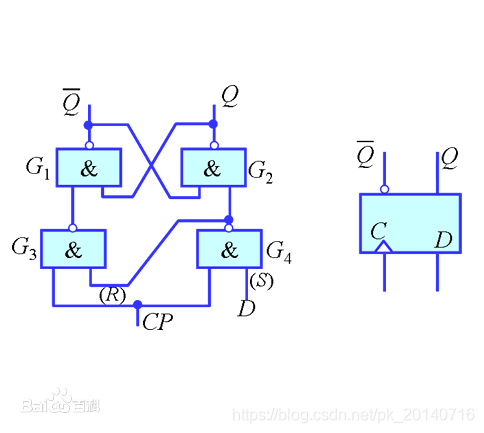

D型触发器

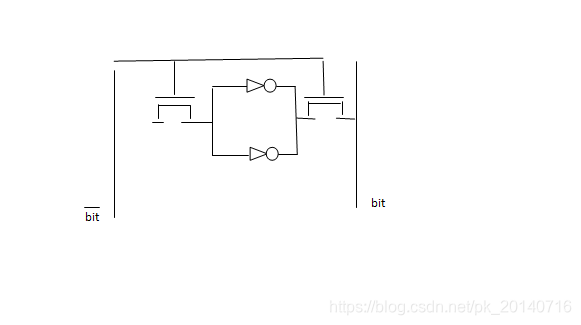

静态存储器存储单元

- 写

- 在位线上设置使(bit=1, =0)

- 使字选通

- 读

- 使bit和 都充为高电平Vdd

- 使字线选通

- 根据触发器的状态,将使其中一条位线电平 为低

- 放大器感知bit和 的变化,读出存储器的值

静态存储器典型组织方式

随机访问

静态存储器

速度快

存储密度低,单位面积存储容量小

数据入/出共用管脚

能耗高

价格高

与动态存储器比较

| SRAM | DRAM | |

|---|---|---|

| 存储信息 | 触发器 | 电容 |

| 破坏性读出 | 非 | 是 |

| 需要刷新 | 不要 | 需要 |

| 送行列地址 | 同时选 | 分两次送 |

| 访问速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 发热量 | 大 | 小 |

| 存储成本 | 高 | 低 |

程序局部性原理

for(i=0;i<1000;i++)

{

for(j=0;j<1000;j++)

{

a[i]=b[i]+c[i];

}

}

if err{...}

else for(i=0;i<1000;i++)

{

for(j=0;j<1000;j++)

{

e[i]=d[i]+a[i];

}

}

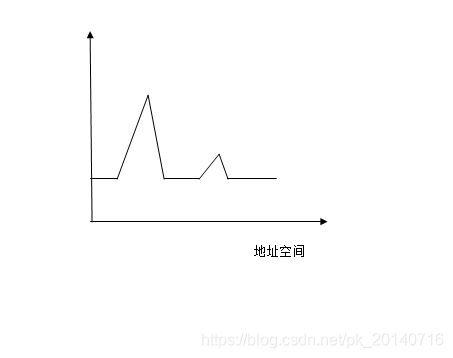

数据流访问的内部性

指令访问的局部性

不同的程序段可能访问不同的内存空间。

程序在一定的时间段内通常只访问较小的地址空间

两种局部性:

时间局部性

空间局部性

层次存储器系统

使用高速缓存存储器cache来提高CPU对存储器的平均访问速度

时间局部性:最近被访问的信息很有可能还要被访问。

将最近被访问的信息项装入到cache中。

空间局部性:最近被访问的信息临近的信息也可能被访问。

将最近被访问的信息项临近的信息一起装入到cache中。

高速缓冲存储器cache

- 定义

- 设置于主存与CPU之间的存储器,用高速的静态存储器实现,缓存了CPU频繁访问的信息。

- 特点

- 高速:与CPU的运行速度基本匹配

- 透明:完全硬件管理,对程序员透明

要解决的问题

- 地址之间的映射关系

如何根据主存地址得到cache中的数据 - 数据之间一致性

cache 中的内容是否已经是主存对应地址的内容 - 数据交换的粒度

cache中的内容与主存内容以多大的粒度交换 - cache内容装入和替换策略

如何提高cache的命中率?