超级计算机:

硬件通过每条指令的有序执行(软件)来发挥作用。

硬件提供了接口给上层的软件(提供一系列指令集),软件通过利用一系列指令集能够完成一定功能。例如系统软件,利用硬件的资源完成人机交互界面。下面是简单的逻辑图:

应用软件也调用系统软件提供的接口,利用系统软件的资源实现自己的功能。

程序员的角度看待计算及系统的抽象:

高级语言或者汇编语言,必须有一个编译器,将其编译成机器可执行的二进制文件,这样程序才能被机器识别,让机器运作。

操作系统能够管理软硬件的资源。

DOS系统是(win)操作系统的一部分。

上图的这个实现乘法指令指的是逻辑实现。

我们现在使用的现代计算机(都是存储程序结构的计算机)也称作冯诺依曼结构计算机,核心理论是,计算机的数据,程序都是以二进制的形式存放在计算机当中。

指令位于内存当中,通过地址寻访(操作码指明指令要做什么操作,操作码存于内存地址中,地址码指明操作码的地址)。有点C语言的味道了。程序存储在存储器当中。

可以对以上6个内容提出质疑,锻炼批判思维,但前提是一定要有根据。

冯诺依曼结构计算机5大部件:

实线表示数据流向通路,虚线表示控制和状态反馈。

如果以上图设计的计算机:

运算器:算术运算,逻辑运算 (运算器负载太高会成为系统的一个瓶颈)。

改进成以存储器为核心:

层次还不够清晰,再改进形成现代计算机框图:

主存(内存条)和CPU构成主机,辅存(硬盘等)和输入输出设备构成I/O设备。所以硬盘是I/O设备之一。

思考:生活中的问题能否用计算机解决,能要怎么做。

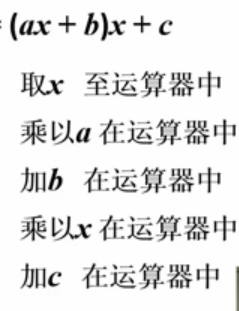

它在计算机中的运算顺序以及操作指令是这样的:

(一个操作数要保存在累加器当中,一个则要保存在内存当中。)

1.乘法指令

2.加法指令

3.从内存中取出操作数指令

4.计算最终结果保存到存储器中指令

5.打印指令

6.停机(停止)指令

这6条指令指挥计算机运行计算,所谓编程,和这些指令就类似,操作计算机进行运算。一条条指令集合组成一个程序。

PS:取x是放在运算器的累加器(ACC)当中。

简化后,只需要5步:

指令格式:

操作码表示执行什么操作,地址码表示内存地址单元,里面保存操作数。可以看到每条指令(操作码)都是二进制的。

存储器的作用,保存数据(计算结果等需要保存的都要放入存储器中供系统以后使用)和指令(平等的)。

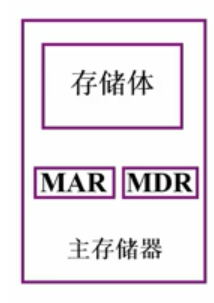

存储器(内存或者主存)的基本构成:

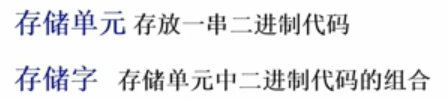

存储字长:存储单元里面二进制代码的位数(长度)。每个存储单元赋予一个地址。存储单元按地址寻址。

存储单元保存的数据就是一个存储字。

存储体可能存放了很多指令或者数据(0,1代码),这些数据或者指令被分成了若干个存储单元,

MAR(存储器地址寄存器):对存储单元是按地址访问的,CPU想取出指令或者数据,就要寻址,那么MAR就是保存了(二进制)存储单元的地址。反映了存储单元的个数。

MDR(存储器数据寄存器):要保存的是:刚刚从存储体取出来的数据或者要保存到存储体的数据。(百度百科:将要写入到计算机主存储器(例如:RAM)的数据,或由计算机主存储器读取后的数据。)

所以MDR的长度和存储单元的长度是相同的,反映了存储字长 。

假设一个MAR是4位的,MDR是8位的(位数指处理数据的长度),那么0000~~1111会有2的4次方个地址(要么0要么1,排列组合为16)。那么

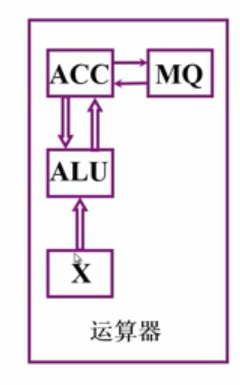

运算器结构:

ALU:执行各种算术和逻辑运算操作的部件,亦称算术逻辑部件。 通常是个组合电路,若输入撤销了,那么输出结果也不会被保存,为了让ALU能对结果进行保存,所以需要在ALU输入端加上寄存器,寄存器保存参与运算的数据。那么就需要两个寄存器作为输入数据的保存设备。其中一个就是ACC(累加器)专门用来存放操作数或运算结果,另一个称作X(有AX,BX,CX,DX之分,数据寄存器,是用来暂时存放计算过程中所用到的操作数、结果和信息,功能与累加器有点类似),如果当运算的结果将会出现溢出(执行乘法时候),还要加一个MQ乘商寄存器。

ACC:累加器

MQ:乘商寄存器

X:数据寄存器

运算器执行运算时,数据存放的位置:

做加法时:

初态是被加数已经存放在了ACC中,指令把在内存中的M取出来放入X寄存器中,两个数的相加在ALU中完成,然后ALU输出到ACC,保存在ACC中。

减法同加法:

乘法:

它的步骤是这样的:首先,初态被乘数放在了ACC中,第一步M乘数从存储器拿出来放到MQ寄存器,第二步ACC中的被乘数放到X寄存器(这一步是运算必须的,都要放在X寄存器),实际上第一步和第二步先后顺序也可以互换,第三步清空ACC,第四步X寄存器和MQ寄存器中的值放入ALU运算器中运算,然后得出的结果高位放在ACC,低位放在MQ。(PS:计算机的乘法和除法是通过累加、减和移位实现的)以上所有的步骤均有 控制器 控制指挥来执行。

除法:

初态ACC中有被除数,将除数M放入X寄存器,ACC和X的运算在ALU中,然后结果的余数保存在ACC,商保存在MQ中。

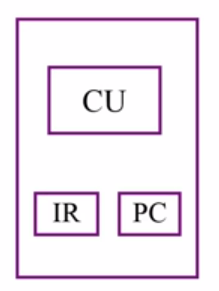

控制器能控制指挥运算步骤执行,下面讲解控制器:

它的功能:

1.解释指令。取址,分析,取操作数,真正执行指令以及保存操作数一系列过程。

2.保证指令按顺序执行。

上图全过程:1.把内存单元保存的指令取出来送到控制器当中。2.把操作码部分送到控制器进行分析。3.由控制单元控制相应的执行部件完成操作。

对应功能的硬件结构:

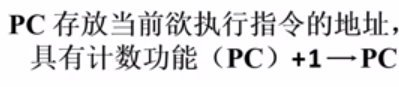

1.取指令,就要知道对应是指令的地址,指令是保存在内存单元当中,因此有个寄存器叫做(PC)程序计数器

由于指令是连续存放在内存单元中,执行完成后地址数要加1 ,取下一个指令,所以PC是具有计数功能的,为下一次取址做准备。

百度百科:

程序计数器是用于存放下一条指令所在单元的地址的地方。当执行一条指令时,首先需要根据PC中存放的指令地址,将指令由内存取到指令寄存器中,此过程称为“取指令”。与此同时,PC中的地址或自动加1或由转移指针给出下一条指令的地址。此后经过分析指令,执行指令。完成第一条指令的执行,而后根据PC取出第二条指令的地址,如此循环,执行每一条指令。

2.分析指令(IR):

![]() 指令寄存器(IR,Instruction Register),是临时放置从内存里面取得的程序指令的寄存器,用于存放当前从主存储器读出的正在执行的一条指令。

指令寄存器(IR,Instruction Register),是临时放置从内存里面取得的程序指令的寄存器,用于存放当前从主存储器读出的正在执行的一条指令。

3.执行指令由CU发起,CU控制器决定怎么执行。下面是控制器结构:

那么计算机系统构建:

取数指令时系统执行如下:

首先是要取得存储体中的操作指令(指令和操作数据都保存在了存储体中),那么(在控制器的作用下)

1.PC要去获得指令地址,并保存。

2.那么存储体的MAR记录着指令地址。

3.根据MAR中的地址,访问到存储体中的指令。

4.把要从存储体中输出的指令存于MDR。

5.主存取出来的正在执行的指令就保存到IR指令寄存器。

6.IR将操作码部分给CU分析,CU就会知道要执行什么样的操作,并发出控制信号来完成指令要求的操作。

7.在CU的控制下,IR指令寄存器去取操作数,---->MAR------>存储体-------->MDR.

8.这个时候MDR中的操作数在控制器的作用下放入运算器的ACC中去保存。

存数指令系统的执行情况:

存数要把ACC当中的数存入存储体当中。但要执行这个指令时候,也要先去存储体拿到这条指令。所以明显得出,不管你是存还是取,都要先去存储体中拿到相对应的指令才可以进行操作。所以和取数时前5步是重叠的。

6.在CU的控制下,IR去访问MAR的地址码,并告诉存储体,数据要存在哪个单元。

7.CU控制下,ACC的数据存放在MDR中。

8.最后由MDR存入存储体。

PS:PC在执行完取指令操作后就可以进行调整了。

控制器必须要知道程序的首地址(保存在PC中),然后启动程序,实质上就是执行所有指令的一个过程,因为程序是指令的集合。接下来就是以上所谈到的过程。

衡量计算机硬件水平:

PS:机器字长实质上就是平时所说的多少位操作系统。

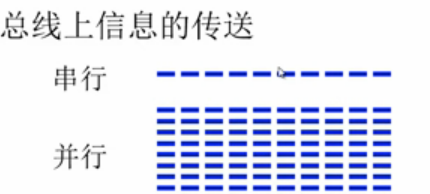

总线:

总线是信号的公共传输线,各个设备都可以链接到总线上,在任何时刻,只能有一对部件或者设备占用着总线资源,其它组件必须要等着占用设备释放,才可以使用总线(跟计网的共享介质广播有点类似)。这种结构简单,可拓展性好。

并行,发送和接收方接收多位数据,意味着需要的数据线多,如果传输距离长,线就必须平行,实际上很难做到,这样就会造成对传输的干扰。所以并行适合短距离传输,在机箱内传输。串行适合长距离,机器之间或者更远设备间传输。

总线造成的瓶颈:

改进:

再改进:

PS:主存工作时只能使用其中一条,现代技术还没有好的办法让主存在存储总线和系统总线同时工作。

数据总线一般是小于等于机器子长,比如64位机器,你做成8位的总线那么一次运算你就得做8次传输。

总线生产有个约定,这就是总线的标准:

上图第二列是传输位数(机器字长)。注意上图中带宽有两种单位,MB带宽是指文件流传输的速度,Mb带宽是数据率。MB/8等于Mb。

由于主存的发展速度跟不上CPU,所以主存和CPU之间加了个小容量高速度的Cache。这个cache能缓存主存的数据,cpu每次就到cache去取数据,指令等。

PS:DMA总线:直接存储器访问总线,外部设备直接访问系统内存。

总线控制:

流程可能是这样的:

I/O设备1,2都发起了总线控制请求BR,控制部件会发出BG进行确认,确认到了设备1是请求方(虽然设备1,2都发出了请求,但设备1是BG查询到第一个设备,所以优先级是设备1最高。因此这里的优先级跟设备一开始的连接方式直接相关)。那么总线控制权给到了设备1,设备1就发起BS忙的信号。所以如果有个设备排的非常后,可能永远得不到应答。

和链式查询有些类似:

设备地址是用来总线判优的,设备发出占用请求BR后,计数器启动,0时就去查看地址为0的设备,发现到1时,设备1发出的请求,那么设备1发出BS总线忙。

链式和计数器方式查找到序号比较高的设备时候,会很慢。所以独立请求方式改变了这个缺点:

在三个查询方式中,链式对电路故障是最敏感的,因为这会直接影响到控制部件对设备的授权线。

存储器:

电脑内存是半导体材质的,磁盘是磁表面材质的,磁盘中有同心圆,扇区就是这个同心圆的部分,可以存几百几千的数据或者文件。磁表面存储器存储信息是不易失的。还有一种就是光盘存储器。

RAM就是随机存储器,可读可写,用户所有的程序,数据就可以保存在RAM。

ROM就是只读存储器,系统数据参数(防止随意修改)就可以保存在上面。

U盘就是flash memory做的,是半导体材质(半导体存储器),速度介于磁盘和内存。flash memory还可以做高性能硬盘。

内存和(ssd)磁盘之间还可以用flash memory作为辅助存储器(磁盘)的缓冲。SSD固态盘的材料就是flash memory。

高速缓冲存储器cache(用静态RAM制作),是放在内存和CPU之间的,速度比内存还快,作为缓冲。

而且这个金字塔越往下价格越便宜。

程序的执行是在主存和CPU当中的,所以它们之间的通信非常频繁。但主存的容量是非常小的,所以很多数据和文件都要辅存来存放。

因此主存和辅存之间的通信也很频繁。在应用程序员的角度来看,根本不用关心它们的通信是怎么实现的。

缓存和主存主要解决访问速度问题,主存和辅存主要解决容量问题。(平时C语言指针是逻辑地址)主存和辅存构成的整体叫做虚拟存储器,然后就出现了虚拟地址(逻辑地址)。物理地址就是由逻辑地址转换得来的。主存存储使用的真实地址是物理地址。

主存储器:

16进制和二进制的对应关系:

16进制的每一位对应4个位的二进制:如0001对应16进制的1。

12345678H是一个16进制数,H=Hex代表16进制的意思

12345678H=0001 0010 0011 0100 0101 0110 0111 1000,一共占用4(内存是4*8)个字节,所以在内存里占用4个存储单元。内存存储是低位在前高位在后,在内存中看到的存储形式就是78H 56H 34H 12H。

一个数据占4个字节,每4个字节的存储方式:

上图中的字地址(第一行)0~3,第二行4~7,以此类推。所以0,4,8就这样来。

一个容量为16k*32位的储存器,其地址线和数据线的总和是多少?

32位是机器字长,所以需要32条地址总线。因为一个地址总线存放一个字节的地址,所以16K容量等于2的14次方,也就是14根地址总线。14+32=46.

带宽广义上来讲:就是传输的流量,单位可以 是位/秒和字节/秒。

首先16K X 1要变成64K X 8位的存储器,那么就先需要8根数据总线(每一条数据总线只传输一个比特位)。所以上图中有8片芯片。然后需要64K的地址总线也就是16乘以4,所以要4组芯片组。

线选法,如果有20根地址线,用一个译码器的话,输出是1M条线(1000*1000)。所以:

采用重合法,译码器输出只有2K(1000+1000),更适合做集成芯片。

WE:读写控制信号,低电平写操作,高电平读操作。

CS:片选信号,低电平的时候上图21114才会被选中。

上图中可以看出有10个地址线(A0~~A9),也就是1K个存储单元,4个数据线(I/O),也就是4位信号。

这个芯片是1K X 4,