电路设计中常常需要延迟上电的方法,本文和大家一起简单的探讨下这个问题。

电源监控

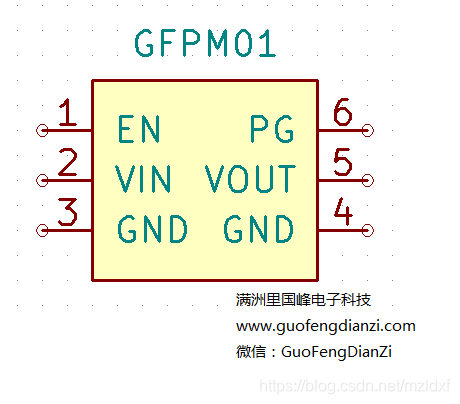

在很多电路中需要对供电电源监控,当电源的电压低于某个数值时,系统很有可能就不能正常工作了,现在很多电源管理模块都提供这样的引脚,通常名为Power Good,简称PG,如图1所示:

图1:电源模块样板[1]

有电源供电电压监测功能,当输出电压低于预计数值的90% 时(根据厂家不同,数值略有不同),power good引脚输出低电平(或者高电平,看器件)防止系统供电出错。

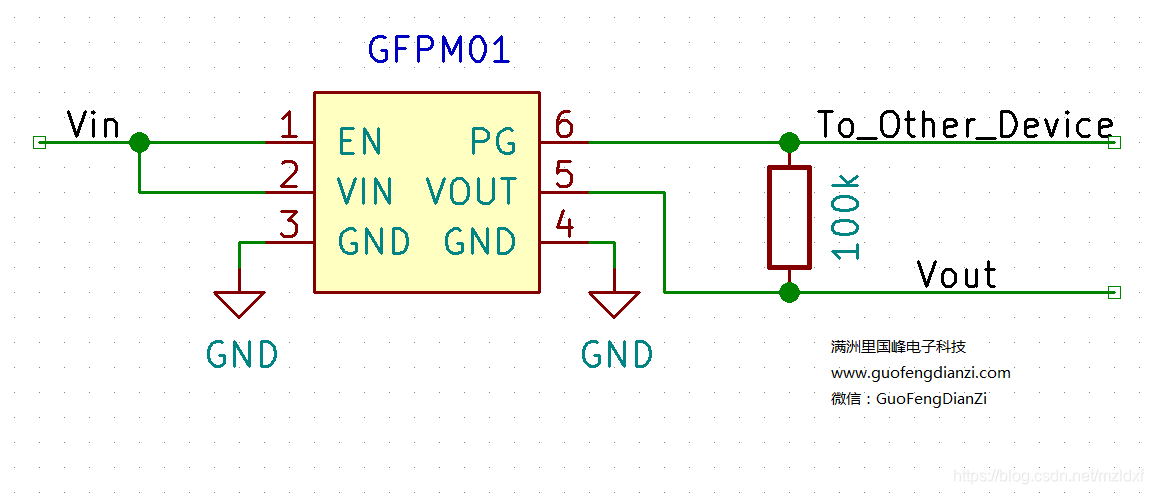

有些器件的PG引脚是漏极开漏电路,则需要在片外加上拉电阻,如图2所示:

图2: Power Good 引脚加上拉电阻[1]

上电顺序

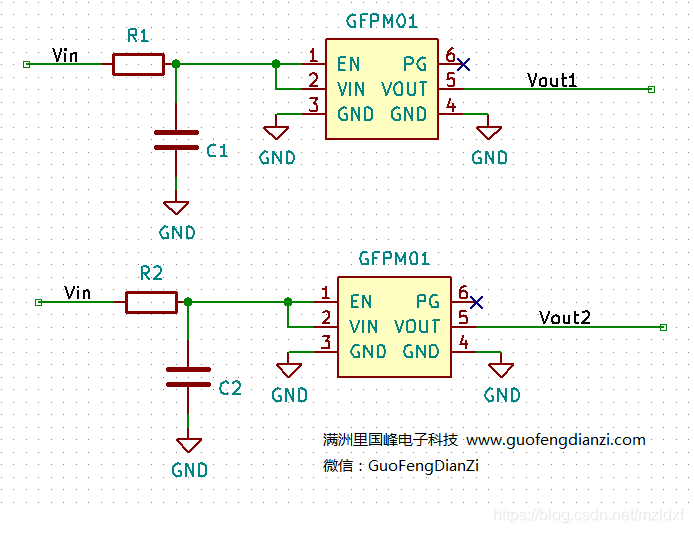

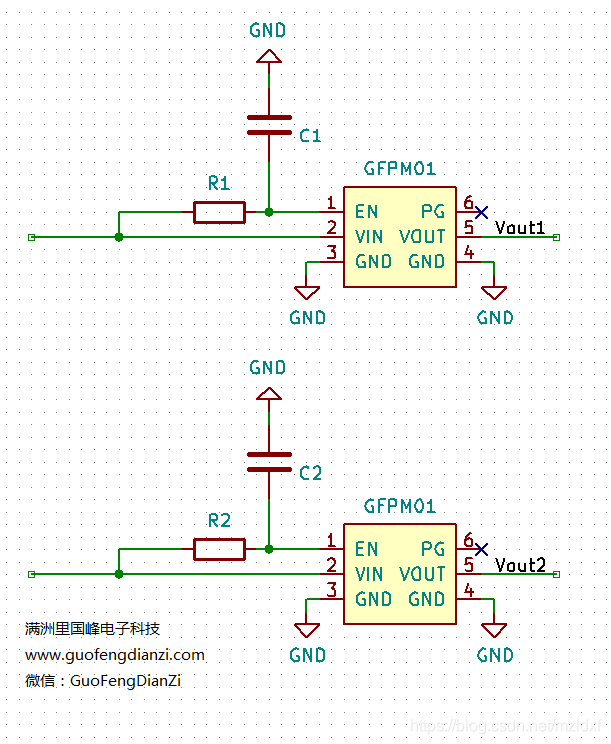

在负责的电路中,不同的器件常常需要有不同的上电顺序,比如有些FPGA需要先给3.3V的内核供电,至少20ms后才给5V的IO口供电,以避免器件的损毁。在射频电路和模拟电路中也有些这样的需求,例如需要Vout1先上电,Vout2后上电,最简单也是最容易想到的是使用RC延时电路,方案1:

图3:在电压输入端使用RC电路

方案1可以设置R1,C1,R2,C2的数值以完成不同的延时,从而可以改变上电上电顺序,但是有缺点,因为在供电回路中串联了电阻,如果是给功放等大功率的器件供电,会产生很大的损耗。

方案2,利用电源模块的使能引脚,现在的电源管理芯片都有使能引脚,在是能引脚处加RC电路可以完成延时:

图4:在使能输入端使用RC电路

在使能端使用RC电路可以满足一些不精确控制延时的场合。在精确控制上电顺序的场合,可以使用专用的集成电路芯片,欢迎大家咨询电源管理方案。

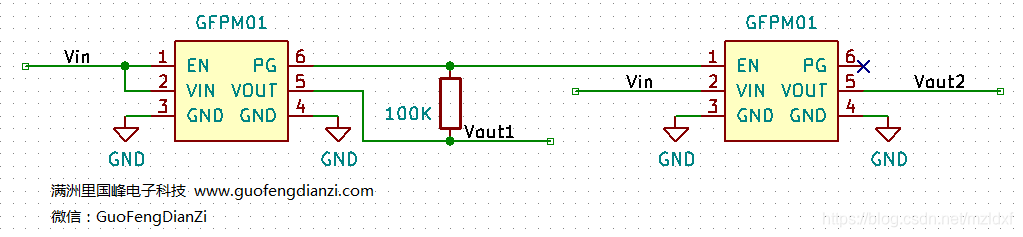

方案3:利用电源监测引脚PG和使能引脚,完成上电顺序的控制,如图5所示,先上电的Vout1在完成上电后,PG引脚会产生一个高电平,该高电平使能下一个要上电的模块输出Vout2。

作者:伏熊(专业:射频芯片设计、雷达系统、嵌入式。欢迎大家项目合作交流。)

微信:GuoFengDianZi

[1] https://item.taobao.com/item.htm?spm=a2oq0.12575281.0.0.25911debZibwwe&ft=t&id=612838123547