默认情况下,所有约束都处于启用状态,并且在随机化过程中,SystemVerilog约束求解器将考虑所有约束。 在随机化过程中不考虑禁用的约束。

可以通过constraint_mode()启用或禁用约束。

Syntax

Constraint_mode()既可以作为任务也可以作为函数调用。

当作为任务调用时,该方法不返回任何内容。 该任务提供了一个输入参数来打开或关闭给定的约束。 当作为函数调用时,该方法返回给定约束的当前状态。

// Called as a task

class_obj.const_name.constraint_mode(0); // Turn off the constraint

class_obj.const_name.constraint_mode(1); // Turn on the constraint

// Called as a function

status = class_obj.const_name.constraint_mode(); // status is an int variable to hold return value

constraint_mode()是一个内置方法,不能被覆盖!

方法

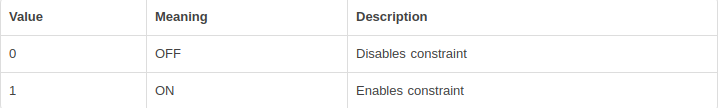

下表显示了何时将constraint_mode称为任务时,参数输入的每个值指示什么。

例

在下面的示例中,我们将看到constraint_mode()对它的约束有什么影响。

class Fruits;

rand bit[3:0] num; // Declare a 4-bit variable that can be randomized

constraint c_num { num > 4; // Constraint is by default enabled, and applied

num < 9; }; // during randomization giving num a value between 4 and 9

endclass

module tb;

initial begin

Fruits f = new ();

// 1. Print value of num before randomization

$display ("Before randomization num = %0d", f.num);

// 2. Call "constraint_mode" as a function, the return type gives status of constraint

if (f.c_num.constraint_mode ())

$display ("Constraint c_num is enabled");

else

$display ("Constraint c_num is disabled");

// 3. Randomize the class object

f.randomize ();

// 4. Display value of num after randomization

$display ("After randomization num = %0d", f.num);

end

endmodule

Simulation Log

ncsim> run

Before randomization num = 0

Constraint c_num is active

After randomization num = 8

ncsim: *W,RNQUIE: Simulation is complete.

现在,让我们尝试在尝试使变量随机化之前使用constraint_mode()禁用约束。

module tb;

initial begin

Fruits f = new ();

$display ("Before randomization num = %0d", f.num);

// Disable constraint

f.c_num.constraint_mode(0);

if (f.c_num.constraint_mode ())

$display ("Constraint c_num is enabled");

else

$display ("Constraint c_num is disabled");

// Randomize the variable and display

f.randomize ();

$display ("After randomization num = %0d", f.num);

end

endmodule

Simulation Log

ncsim> run

Before randomization num = 0

Constraint c_num is disabled

After randomization num = 15

ncsim: *W,RNQUIE: Simulation is complete.

请注意,关闭约束会使求解器选择变量支持的任何值,而不是将值限制在约束中指定的范围内。

如果在不存在的约束上调用constraint_mode()方法,则将导致编译器错误。

module tb;

initial begin

Fruits f = new();

f.c_does_not_exist.constraint_mode(1);

end

endmodule

Simulation Log

f.c_does_not_exist.constraint_mode (1);

|

ncvlog: *E,NOTCLM (testbench.sv,11|21): c_does_not_exist is not a class item.

参考文献:

【1】https://www.chipverify.com/systemverilog/systemverilog-disable-constraints