#来自学渣的问候~

#没想到菜鸡还有被催更的一天,瑟瑟发抖~

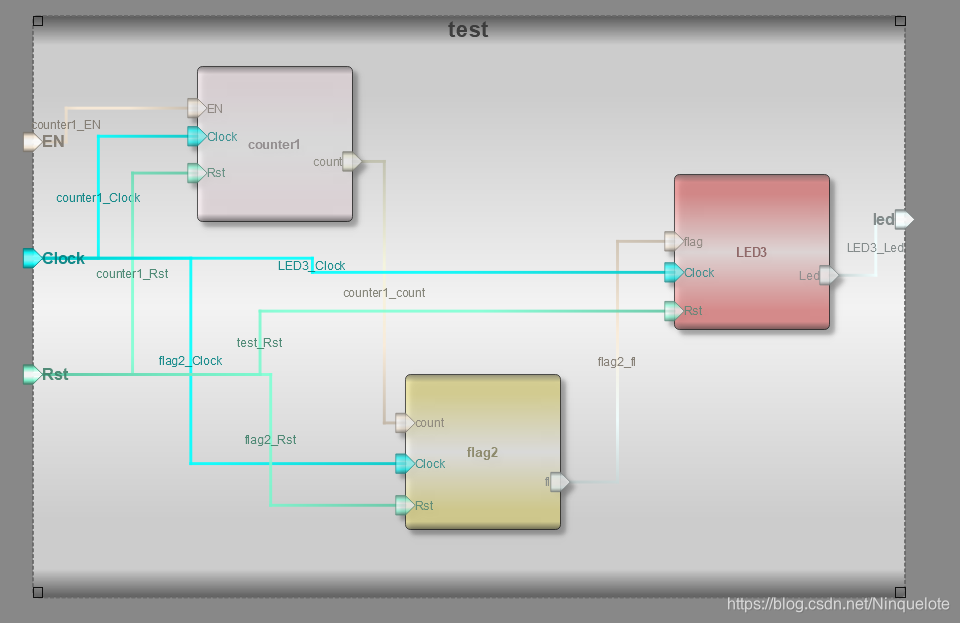

之前两个有关 Robei 的博客,都是利用软件里给好的现成模块,做的组合逻辑的仿真,所以这一个,我们尝试用时序逻辑来做一个简单的计数器。

在我学FPGA的时候,入门的第一个Verilog程序,就是点亮流水灯,这个过程就是一个简单的计数器。流水灯的闪烁时间,换下一个灯的时间,都是依靠每次计数器计时完成之后的判断来实现的。在Verilog里,就是定义一个reg count[x:0](x是自定义的数),然后不断让这个寄存器自加,当满足要求时,改变灯的状态,再把变量置0,重新开始。

Robei EDA的仿真过程如下

- count计数模块

新建一个module的文件

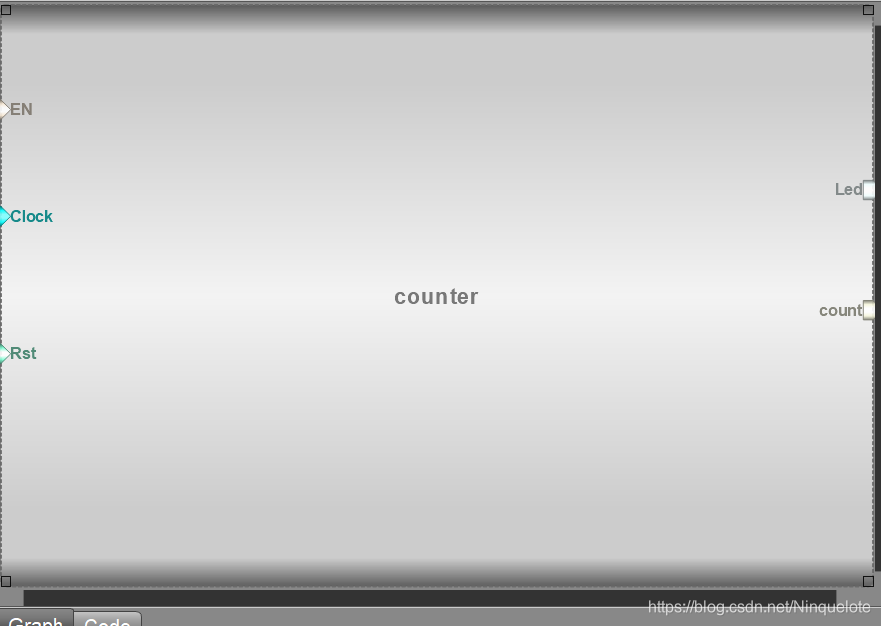

给模块配置上端口,并修改

给模块配置上端口,并修改port的名称

Robei的教程里,很喜欢给模块和仿真提供Enable使能信号,但是如果是自己写代码的话,顶层模块是很少写使能的,除非是按键触发,或者下层模块的状态变化。但是它官方的教程有,所以写就写了。

而count在这里为了有计数这个过程,就把它作为一个输出IO口,在实际的代码里,顶层模块基本不会有计数器的IO,大部分都在下层模块里。

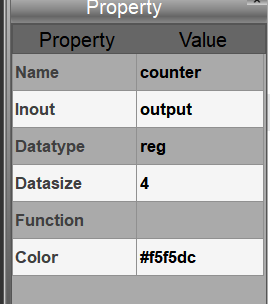

点击count和Led的管脚,在右侧的Property性质那里,修改Datetype里的wire为reg,Datesize为4或者[3:0],意思是4位寄存器,最大可以计数16,对于Led 来说则是闪烁的4个灯。(如下图)

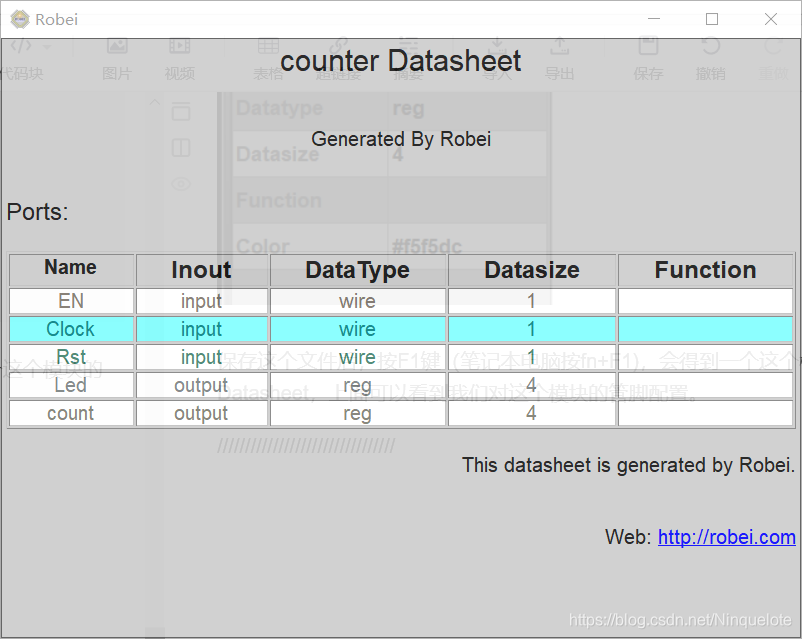

保存这个文件后,按F1键(笔记本电脑按fn+F1),会得到一个这个模块的Datasheet,上面可以看到我们对这个模块的管脚配置。

因为Robei里,一个模块只支持一个always块,意味着如果你写了一个程序,里头有多少个always,你就要写多少个模块(是不是特别惨)。

因为Robei里,一个模块只支持一个always块,意味着如果你写了一个程序,里头有多少个always,你就要写多少个模块(是不是特别惨)。

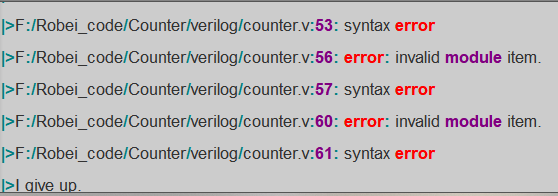

如果你在一个模块里,写了两个always,就会出现这样的报错。

-

flag状态改变模块

这样子:

这块的

这块的count的propert要把Datetype设置成wire,但是Datasize还是设置成4。 -

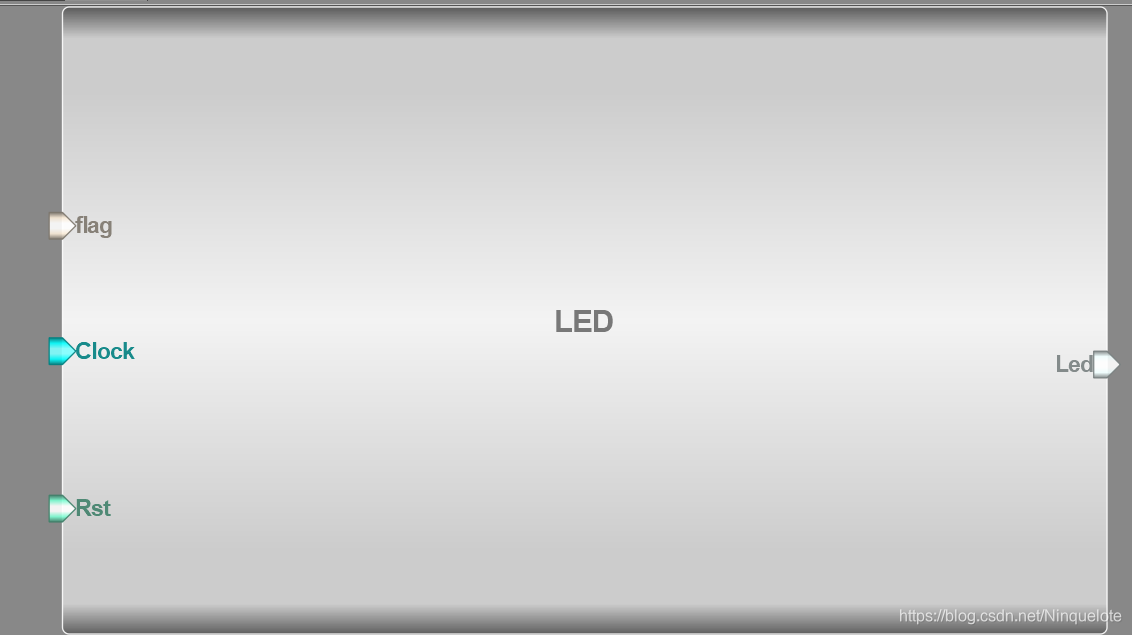

LED模块

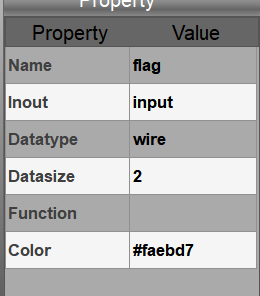

flag这里也和上面的count一样,property要修改设置。

flag这里也和上面的count一样,property要修改设置。

代码编写

- 计数器模块

对应着counter这个module。(因为CSDN不支持Verilog的高亮,这里的高亮是C的)

always@(posedge Clock or negedge Rst)

begin

if(Rst ==1)

begin

count <= 4'b0;

end

else if(EN ==1)

begin

if(count == 4'd15)

begin

count <= 4'b0;

end

else

begin

count <= count +1;

end

end

end- 状态变化模块

always@(posedge Clock or negedge Rst)

begin

if(Rst == 1)

begin

fl <= 2'b00;

end

else

begin

if(count == 4'b1111)

begin

if(fl ==2'b11)

begin

fl <= 2'b00;

end

else

begin

fl <= fl + 1;

end

end

else

fl <= fl ;

end

end

这个模块是用来给LED做状态改变的,计数器每计满一次,就换一个灯。(其实这里有很多种写法,直接根据计数器的计数值改变的也有,这里只是我喜欢用这个方法)

5. LED闪烁模块

always@(posedge Clock or negedge Rst)

begin

if(Rst ==1)

Led <= 4'b0;

else

begin

case(flag)

2'b00: Led <= 4'b0001;

2'b01: Led <= 4'b0010;

2'b10: Led <= 4'b0100;

2'b11: Led <= 4'b1000;

default: Led <= 4'b0000;

endcase

end

end用case来做一个巨简单的状态机(虽然是状态机的原理,但太简单了,连状态机都不如)

创建激励文件

之前的博客讲过激励文件的创建方法了,这里的话,只需要注意一下,输出的那个LED的配置,略有不同。(wire的类型)

之前的博客讲过激励文件的创建方法了,这里的话,只需要注意一下,输出的那个LED的配置,略有不同。(wire的类型)

而激励文件的代码,主要是提供使能EN的信号,时钟Clock的信号,还有复位信号Rst,不过使能和复位只要给一次就够了,因为在这个仿真里,不需要它。

initial begin

Clock = 1;

Rst = 0;

EN = 0;

#5 Rst = 1;

#10 Rst = 0;

#10 EN = 1;

#1500 EN = 0;

#5 $finish;

end

always begin

#5 Clock=~Clock;

end这个#5代表5ms的时间,可以随意配置。

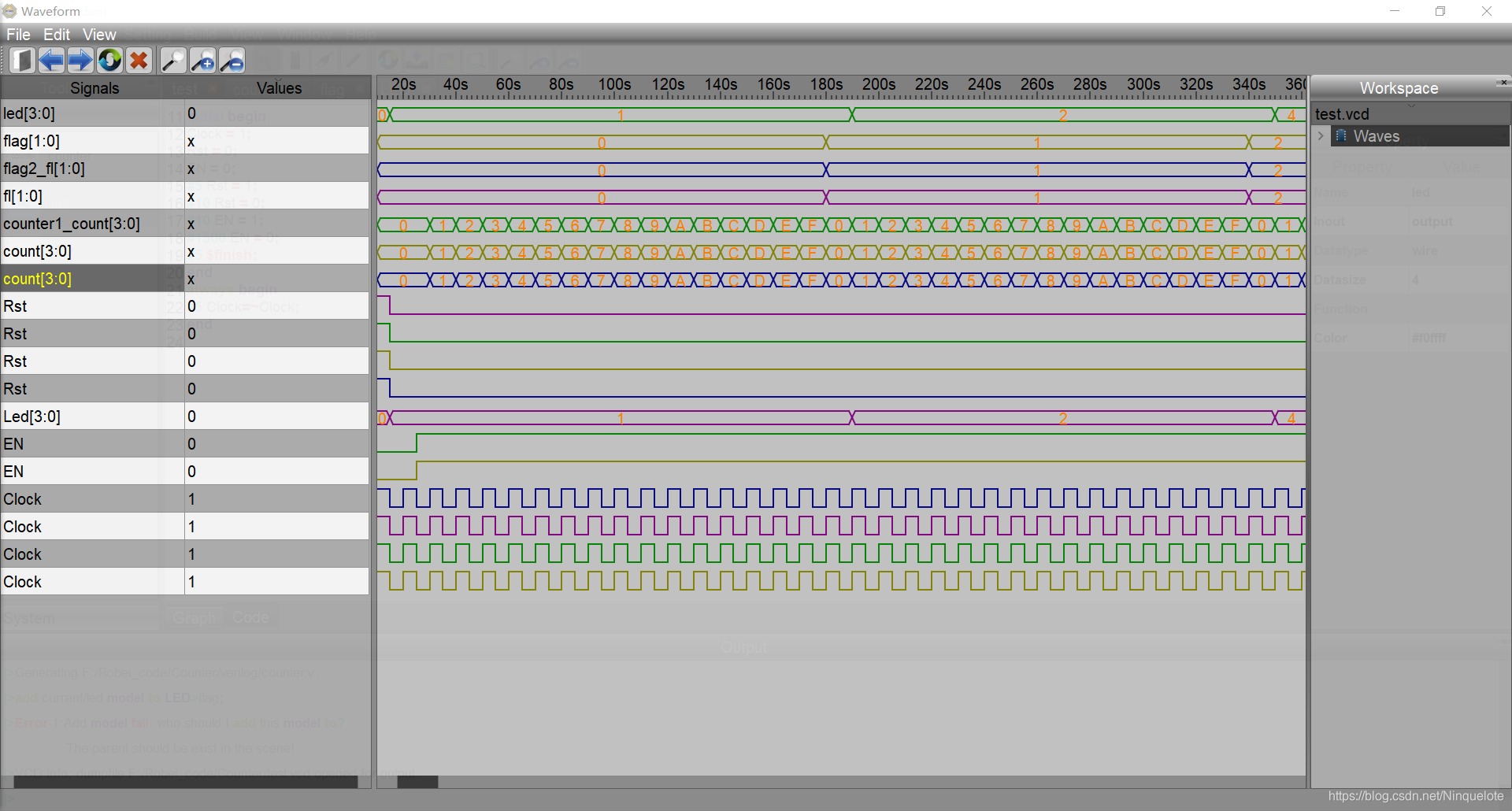

仿真波形图如下:

LED的显示是这样的,如果实际用开发板操作,就能够看到流水灯点亮。

LED的显示是这样的,如果实际用开发板操作,就能够看到流水灯点亮。

(写完撒花,这是我写的第一个关于时序逻辑电路的Robei EDA 仿真,时序逻辑也是FPGA里用到最多的。下一个,来写一个PWM或者DDS吧)

因为目前没有办法做vivado和 Robei的联合调试(其实是垃圾的我还没借到板子),所以只能写仿真能看得出来是那么个东西的博客。(哭咧咧~)