逻辑门电路简易实现 - 异或

----- 异或 -----

异或门

| 输入A | 输入B | 输出 |

|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

规则:同则0,异则1

设计思想:

先研究异或的基本逻辑,在设计由基本逻辑门构成的异或门电路,最后依此设计电路

异或基本逻辑

A^B = ~ [A · B + (~ A) · (~ B)]

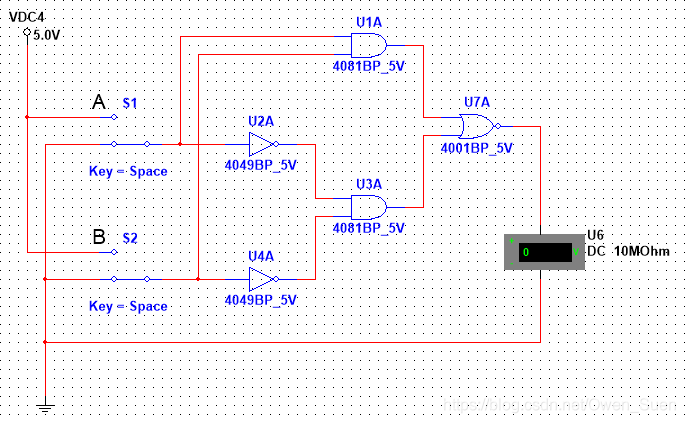

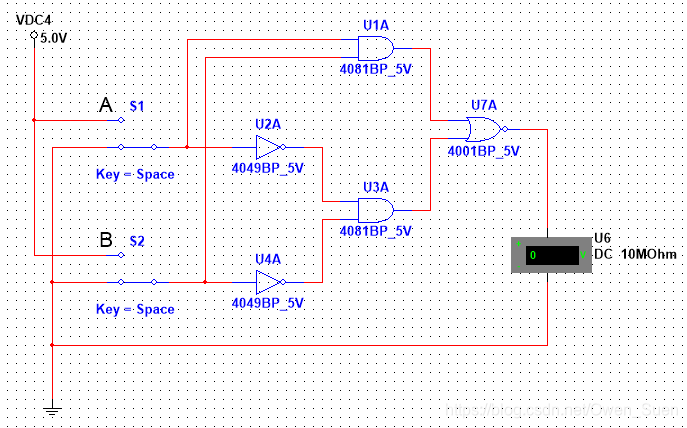

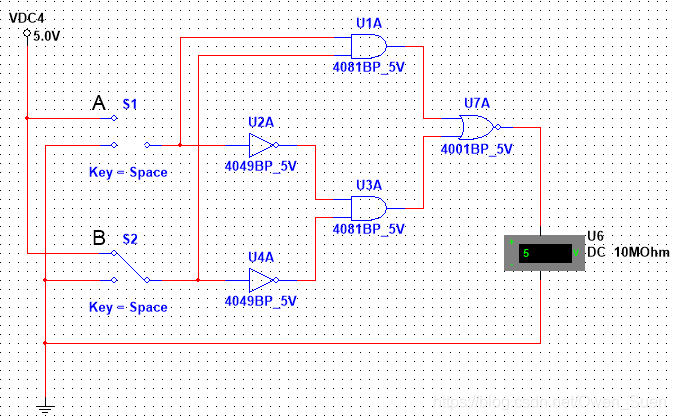

门电路设计实例

门电路直接对应于其基本逻辑,不多作介绍

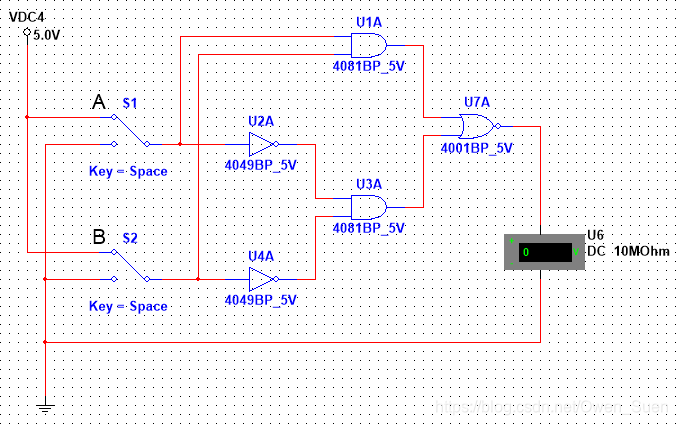

[0 0] == > [0]

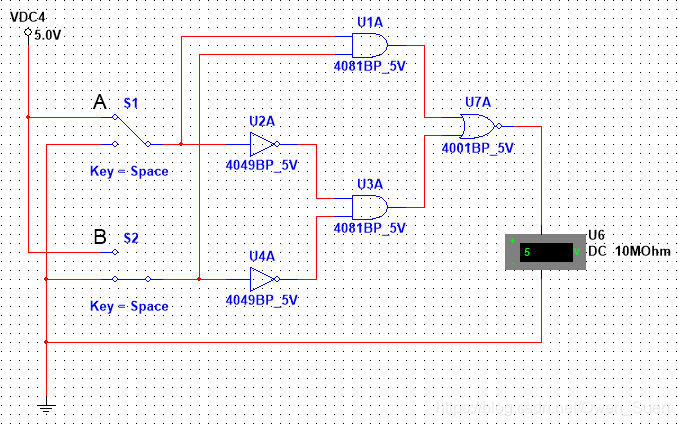

[0 1] == > [1] (5V)

[1 0] == > [1] (5V)

[1 1] == > [0]

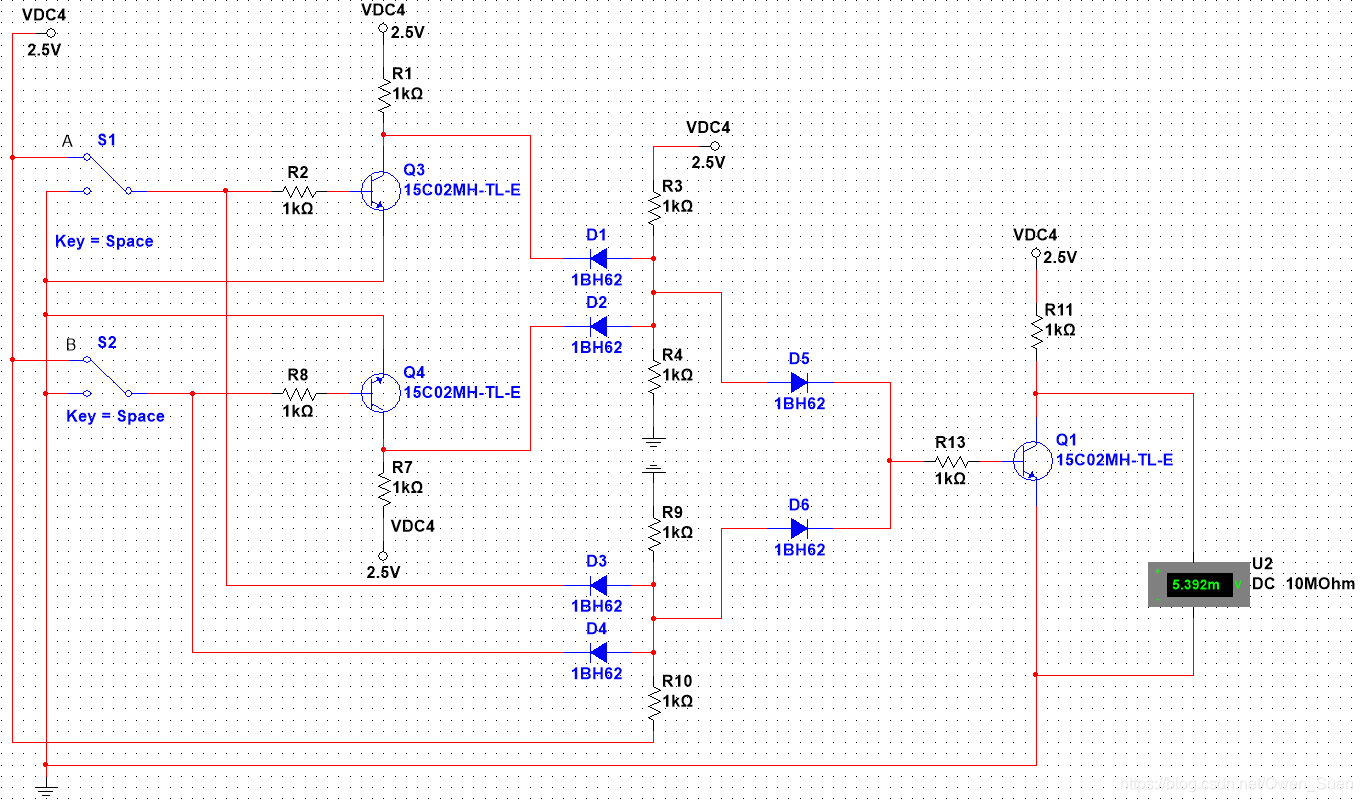

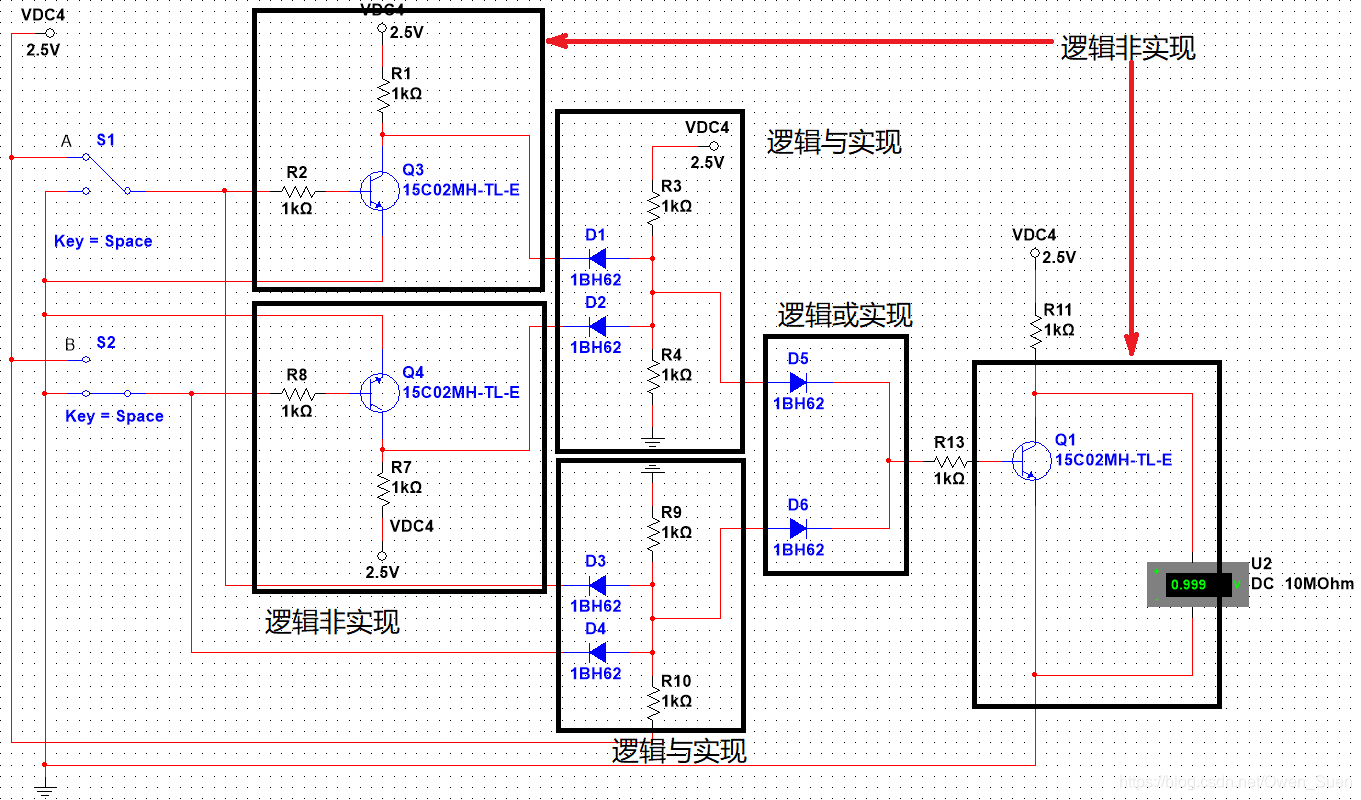

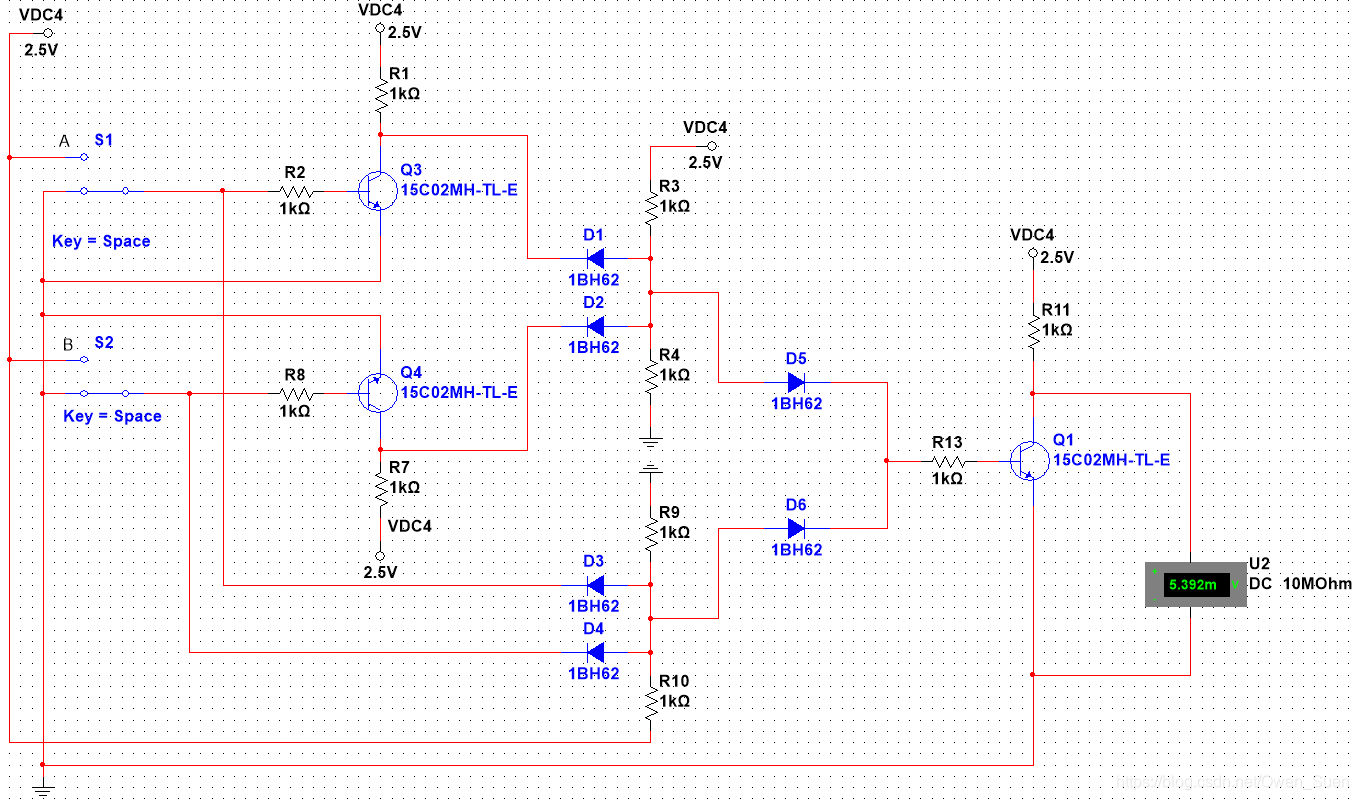

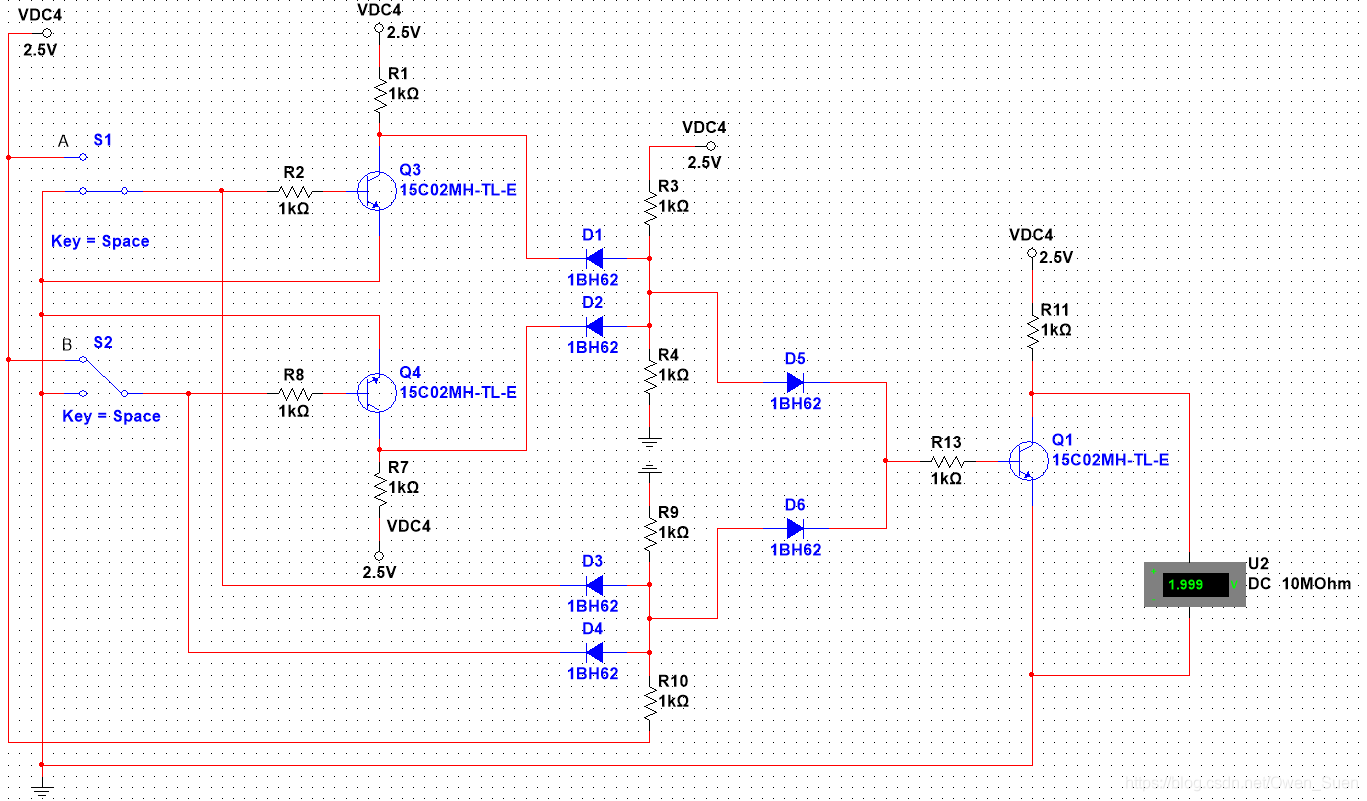

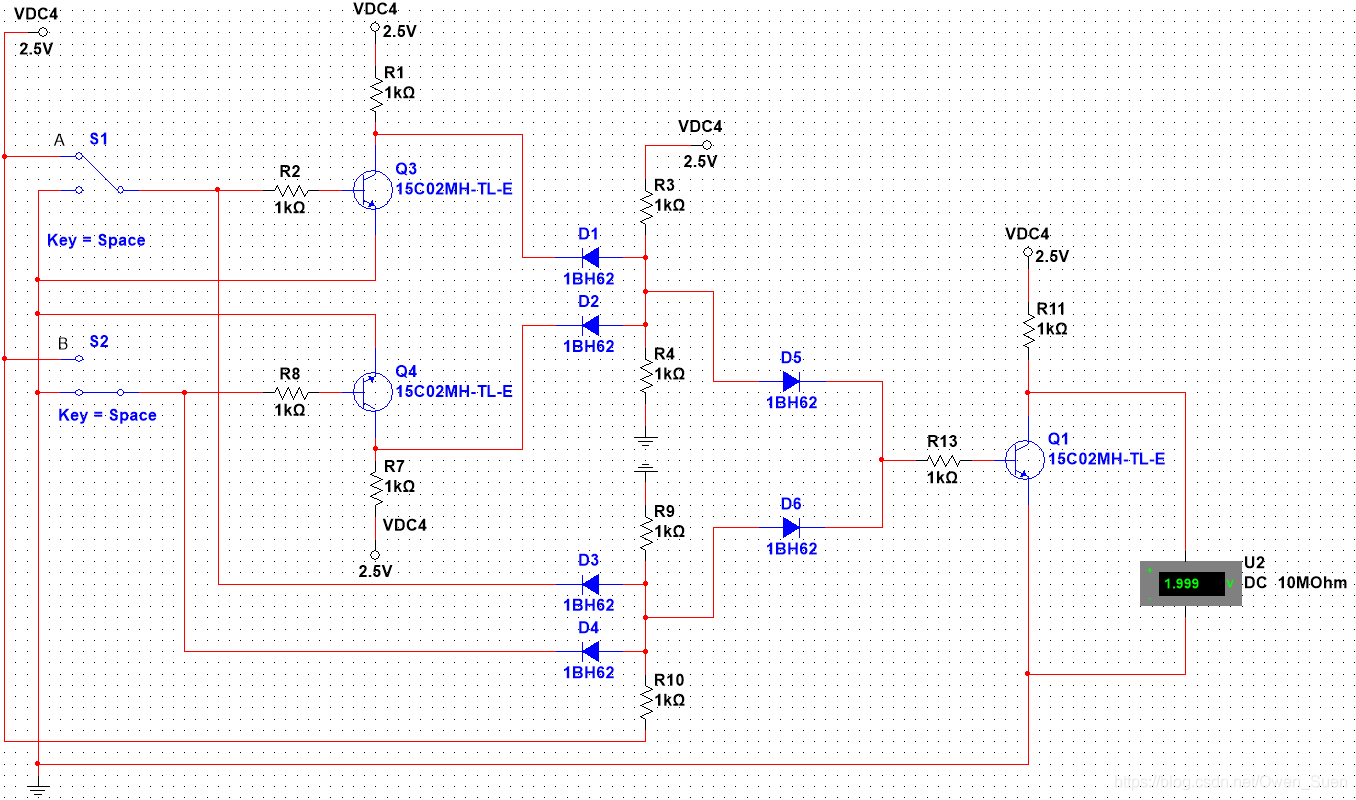

电路设计实例

当S1 S2均断开[0 0]时,输出OUT电压值为5.392mV [0]

当S1断开 S2闭合[0 1]时,输出OUT电压值为1.999V [1]

当S1闭合 S2断开[1 0]时,输出OUT电压值为1.999V [1]

当S1 S2均闭合[1 1]时,输出OUT电压值为5.392mV [0]