测试平台(testbench)的目的是什么?

测试平台使我们能够通过仿真来验证设计的功能。 是一个放置设计并通过不同的输入激励驱动的容器。

【1】产生不同类型的输入刺激;

【2】利用生成的激励来驱动设计输入;

【3】允许设计处理输入并提供输出;

【4】检查预期行为的输出以发现功能缺陷;

【5】如果发现了功能性错误,请更改设计以修复该错误;

【6】执行以上步骤,直到不再有功能缺陷为止;

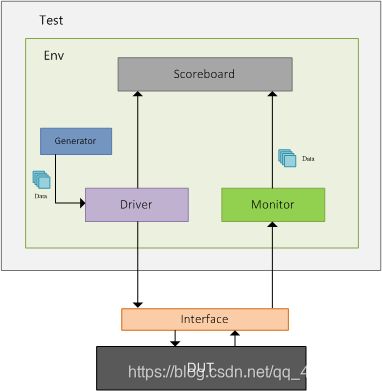

测试平台的组成

| 组件 | 描述 |

|---|---|

| Generator | 产生不同的输入激励以驱动至DUT |

| Interface | 包含可以驱动或监视的设计信号 |

| Driver | 驱动生成的激励到设计 |

| Monitor | 监视设计输入输出端口以捕获设计活动 |

| Scoreboard | 检查具有预期行为的设计输出 |

| Environment | 包含上述所有验证组件 |

| Test | 包含可以使用不同配置设置进行调整的环境 |

DUT是什么?

DUT代表测试中的设计,是用Verilog或VHDL编写的硬件设计。DUT是一个术语,通常用于芯片制造后的硅验证。在预验证中,也称为验证设计,简称DUV。

// 所有验证组件都放在此顶层测试平台模块中

module tb_top;

//声明需要连接到设计实例的变量;

// 这些变量被分配了一些值,这些值又作为输入传递给设计,因为它们与设计中的端口相连;

reg clk;

wire en;

wire wr;

wire data;

//实例化设计模块,并将上面声明的变量与设计中的端口连接

design myDsn (

.clk (clk),

.en (en),

.wr (wr),

. ...

.rdata);

endmodule

什么是interface?

如果设计包含数百个端口信号,则连接,维护和重新使用这些信号将很麻烦。 相反,我们可以将所有设计输入/输出端口放入一个容器中,该容器成为DUT的接口。 然后可以通过该接口以值驱动设计。

什么是driver?

驱动程序是验证组件,它通过接口中定义的任务来完成DUT的引脚摆动。 当驱动程序必须为设计驱动一些输入值时,它仅需在接口中调用此预定义任务,而无需实际知道这些信号之间的时序关系。 定时信息在界面提供的任务中定义。 这是使测试平台更加灵活和可扩展所需的抽象级别。 将来,如果接口更改,则新驱动程序可以调用相同任务并以不同方式驱动信号。

为什么需要显示器(monitor)?

到目前为止,已经讨论了如何将数据驱动到DUT。 但这只是一半,因为我们的主要目的是验证设计。 DUT处理输入数据并将结果发送到输出引脚。 监视器将拾取处理后的数据,将其转换为数据对象,然后将其发送到记分板。

scorebord的目的是什么?

记分板可以具有行为与DUT相同的参考模型。 该模型反映了DUT的预期行为。 发送到DUT的输入也将发送到该参考模型。 因此,如果DUT存在功能性问题,则DUT的输出将与参考模型的输出不匹配。 因此,比较设计和参考模型的输出将告诉我们设计中是否存在功能缺陷。 这通常在计分板上完成。

为什么需要环境(environment)?

由于可以为将来的项目将更多组件插入相同的环境,因此它使验证更加灵活和可扩展。

测试(test)做什么?

测试将实例化环境的一个对象,并按照测试所需的方式对其进行配置。 请记住,我们很可能会有成千上万的测试,并且每个测试都不能直接更改环境。 相反,我们希望环境中的某些旋钮/参数可以针对每个测试进行调整。 这样,测试将对刺激物产生有更高的控制力,并且将更加有效。

在这里,我们讨论了一个简单的测试平台的外观。 在实际的项目中,将插入许多这样的组件,以在更高的抽象级别上执行各种任务。 如果我们必须验证一个简单的数字计数器,最多包含50行RTL代码,是的,那么就足够了。 但是,当复杂性增加时,将需要处理更多的抽象。

什么是抽象级别?

在前言中,您看到我们使用单独的信号切换了设计。

#5 resetn <= 0;

#20 resetn <= 1;

相反,如果将这两个信号放在一个任务中并将其称为“ apply_reset”任务,则您刚刚创建了一个可以重用的组件,并且隐藏了发出信号的详细信息以及发出信号的时间间隔。 这是我们在开发测试平台时希望拥有的功能-隐藏细节-这样测试编写者无需费心如何使用这些任务,而只需关注何时以及为什么要使用这些任务。 最后,测试编写者使用任务,配置环境并编写代码以测试设计。

module tb_top;

bit resetn;

task apply_reset ();

#5 resetn <= 0;

#20 resetn <= 1;

endtask

initial begin

apply_reset();

end

endmodule

参考文献:

【1】https://www.chipverify.com/systemverilog/systemverilog-datatypes