本文由网友提供,非原创。

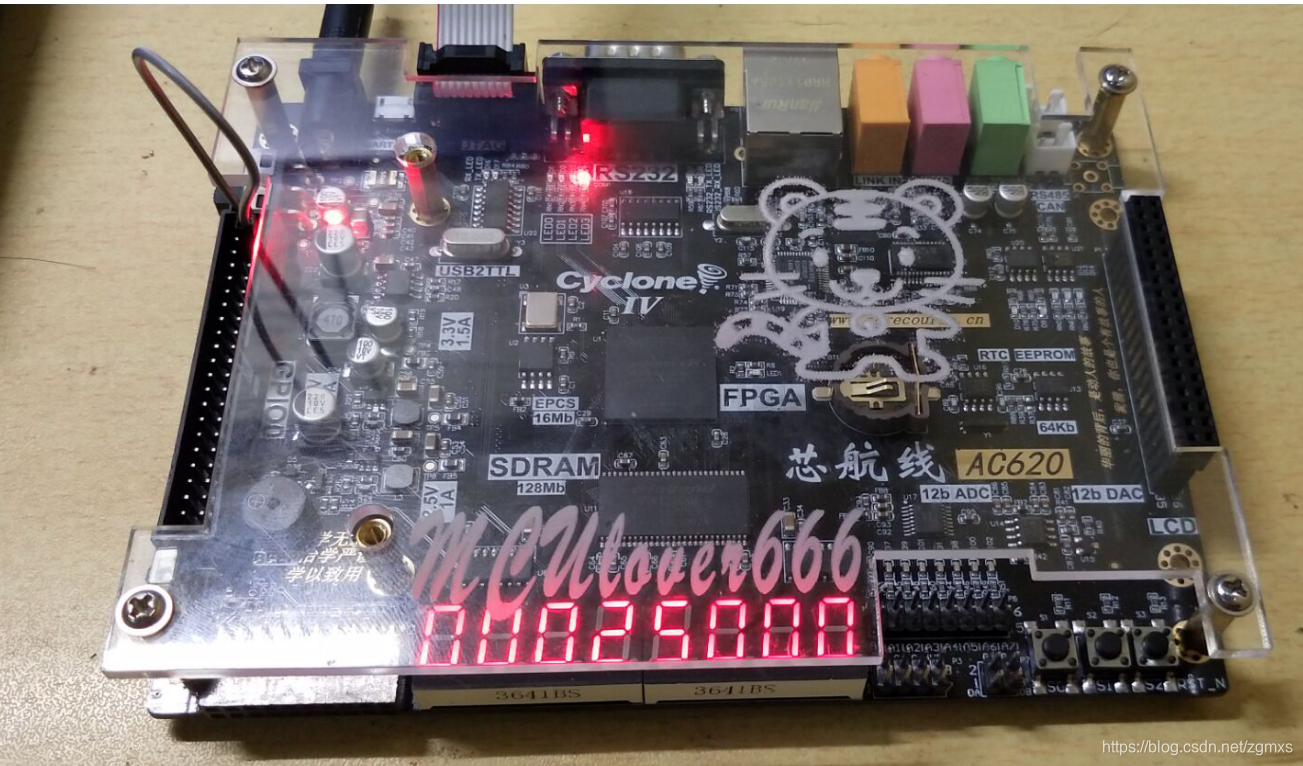

测量范围10Hz-50Mhz,通过8数数码管显示; 数字频率计的原理很简单,就是计算每秒钟内待测信号的脉冲个数,按照分模块设计的思想,分为:计数模块,数码管显示模块,控制信号模块,因为系统还需要高电平为1s的脉冲信号,所以还需要一个分频模块:

1、计数模块

计数器有二级制计数器和BCD计数器,因为计数器的计数结果需要经过译码送至数码管实时显示,所以选用BCD计数器,根据测量频率最大为50M,设计出计数器电路由8个4位BCD计数器级联实现;

2、数码管显示模块

BCD计数器的输出值为4位BCD码,经过显示译码电路送至数码管,显示译码电路通过查找表LUT设计方法实现;8位数码管同时显示8个不同的值需要通过16个IO(8位位选,8位段选)动态扫描显示,扫描间隔为1ms,AC620实验板上为了节省IO,通过两片74HC595实现串并转换,将16位串行数据转换为16位并行数据,所以采用三个IO口(工作频率SCK,存储频率RCK,数据线DIO)就可以实现数码管动态扫描显示,查阅74HC595数据手册可知,3.3V电压时工作频率SCK为1.25M;

3、控制信号模块

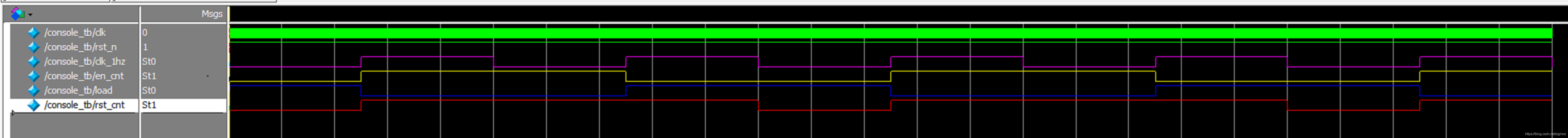

上面两个模块小梅哥都讲的很详细了,可以参考PDF或者视频,分频器最重要的就是控制信号模块,它需要产生3个控制信号:

1)待测信号控制脉冲 —— 产生高电平时长为1s的门控信号,和待测信号经过与门;起到控制待测脉冲到达计数器的作用

2)锁存信号控制脉冲 —— 计数器在门控信号为低电平时需要清零,以便下次计数,数码管上显示的数据需要保持,通过设计一个32位锁存器实现;在门控信号高脉冲结束时将数据送至锁存器供数码管显示

3)计数器复位脉冲 —— 将计数结果送至锁存器后,需要将计数器清零;

4、分频器模块

系统需要0.5hz的门控信号,1hz的脉冲信号,利用分频器将50M系统时钟分频得到;

一直很喜欢小梅哥的一句话,代码只是照图施工的过程,下面就是按照FPGA从上向下的设计思想实现整个设计了:

(.....好像不是很好传verilog代码....放附件吧)

modelsim仿真波形如图:

用10hz,25khz,50mhz三个信号下板验证效果: