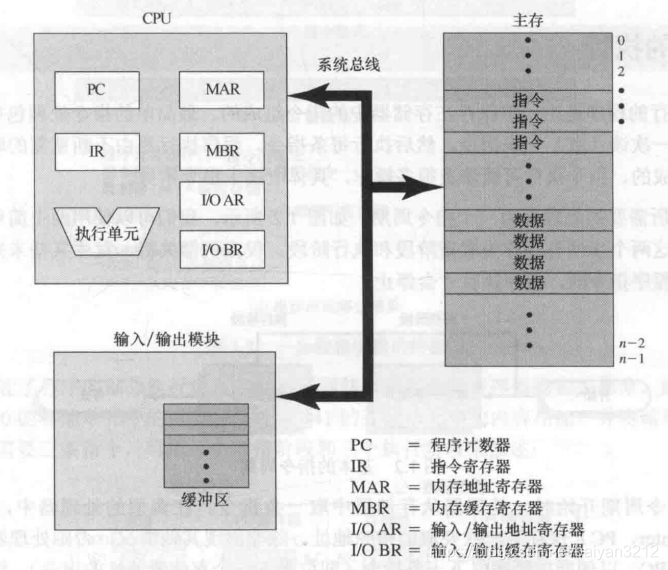

一.基本构成

- 处理器:cpu

- 内存:存储数据和程序,关机后内存上的内容会丢失,相对应的是磁盘存储器,关机后内容不会丢失

- 输入输出模块(IO):在计算机和外部环境之间移动数据,外部环境由各种外部设备组成包括硬盘,通信设备和终端

- 系统总线:在处理器,内存,输入输出模块间提供通信的设施

- MAR:内存地址寄存器用于确定下一次读/写的存储器地址

- MBR:内存缓存寄存器存放要写入内存的数据和从内存中读取的数据

- I/O AR:输入输出地址寄存器,用于确认一个特定的输入输出设备

- I/O BR:输入输出缓存寄存器用于在输入输出模块和处理器间交换数据

二 .指令的执行

处理器执行的程序是由一组保存在存储器中的指令组成的,最简单的指令处理包含两步:

处理器从存储器中一次读取一条指令,然后执行每条指令.

这两步分别称为取指阶段和执行阶段

PC:程序计数器(program counter) 保存下一次要取的指令地址.一般处理器在每次取指令后总是递增PC.以便能按顺序取下一条指令.

比如PC被置为地址300,处理器下一次将在地址为300的存储单元处取指令,取完后,pc地址变为301..下一次302..303

IR:指令寄存器 用于存放处理区取到的指令.

指令:指令中包含确定处理器将要执行的操作.处理器解释指令,并执行对应的操作 具体操作分为以下4类

- 处理器---存储器:数据可以从处理器传送到内存(存储器),或从存储器传送到处理器.

- 处理器---I/O:数据可以从处理器输出到I/O模块(外部设备),或者从外部设备向处理器输入数据

- 数据处理:处理器可以执行很多与数据相关的算术操作或逻辑操作

- 控制:控制指令执行的顺序,比如跳转或者循环,

比如处理器从地址为149的存储单元取一条指令,指令指定下一条指令从地址为160的存储单元取.这样处理器就会将程序计数器置为160,而不是递增为150.

一个例子:

假设一台机器具有以上图中的特征,处理器中包含一个累加器(AC)的数据寄存器

所有指令为16位,指令格式中操作码占4位,总共有2^4=16种操作码

0001 从内存中读取到AC 指令的第一个数字是1 后面3个数字代表存储单元地址

0010 将AC中的数据存储到内存 指令第一个数字为2

0101 从内存中添加到AC 指令第一个数字为5

下图描述了程序的部分执行相加的过程

1.pc程序计数器中第一个指令地址为300,300地址中的指令1940被读取到IR指令寄存器中,PC加1变为302

2.处理器解释IR中1940初4位为1代表从内存中读取地址为940的数据0003到AC

3.pc程序计数器中当前指令地址为301,301中的指令5941被读取到IR中 pc加1变为302

4.IR中5941前4位为5 换算成二进制位0101,将941的数据0002添加到AC.AC中变成0005.

5.pc程序计数器中当前指令地址为302,302中的指令2941被读取到IR中,PC变为303

6.IR中2941前4为为2 也就是0010,将AC中的数据0005存储到存储单元地址为941的位置,

这就是以上列子的执行过程.

三.中断

中断最初是用于提高处理器效率的一种手段.

中断的分类包括

- 程序中断:在某些条件下由指令执行的结果产生,如除数为0,非法的机器指令等

- 时钟中断:由处理器内部的计时器产生,允许操作系统以一定的规律执行函数.

- I/O中断:由I/O控制器产生,用于发信号通知一个操作的正常完成或各种错误条件

- 硬件失效中断:断电等机器故障产生

多数I/O设备要远慢于处理器,假设处理器要一直周期性给一台打印机传送数据,在每次写操作后,处理器都必须暂停,直到打印机完成工作,暂停的时间可能相当于成百上千个指令周期.这对于处理器来说是相当浪费的.

假设有一个CPU,每秒约可以执行10^9条指令,硬盘7200转/秒,旋转半周的时间约为4ms,这比处理器约慢400万倍.

无中断:例如上图a中用户程序在处理过程中会间断执行一些Write操作,Write调用执行I/O程序,用户执行遇到Write指令,用户程序被中断,开始执行I/O操作,I/O操作可能要花费较长时间,用户程序会停留较长时间.然后一直到I/O操作完成再接下去执行.时间都用在了等待I/O操作上

短中断:图b中处理器可以在I/O操作的执行过程中执行其他指令,用户程序到达Write处时,执行I/O准备代码和命令,然后立刻返回继续执行用户程序,这期间用户程序中的指令和I/O操作是并发的.当I/O操作完成后,I/O模块会给处理器发送一个中断请求信号,这时处理器会暂停当前用户程序,处理I/O后续的操作.中断和指令周期如下图

显然在这个处理中有一定的开销,在中断处理程序中,必须执行额外的指令判断中断性质,并决定采用何种操作.

下图是上面图b控制流的时序图

这样的前提是I/O操作时间相当短,少于用户写操作之间完成指令执行的时间,也就是说I/O操作在下一次Write调用前要完成

但是实际情况是I/O操作往往比这一系列用户程序指令的时间还要长的多.

长I/O等待:图c中用户程序在第一次I/O操作完成之前就到达了第二次Write调用,这时用户程序挂起,当第一次/O操作完成后再开始第二次I/O调用,下面是上诉情况和无中断的时序图,I/O操作在没完成前,依然会和用户程序指令执行并发,效率依然比无中断高

四.存储器的层次结构

存储器的三个重要特性是:容量,速度,价格.

三者之间的关系如下

存取时间越快,每位的价格越高,容量越大,每位的价格越低,容量越大,每位的速度越慢

在同等价格前提的情况下,我们希望又有大容量,而且有需要速度快.所以我们使用存储器层次结构

具体分为板上存储器,板外存储器,离线存储器(外置?)

上图中的存储结构从上向下存在下面的特点:

- 每位的价格越来越低

- 容量递增

- 存取的速度越来越慢

- 处理器访问的频率越来越低

五.高速缓存

为什么要有高速缓存

因为在指令周期中,指令保存在存储器中,处理器在取指时至少要访问一次存储器,(实际上是很多次),内存的速度过慢,导致处理器执行指令的速度也变慢.但是如果内存的构造技术采用和处理器中的寄存器相同的技术,成本又过高.于是解决办法是在处理器和内存之间提供一个容量小但是速度快的存储器,就是高速缓存

高速缓存的原理

如图所示,处理器读取存储器的一个字节时,先看高速缓存中有没有,有就直接从高速缓存中直接读取,如果没有,就由固定数目的字节组成一块内存数据一次性读入高速缓存,再传递给处理器,当一块数据被读取入高速缓存时满足一次处理器访问时,很可能紧接着的多次访问的数据是该块中的其他字节.就避免了频繁和内存交互.

上图是高速缓存的多级使用,其中1级缓存速度大于2级大于3级,容量小于2级小于3级.

下图是高速缓存和内存的结构图

内存由2^n个可寻址的字组成.(例如32位电脑,为2^32可以换算成4G内存),将内存分为多个块,每个块有K个字,就会有

M=2^n/K个块,高速缓存中有C个存储槽,也可以当做行,每个槽有K个字,当读取存储器中某一块的某一个字时,这个块又不在槽中,则将这个块转移到一个槽中,每个槽中有一个标签,用来标识当前存储的块,标签通常是地址中较高的若干位,表示以这些位开始的所有地址

如标签01块中包含下列地址单元 010000,010001,010002......011111.

下图是一个高速缓存的读操作过程

六.直接内存存取

在移动大量数据时,直接内存存取模块(DMA)负责与存储器交互,传送整个数据块,不需要处理器参与,在传送完成后,才给处理器一个中断信号

七. 多处理器和多核

多处理器

是有多个独立的CPU,每个CPU能执行相同的功能,也叫对称处理器

多核

是多个处理器组装在同一个硅片上,又名芯片多处理器

二者区别

对于多个处理器而言,它们在执行命令的时候多个处理器之间的通信手段是电脑主板上的总线;而对于多核处理器而言,多个核心处理器之间通信时通过CPU内部总线进行信息的交互的。对于执行效率而言,多核处理器要优于多个处理器

若跑小程序,选多核

对于多处理器:如果跑一个多线程的程序(常见典型情况),不考虑超线程,那么每一个线程就要跑在一个独立的CPU上,线程间的所有协作都要走总线,而共享的数据更是有可能要在好几个Cache里同时存在。这样的话,总线开销相比较而言是很大的,怎么办?那么多Cache,即使我们不心疼存储能力的浪费,一致性怎么保证?如果真正做出来,还要在主板上占多块地盘,给布局布线带来更大的挑战?所以对于个人计算机来说,都采用单处理器多核。只需要一套芯片组,一套存储,多核之间通过芯片内部总线进行通信,共享使用内存。在这样的架构上,如果我们跑一个多线程的程序,那么线程间通信将比上一种情形更快。如果最终实现出来,对板上空间的占用较小,布局布线的压力也较小。

若跑大程序,选多CPU多核

假设俩大程序,每一个程序都好多线程还几乎用满cache,它们分时使用CPU,那在程序间切换的时候,光指令和数据的替换就很费事。所以,需要更强的多任务并发能力,就用多颗多核CPU的机子。