Chapter1 计算机系统概述

1.1 基本构成

-

4个主要的结构化部件:处理器、主存、输入/输出模块、系统总线

-

处理器与存储器交换数据:MAR、MBR

处理器与输入/输出模块交换数据:I/O AR、I/O BR

处理器中的PC、IR

1.2 微处理器的发展

略

1.3 指令的执行

-

指令周期:取指阶段、执行阶段

-

程序计数器PC、指令寄存器IR

-

指令的4种主要操作:处理器与存储器数据传输、处理器与输入/输出模块数据传输、数据处理(处理器可进行算术操作和逻辑操作)、控制(改变执行顺序)

-

example(包含处理器与存储器数据传输、数据处理)

(1) PC=300,处理器从地址为300的存储器单元取指令1940,将指令放入IR,PC递增为301

(2) 执行该指令,处理器从地址为940的存储器单元取数据0003,放入累加器AC

(3) PC=301,处理器从地址为301的存储器单元取指令5941,将指令放入IR,PC递增为302

(4) 执行该指令,处理器从地址为941的存储器单元取数据0002,与AC中数据相加,结果存回AC

(5) PC=302,处理器从地址为302的存储器单元取指令2941,将指令放入IR,PC递增为303

(6) 执行该指令,处理器将AC中数据存入地址为941的存储器单元

1.4 中断

-

常见中断类别:程序中断、时钟中断、I/O中断、硬件失效中断

-

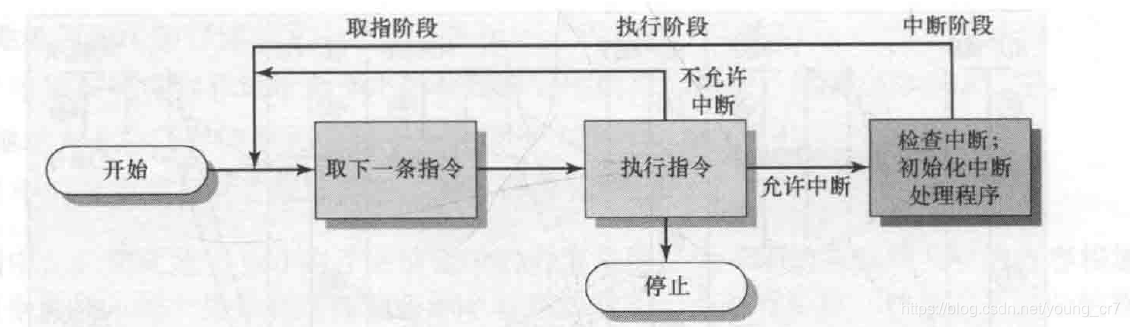

指令周期

-

长I/O等待与短I/O等待的程序时序分析

-

中断处理时的软硬件事件

-

处理多个中断

(1) 在处理一个中断时,禁止再发生中断

(2) 定义中断优先级,允许高优先级中断打断低优先级中断的运行

1.5 存储器的层次结构

- 计算机存储器设计的目标:速度、容量与价格之间的权衡

- 存储器层次结构

存储器层次从上往下:处理器的寄存器、高速缓存、内存、磁盘

(1) 每bit的价格递减

(2) 存取速度递减

(3) 容量递增

(4) 处理器访问频率递减

1.6 高速缓存

-

高速缓存的意义:处理器执行指令的速度受存储周期限制,速度与成本的权衡下,考虑利用局部性原理,在寄存器与内存之间增加一个容量小且速度快的存储器

-

访问局部性原理:高速缓存与内存之间进行块传递

-

高速缓存的多级使用

-

原理

(1) 内存容量为 个字,每个块(block)包含K个字,共有 个块

(2) 高速缓存中有C个存储槽(slots),每个槽有K个字和一个标签(标识存储的块)

(3) (RA为处理器读取的字的地址),处理器读取字时,若包含RA的块不在高速缓存中,则处理器访问内存中包含RA的块,为其分配高速缓存槽,然后把内存中的块载入高速缓存槽,同时把RA中的字传递给CPU;若包含RA的块在高速缓存中,直接取RA中的字传递给CPU

1.7 直接内存存取

-

执行I/O操作的技术:可编程I/O、中断驱动I/O、直接内存存取(DMA)

(1) 可编程I/O操作:处理器给I/O模块发命令来执行指令后,要定期检查其状态以确定I/O操作是否完成,处理器要等待很长的时间

(2) 中断驱动I/O

-

直接内存存取(DMA, direct memory access)

(1) 处理器向DMA模块发送指令后,DMA模块直接与存储器传送整个数据块,完成后DMA模块向处理器发出一个中断信号

(2) 处理器向DMA模块发送的指令包括:是否请求开始读写操作,I/O设备的地址,存储器单元,读写的字数

1.8 多处理器和多核计算机组织结构

-

对称多处理器(SMP)

(1) 定义:多个性能可比的处理器、共享内存和I/O设备(通过系统总线)、共享对I/O设备的访问、可执行相同功能、由统一的操作系统控制,可进行作业、进程、文件和数据元素等级别的交互

(2) 与单处理器对比

1) 性能提升

2) 可用性:单个处理器失效不会导致停机

3) 渐增式成长

4) 可伸缩性(3) 组织结构

高速缓存一致性问题通常通过硬件解决

-

多核计算机:将多个处理器(核)组装在同一块硅(片)上的计算机,又称为芯片多处理器