在文章《LUT是如何实现千万种逻辑结构的》里面我们讲过了LUT的原理,实现逻辑函数时,相当于一个ROM将结果预存,然后把通过输入信号当作地址对预存的结果进行寻址。因此同样借助LUT加几个端口,就可以实现RAM。SLICEM里面的LUT就可以用来实现RAM资源。我们接下来讲几个概念。

(1)CLB

CLB:可配置逻辑单元(Configurable Logic Block,CLB)在FPGA中最为丰富,由两个SLICE组成。由于SLICE有SLICEL(L:Logic)和SLICEM(M:Memory)之分,因此CLB可分为CLBLL和CLBLM两类,SLICEM的数量占总SLICE数量的1/3,一个SLICEM里面有4个6输入查找表,也就是4*64bit存储空间(6输入:可配置64x1的RAM)。

SLICEL和SLICEM内部都包含一下四个东西,下图为SLICEM内部框图:

- 4个6输入查找表(Look-Up-Table,LUT6)

- 8个触发器(Flip-Flop)

- 3个数据选择器(MUX)

- 1个进位链(Carry Chain)

(2)多路复用器

上面讲到一个SLICE里面有3个数据选择器(MUX),分别为F7AMUX、F7BMUX、F8MUX,F7AMUX可以把LUT A和LUT B两个6输入的64位LUT(RAM)组合为一个7输入的128位LUT(RAM),我们可以命名为LUT X,F7BMUX可以把LUT C和LUT D两个6输入的64位LUT(RAM)组合为一个7输入的128位LUT(RAM),我们可以命名为LUT Y,F8MUX可以把LUT X和LUT Y两个7输入的128位LUT(RAM)组合为一个8输入的256位LUT(RAM),从而可以看出F7AMUX、F7BMUX、F8MUX具有一个功能就是扩展LUT数据位宽的作用。看下面的四输出RAM都是由MUX扩展出来的。

(3)LUT RAM实现原理

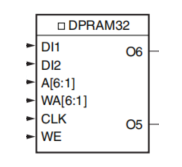

由上图我们可以看出SLICEM有四个LUT单元,SLICEM里面的LUT跟SLICEL里面的LUT相比多了DI2,WA[6:1],CLK,WE这几个端口。做RAM用的时候,其中DI1,DI2是写数据输入端口,O5,O6同样是数据输出端口,支持一次性两bit或者单bit读写。A[6:1]为读地址,WA[6:1]为写地址,WE为写使用,CLK为时钟端口。

从这可以看出,一个LUT具有2^6=64bit的存储空间。

1. 64x1bits单端口RAM原理

一个LUT可以作为64x1bits的RAM(内存大小为64bit,1bit读写),地址为6位。当读写地址共用一个端口时为单端口RAM,不共用时则为双端口RAM(由图中可以看出SLICEM里面第一个LUT的WA与A是连在一起的,故第一个LUT做不了双端口RAM)。输出数据可以经过SLICEM里面的Register资源打一拍以提高时序特性。64bit单端口RAM LUT实现及原语如下图:

2. 64x1bits双端口RAM原理

对于双端口RAM,使用了2个LUT,第一个LUT的读写地址是连接到一起的,而第二个LUT的写地址和第一个LUT的写地址连接到一起的,但是读地址是独立的,所以双扣RAM可以同时进行读写操作,也就是达到了写操作和读操作互不干扰,写操作有些地址,读操作有读地址。下面是简单双口RAM只有一个写端口,一个读端口,真双口RAM才会分别有两个写端口和两个读端口,不要混淆了。

3. 32x2bits单端口RAM原理

或者作为32x2bits的RAM(2bit读写),地址为5位,A[6]拉高。输出为O5,O6。

4. 32x2bits四端口RAM原理

一个SLICEM里面有4个LUT,他们可以组合得到多种大小的RAM。首先就是四端口的32x2bits的RAM,支持一次性读写2bits,原理如下图。四个LUT的写数据端口DI1,DI2,写使能WE,写地址WA共用,称为写控制信号共用。读地址A分别控制。LUT原理及verilog原语如下图:

5. 128x1bits单端口RAM原理

下图可以看出,通过F7BMUX把2个64bit的LUT的组合可以串联实现更大深度的分布式,RAM也就是7输入的RAM。F7BMUX可以实现选择LUT C 64bit还是选择 LUT D 64bit,用第七个输入信号控制F7BMUX是否选通。LUT原理及verilog原语如下图:

6. 128x1bits双端口RAM原理

128x1bit的双口RAM需要四个LUT实现,也正好是一个SLICEM,并且分别使用了F7AMUX、F7BMUX。用两份128bitRAM,读写地址分开的方式实现读写互不干扰。LUT原理及verilog原语如下图:

7. 256x1bits单端口RAM原理

256x1bit的单口RAM需要四个LUT实现,也就是8输入的RAM,也正好是一个SLICEM,并且分别使用了F7AMUX、F7BMUX、F8MUX。F7AMUX可以实现是选择LUT A 64bit还是选择LUT B 64bit,用第七个输入信号控制F7AMUX是否选通。F7BMUX可以实现是选择LUT C 64bit还是选择LUT D 64bit,用第七个输入信号控制F7BMUX是否选通。F8MUX实现是选择F7AMUX输出还是F7BMUX输出,用第八个输入信号控制F8MUX是否选通。LUT原理及verilog原语如下图:

(4)分布式ROM

SLICEL和SLICEM的每一个LUT都可以实现64X1bit的ROM。和RAM实现的方式原理是一样,就是取消了写地址和写使能,只需要对地址信号的查找即可。