特权同学玩转Zynq连载4——AXI总线协议介绍2

2 信号描述

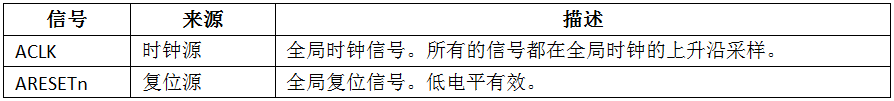

2.1 全局信号

表2-1 全局信号

2.2 写地址通道信号

表2-2 写地址通道信号

注:对于一般的应用,AWBURST、AWLOCK、AWCACHE和AWPROT通常赋一个特定的值,即设定为固定的工作模式即可。

2.3 写数据通道信号

表2-3 写数据通道信号

2.4 写响应通道信号

表2-4 写响应通道信号

2.5 读地址通道信号

表2-5 读地址通道信号

2.6 读数据通道信号

表2-6 读数据通道信号

3 握手过程

全部5个通道使用同样的VALID和READY握手机制来实现数据和控制信息的传输。这个双向的流控制机制使主机和从机能控制数据和控制信息的传输速度。发送端产生VALID信号指示数据或控制信息有效,接收端产生READY信号表明它可以或已经接收数据或控制信息。只有在VALID和READY信号都为高电平的时候才能进行有效的传输。

如图所示,这是一个握手的实例。发送端送出数据或控制信息(INFORMATION),并将VALID信号拉高。来自发送端的数据或控制信息保持稳定直到接收端将READY信号拉高,指明接收端已经接收数据或控制信息。箭头表明了传输实际发生的时机。

必须注意,若发送端要发起一次传输,不允许VALID信号一直等待READY变为高电平才执行拉高操作。正确的操作应该是,将VALID拉高,一直保持高电平直到READY拉高,完成一个完整的握手操作。

如图所示,接收端在VALID信号拉高之后,才将READY信号拉高,表示发送端发出的数据或控制信息被接收。这意味着,接收端若在VALID信号拉高之前就已经将READY拉高表示准备好,那么只需要1个时钟周期就可以完成一次数据或控制信息的有效传输。箭头表明传输发生的时机。

接收端送出的READY信号在VALID拉高之后才拉高,在这个握手机制中是允许的。如果READY为高电平,在VALID拉高之前将READY拉低也是允许的。如图所示,在这个实例中,VALID和READY信号同一个时钟周期拉高了,那么这正好是一次有效的数据或控制信息的传输。