时钟SM

(1) 部件功能:

模型机中所有指令的执行都是一个周期完成取指令,一个周期执行指令。SM则用来区分当前周期是取指令还是执行

(2) 接口设计:

输入:

EN使能信号1有效

Clk:时钟信号

输出:

Z,变化的周期性时钟信号

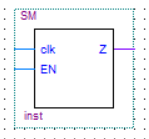

RTL视图

(3) 功能实现:

在时钟下降沿进行判断:

如果EN=1,就对SM取反后输出,EN=0,就输出SM的现有值

VHDL设计:

(4)功能仿真验证:

仿真结果:

时钟为1ns: 处于时钟下降沿,EN=1,对SM取反后输出,SM=1

时钟为2ns: 处于时钟下降沿,EN=1,对SM取反后输出,SM=0

时钟为3ns: 处于时钟下降沿,EN=1,对SM取反后输出,SM=1

时钟为4ns: 处于时钟下降沿,EN=1,对SM取反后输出,SM=1

时钟为5ns: 处于时钟下降沿,EN=1,对SM取反后输出,SM=0

时钟为6ns: 处于时钟下降沿,EN=1,对SM取反后输出,SM=1

时钟为16ns: 处于时钟下降沿,SM不再变化,SM持续为1

结论:仿真结果符合功能要求,设计成功