1.软件版本

Quartusii12.1

2.本系统主要内容

仿真是用Quartus II 12.0软件仿真的,语言是verlog hdl,生成矩形波,脉冲波,正弦波,4级m序列(m序列输出一个就行)。 程序下载到开发板后,示波器要能观察到波形。开发板是emp240的。最好能够通过开发板上按键实现选择输出要的波形,不能的可以分开输出。

3.核心代码

module tops(

i_clk,//clock

i_rst,//rest,

i_key,//key

o_signal//4 kind of signal

);

input i_clk;

input i_rst;

input[1:0] i_key;

output[7:0]o_signal;

wire signal_cube;

wire signal_pluse;

wire signal_m;

wire[7:0]signal_sin;

//the module of juxin signal

signal_jux signal_jux_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_signal (signal_cube)

);

//the module of pluse signal

signal_p signal_p_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_signal (signal_pluse)

);

//the module of m signal

signal_mseq signal_mseq_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_signal (signal_m)

);

//the module of sin signal

signal_sin2 signal_sin2_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_signal (signal_sin)

);

reg[7:0]o_signal;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_signal <= 8'd0;

end

else begin

case(i_key)

0:o_signal <= {signal_cube,7'b000_0000};

1:o_signal <= {signal_pluse,7'b000_0000};

2:o_signal <= {signal_m,7'b000_0000};

3:o_signal <= signal_sin;

default:o_signal <= {signal_cube,7'b000_0000};

endcase

end

end

endmodule 4.操作步骤与仿真结论

仿真是用Quartus II 9.0软件仿真的,语言是verlog hdl,生成矩形波,脉冲波,正弦波,4级m序列(m序列输出一个就行)。 程序下载到开发板后,示波器要能观察到波形。

我的cpld的开发板是emp240的。最好能够通过开发板上按键实现选择输出要的波形,不能的可以分开输出。

设计说明:

扫描二维码关注公众号,回复:

13774779 查看本文章

这个设计中,我们将四种波形使用选择开关进行选择输出。

外部连接两个按键,00输出矩形波,01输出脉冲波,10m序列,11输出正弦序列。

系统的仿真效果如下所示:

00:

01:

10:

11:

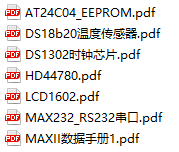

5.参考文献

A35-01

6.完整源码获得方式

方式1:微信或者QQ联系博主