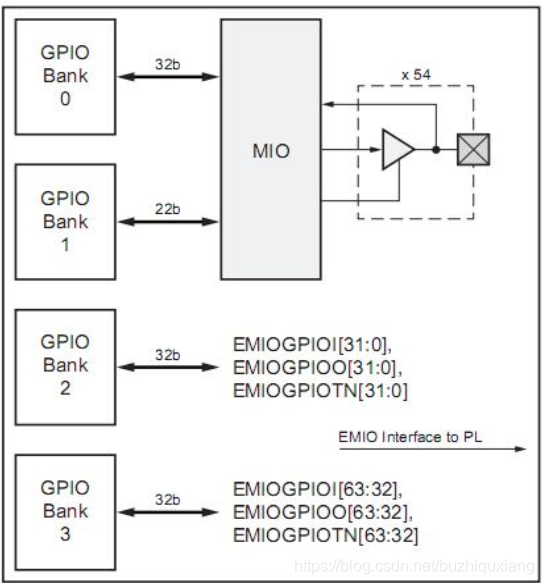

GPIO中MIO(multiuse IO)与EMIO(extendable multiuse IO)的区别:

MIO 分配在 bank0 和 bank1 直接与 PS 部分相连, EMIO 分配在 bank2 和 bank3 和 PL部分相连。 除了 bank1 是 22-bit 之外, 其他的 bank 都是 32-bit。 所以 MIO 有 53 个引脚可供我们使用, 而 EMIO 有 64 个引脚可供我们使用。

使用 EMIO 的好处就是, 当 MIO 不够用时, PS 可以通过驱动 EMIO 控制 PL 部分的引脚, 接下来就来详细介绍下 EMIO 的使用。

EMIO 的使用和 MIO 的使用其实是非常相似的。 区别在于, EMIO 的使用相当于, 是一个 PS + PL 的结合使用的例子。 所以, EMIO 需要分配引脚, 以及编译综合生成 bit文件。

步骤与ZYNQ(一)中相同

(1)创建一个vivado工程

(2)open Block Design

(3)配置zynq ps端

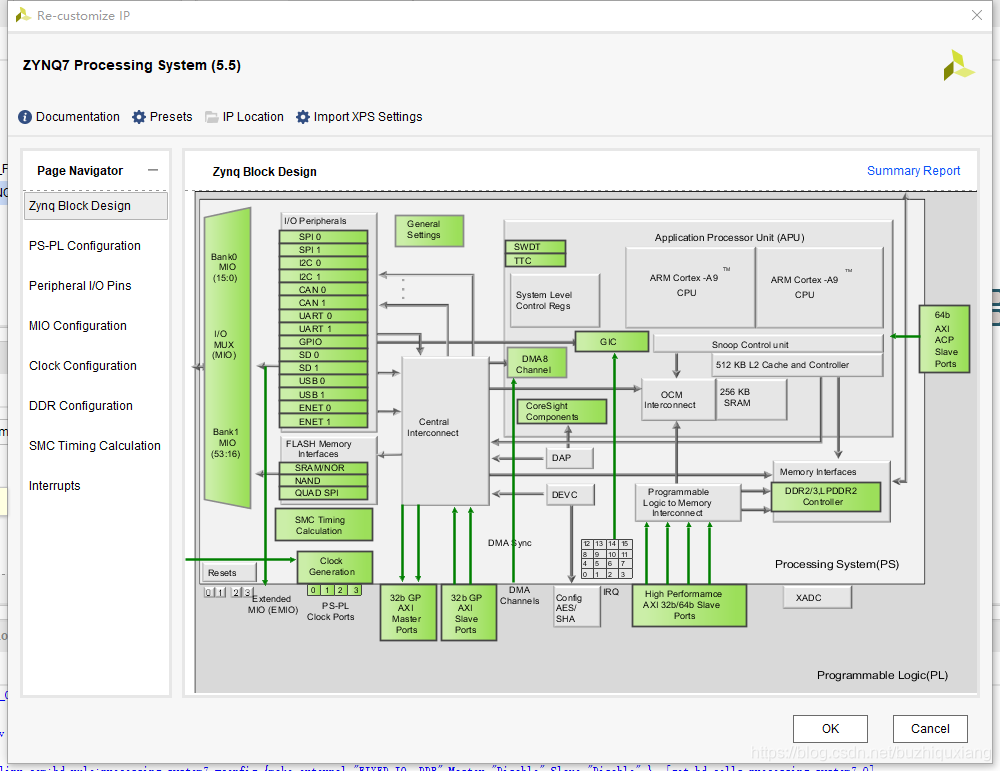

(此处提及zynq的ps端与pl端包含的内容)

顶部的四个按钮:

(1)Documentation 查找与ZYNQ相关的文档

(2)Presets 保存或导入一些预设配置

(3)IP Location IP的路径

(4)Import XPS Settings 导入由XPS工程产生的XML文件

(绿色代表可配置)

一、PS-PL Configuration:

GP Slave AXI Interface:(2个)

这种接口将主机与从机端口直接相连,不需要额外的FIFO缓冲。由于没有FIFO,AXI_GP接口的性能受到主机和从机端口的限制。这种接口用于往往不会太关注性能的一般用途。

HP Slave AXI Interface:(4个)

4个AXI_HP接口为PL总线主程序提供了到DDR和OCM内存的高带宽数据通道,每个接口有两个用于读写通信的FIFO缓冲区。内存互连的PL将高速AXI_HP端口布线到两个DDR内存端口或OCM。AXI_HP接口也可以用作AXI_FIFO接口,利用其缓冲能力。

ACP Slave AXI Interface:(1个)

ACP接口允许对PL主机进行低延迟访问,带有可选的coherency和L1、L2缓存。从系统角度来看,ACP接口具有与APU CPU类似的连通性,因此ACP可以直接在APU块争取资源。

二、Peripheral I/O Pins /MIO Configuration

Zynq-7000支持Quad-SPI Flash、SRAM/NOR Flash和NAND Flash三种闪存,配置时只能选择其中一个。注意外设之间如果发生管脚冲突,会用红色提示。

三、时钟配置

PS上外设的时钟源可以由内部PLL生成,也可以来自外部时钟源。同一个PLL可能要产生多个频率,导致得到的频率不是完全准确,在Actual Frequency列中查看能够实现的实际频率。PS的输入频率范围限制在30~60MHz之间,通常都会选择33.33MHz,便于产生内部所需的时钟频率。

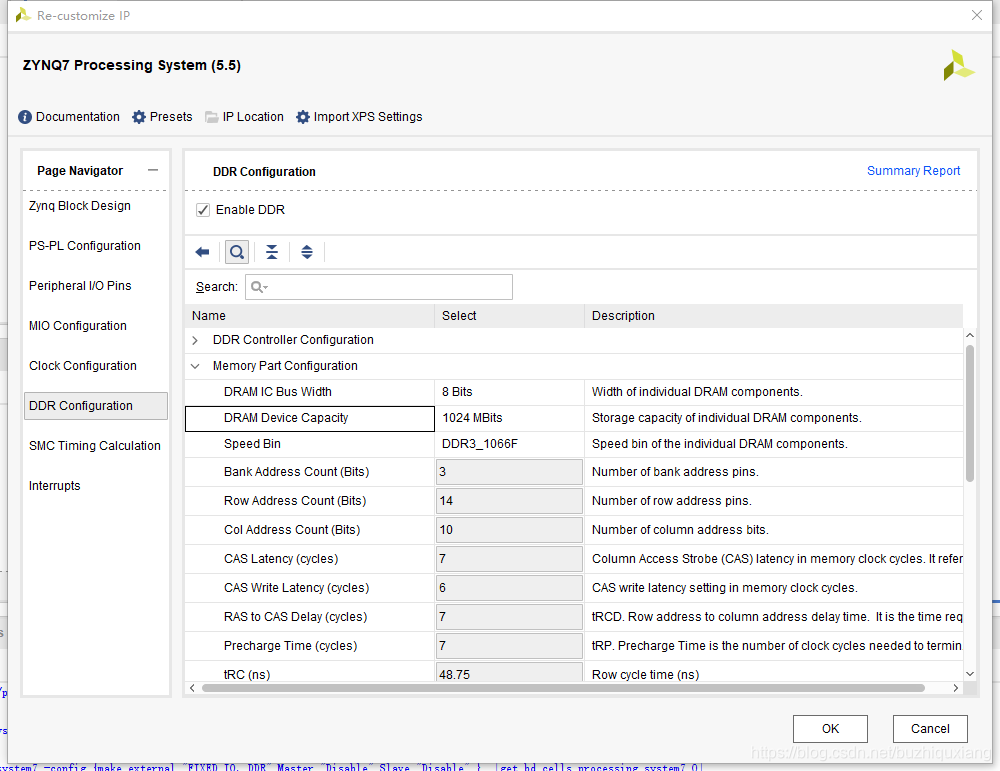

四、DDR配置

ZYNQ-7000的内存控制支持DDR2、DDR3、DDR3L和LPDDR2

DDR型号要与开发板相符:

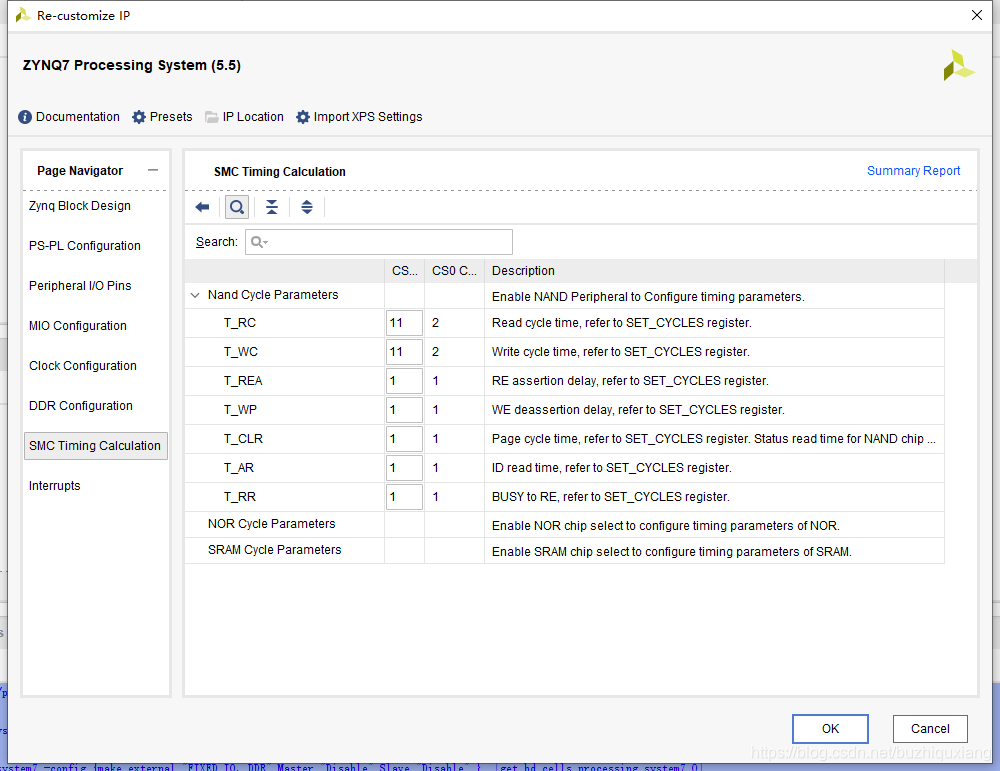

五、SMC Timing calculation

可配置Quad-SPI Flash、SRAM/NOR Flash和NAND Flash的时间参数

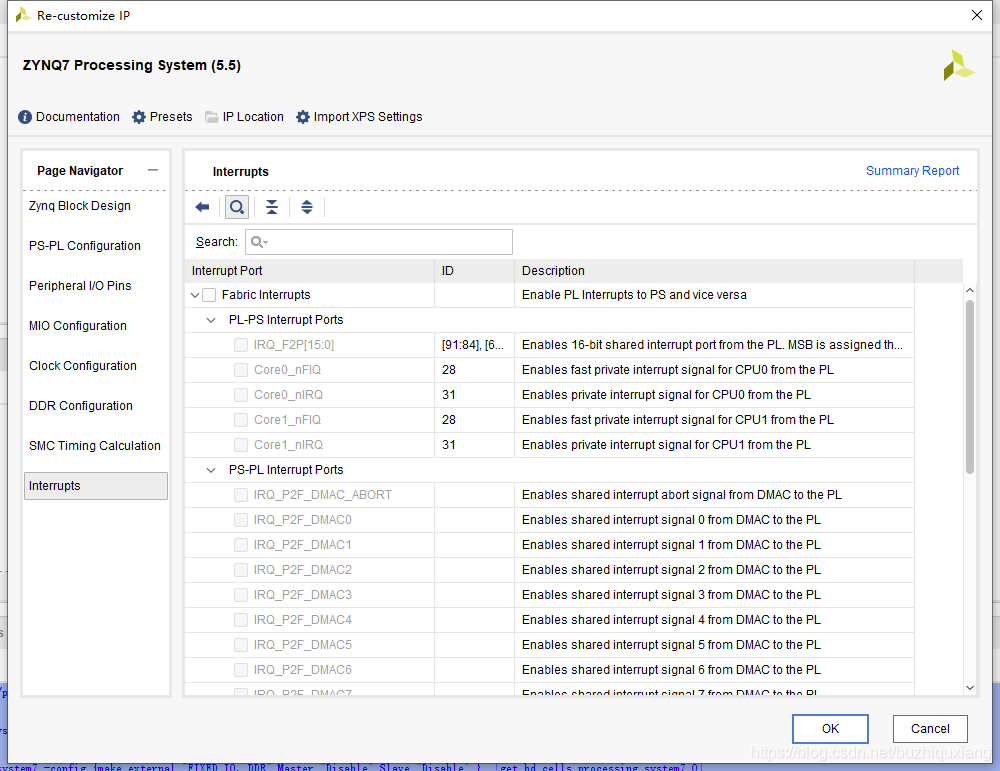

六、Interrupts

在Interrupts中对通用中断控制器GIC(Generic Interrupt Controller)进行配置。GIC用于管理从PS和PL发送到CPU中的终端。当CPU接口接收一个新中断时,GIC以编程的方式启用、禁用、屏蔽与优先处理中断源,并将其发送到选定的CPU。

PL端:

(一):可配置逻辑块(CLB):

包含带有存储功能的6输入查找表(LUT)、寄存器与移位寄存器和一些选型电路组成。每个CLB不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM和分布式ROM。

(二):36KB的块RAM

双端口,最高支持72bits位宽,可配置为双18Kb,带有可编程的FIFO逻辑电路和内部错误纠正电路。

(三):数字信号处理DSP48E1 Slice

12×18的2进制补码乘法器、累加器,高分辨率(48bit)的信号处理器,带有25-bit的预加器以优化对称结构滤波器应用。

(四)时钟管理单元

超高速缓冲器与低斜率时钟分布的布线,实现频率综合和相移功能,产生低抖动时钟,还带有抖动滤波。

(五)数模转换器XADC

双12-bit、1MSPS,多达17个灵活的、用户可配置的模拟输入,可用于片内或片外测量。带有片内温度传感器(±4℃)和电源供应传感器(±1%)。通过JTAG可获取ADC测量结果。

//

(4)生成IP的output products

(5)创建顶层封装 HDL wrapper

(6)生成bit流文件

(7)export hardware

(8)launch SDK

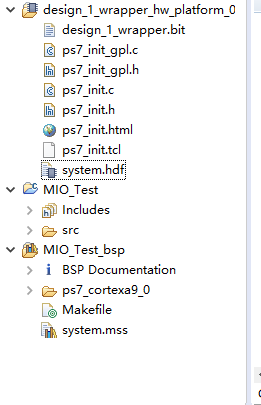

介绍一下裸机应用程序开发流程:

将硬件导入至SDK中,其中硬件平台数据包括:

(1)基于XML的硬件描述文件,描述了处理器、外设、内存映射等系统数据。

(2)bit流文件,包括PL端的编程数据。

(3)块RAM内存映射(BMM)文件。

(4)引导装载(FSBL)所需的PS配置数据。

构成应用程序最底层的库与驱动的集合,称为裸机的板级支持包BSP。裸机程序的应用环境是一个简单的、半托管的单线程环境,提供了一些基本特性,包括:启动代码、缓存函数、异常处理、基本的文件I/O、支持内存分配和其它调用的C语言库、处理器硬件访问宏、定时器函数,以及其它一些支持裸机应用所需的函数。

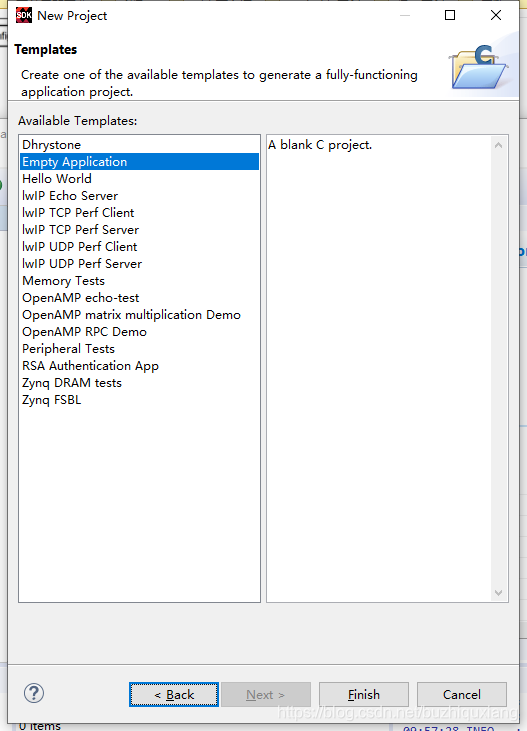

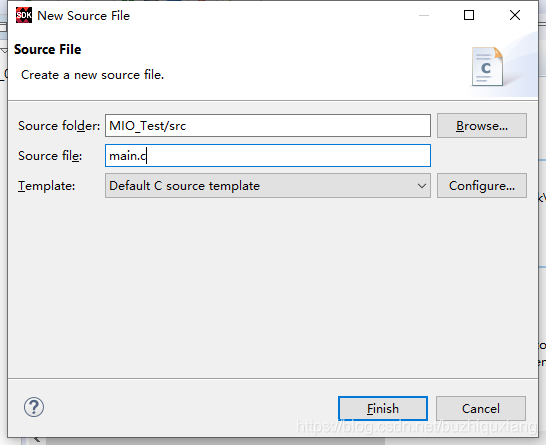

(9)创建裸机应用

SDK提供了几个示例程序,从简单的“Hello World”到复杂的LWIP测试等。在应用程序向导中可以选择并生成这些应用程序。当然也可以创建空白程序,或者将现有的程序导入到裸机BSP中。每个应用程序都要有个相关联的BSP。

(10)构建应用工程

SDK应用工程可以选择用户管理或自动管理;

用户管理需要自己创建makefile并维护。自动管理SDK会创建makefile,自动管理SDK会创建makefiles,当添加或删除源文件时自动更新makefiles,源文件在保存改动时会自动编译,还会自动构建ELF文件。SDK可以根据硬件平台和使用的BSP,推测和设置默认的构建选项,包括编译器、链接器和库路经。

(11)器件编程与应用运行

构建完裸机应用后,用SDK配置PS、对PL编程、运行应用。

SDK使用系统级配置寄存器SLCR配置PS,同时配置数据也会用于FSBL。Bit流和块内存映射数据也会下载到Zynq中,将自定义的设计逻辑加载到PL中,如果仅需要在PS中运行应用,这步便可省略。

下载和运行应用程序的ELF文件时,SDK的Terminal窗口可以通过STDIN和STDOUT和应用程序进行交互。

在main.c中,编写程序如下:

#include "xgpiops.h"

#include "sleep.h"

int main()

{

static XGpioPs psGpioInstancePtr; //指针实例,指向添加进来的GPIO端口,XGpioPs是一个结构体,包含GPIO的一些参数;分别是: 设备的配置、设备是否初始化并准备好、 所有状态的处理程序、 块处理程序的回调、 设备数据、 GPIO 的最大 pin数量和GPIO的最大的 bank 数量。

XGpioPs_Config* GpioConfigPtr;//指针实例,XGpioPs_Config 结构体存放的是 GPIO 的设备地址和基地址。

int iPinNumber= 7; //LD9连接的是MIO7

u32 uPinDirection = 0x1; //1表示输出,0表示输入

int xStatus;

//--MIO的初始化,这段程序是一段查找 GPIO 配置程序。XGpiops_Lookupconfig()这个函数是一个 xilinx 官方提供的 GPIO的查找配置的函数, 程序的参数为要查找的 GPIO 的基地址。 基地址可从 xparameters.h中查看,此处基地址为XPAR_PS7_GPIO_0_DEVICE_ID

GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID);

if(GpioConfigPtr == NULL)

return XST_FAILURE;

xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr,GpioConfigPtr, GpioConfigPtr->BaseAddr);

if(XST_SUCCESS != xStatus)

print(" PS GPIO INIT FAILED \n\r");//查找 GPIO 的配置, 然后判断其是否为空, 若为空则返回查找失败。

//--MIO的输入输出操作

XGpioPs_SetDirectionPin(&psGpioInstancePtr, iPinNumber,uPinDirection);//配置MIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, iPinNumber,1);//配置MIO的第7位输出

/* while(1)

{

XGpioPs_WritePin(&psGpioInstancePtr, iPinNumber, 1);//点亮MIO的第7位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, iPinNumber, 0);//熄灭MIO的第7位输出0

usleep(500000); //延时

}*/

while(1)

{

XGpioPs_WriteReg(0xE000A000,0x00000000, 0xFF7FFFFF&0xFFFF0080);

usleep(500000); //延时

XGpioPs_WriteReg(0xE000A000,0x00000000, 0xFF7FFFFF&0xFFFF0000);

usleep(500000); //延时

}

return 0;

}

(12)debug application

调试应用程序与运行应用程序步骤基本相同,一组窗口提供了完整的调试环境,包括调用堆栈状态、源文件查看、分解器、内存、寄存器、其它一些视图,还有控制台。设计者可以设置断点,控制程序执行。