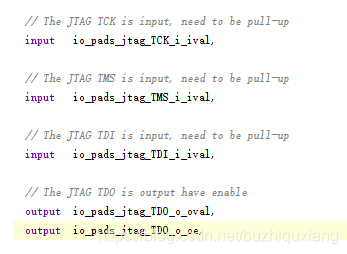

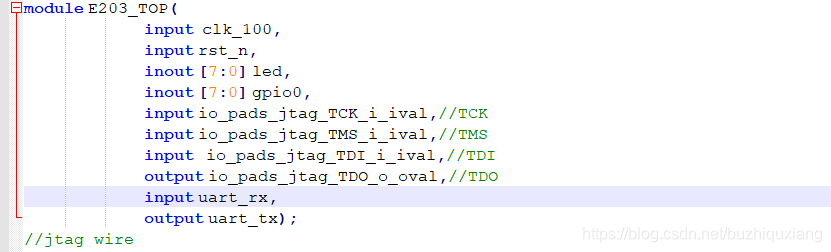

(1) 蜂鸟E203开源SOC中的JTAG代码如下:

根据标准的jtag的引脚,其中必选项有:

5 ->Test Data Input (TDI):TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

7 ->Test Mode Selection Input (TMS):TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。

9 ->Test Clock Input (TCK) :TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

13 ->Test Data Output (TDO) :TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

以及VCC信号与GND信号。

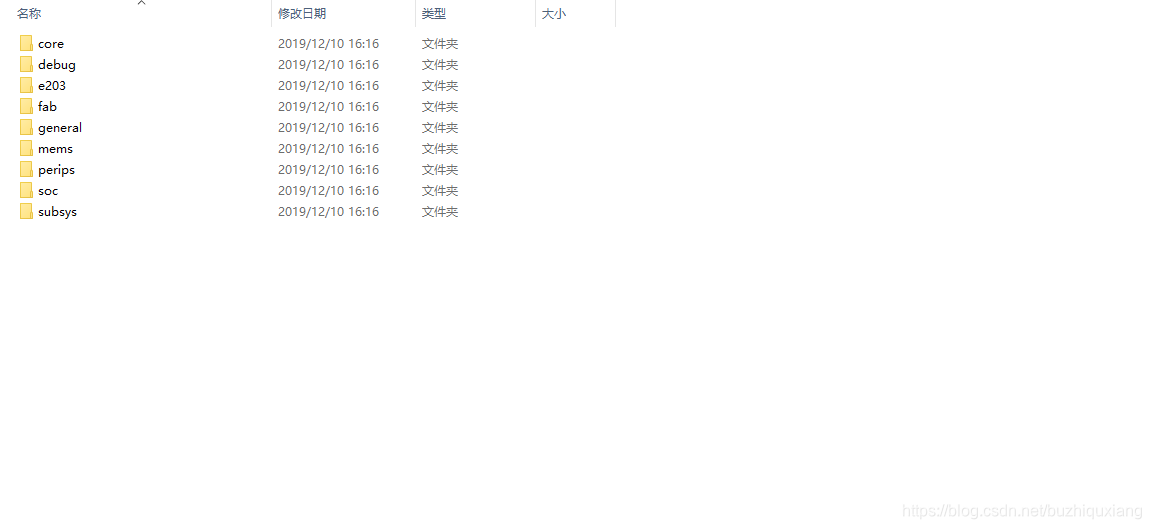

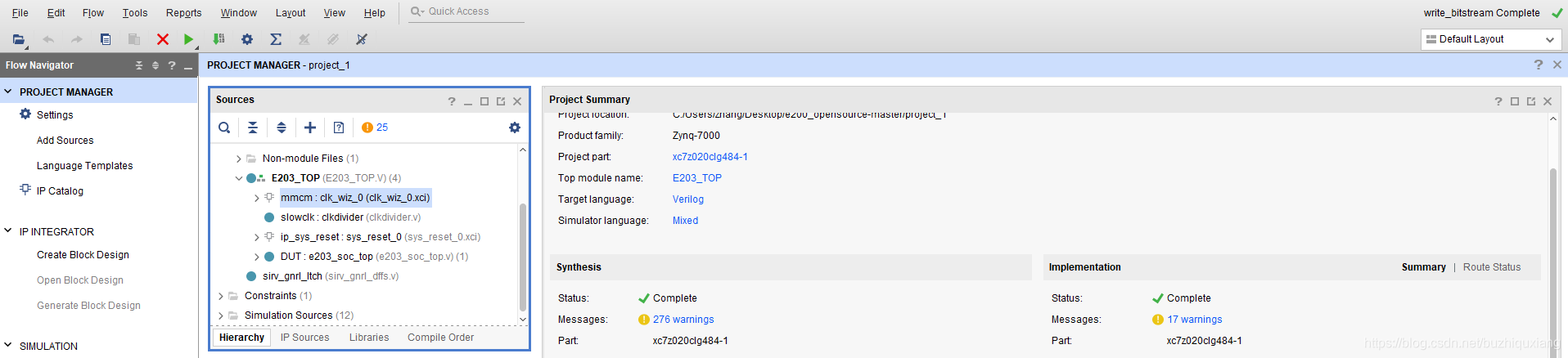

(2)对vivado的文件进行综合

但是由于文件存放在不同文件夹中,会导致找不到include文件(在仿真时也会出现这种情况,对于仿真工具(VCS)的做法,+incdir +inc dir )

解决方法有三种:

(1)将e203_defines.v 设置为set global include ->再将properties 换成

verilog header 即可。

(2)将各个文件夹的.v文件提取出来放入一个文件夹中,这样同样可以避免找不到include文件的问题

(3)将使用include命令改为使用绝对路径对文件进行引用

(3)添加约束文件,由于综合后的IO资源超过板子所拥有的IO资源,需要重新添加一个top文件,减小IO资源的使用。

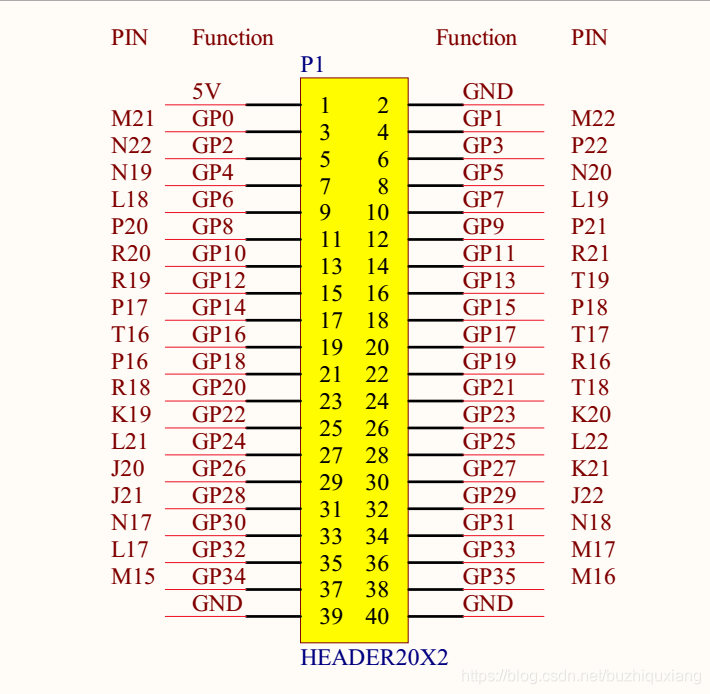

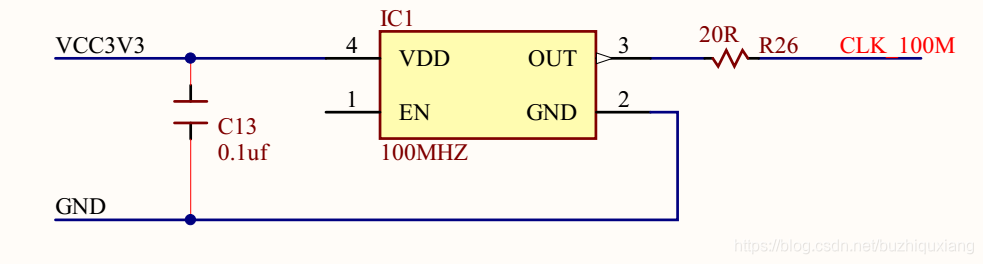

根据自己板子上的原理图添加约束文件。

由于板子上的时钟信号为100MHZ,还需要加入PLL分频(由于需要的一个时钟为32.768KHZ,需要先使用DLL分频为8.388MHZ) 以及全局复位ip,以及uart_tx,uart_rx.

简单解释一下:xilinx clock wizard中MMCM 与PLL 以及DCM和PMCD的时钟资源,(PLL会一直存储相位和频率信息,而DLL只存储相位信息)

(1)DCM ->内含DLL,DLL(delay lock loop),主要是用于产生一个时间延迟,使两路信号的相位一致。

(2)PLL ->(Phase locked loop)除了用作相位跟踪,还可以用来做频率综合,可以产生不同频率的信号。

(3)MMCM相当于PLL+DCM ,( This is a PLL with some small part of a DCM tacked on to do fine phase shifting (that’s why its mixed mode - the PLL is analog, but the phase shift is digital). Thus the MMCM can do everything the PLL can do plus the phase shifting from the DCM.)。

(4)相位匹配时钟分频器(PMCD):生成相位匹配的分频输入时钟信号,于分频时钟的DCM频率综合类似。

所添加top文件的端口如下:

其中由于使用到inout端口,所以使用了IO_BUF的原语

wire iobuf_gpio_0_o;

IOBUF

#(

.DRIVE(12),//Specify the output drive strength

.IBUF_LOW_PWR("TRUE"),//Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD("DEFAULT"),//Specify the I/O standard

.SLEW("SLOW")//Specify the output slew rate

)IOBUF_gpio_0

(

.O(iobuf_gpio_0_o),//Buffer output IO_pad输入

.IO(gpio_0),//Buffer inout port (connect directly to top-level port)

.I(io_pads_gpio_0_o_oval),//Buffer input IO_pad输出

.T(io_pads_gpio_0_o_oe));//3-state enable input, high=input, low=output

assign io_pads_gpio_0_i_ival=iobuf_gpio_0_o&io_pads_gpio_0_o_ie;

约束文件如下:

set_property PACKAGE_PIN M19 [get_ports {clk_100}]

set_property IOSTANDARD LVCMOS33 [get_ports {clk_100}]

set_property PACKAGE_PIN AA19 [get_ports {rst_n}]

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

set_property PACKAGE_PIN AA14 [get_ports { led[0] }]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN W15 [get_ports { led[1] }]

set_property IOSTANDARD LVCMOS33 [get_ports { led[1] }]

set_property PACKAGE_PIN Y15 [get_ports { led[2] }]

set_property IOSTANDARD LVCMOS33 [get_ports { led[2] }]

set_property PACKAGE_PIN AB14 [get_ports { led[3] }]

set_property IOSTANDARD LVCMOS33 [get_ports { led[3] }]

set_property PACKAGE_PIN AB15 [get_ports { led[4] }]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property PACKAGE_PIN W16 [get_ports { led[5] }]

set_property IOSTANDARD LVCMOS33 [get_ports { led[5] }]

set_property PACKAGE_PIN Y16 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property PACKAGE_PIN U15 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property PACKAGE_PIN M21 [get_ports { gpio0[0] }]

set_property IOSTANDARD LVCMOS33 [get_ports { gpio0[0] }]

set_property PACKAGE_PIN M22 [get_ports { gpio0[1] }]

set_property IOSTANDARD LVCMOS33 [get_ports { gpio0[1] }]

set_property PACKAGE_PIN N22 [get_ports { gpio0[2] }]

set_property IOSTANDARD LVCMOS33 [get_ports { gpio0[2] }]

set_property PACKAGE_PIN P22 [get_ports { gpio0[3] }]

set_property IOSTANDARD LVCMOS33 [get_ports {gpio0[3]}]

set_property PACKAGE_PIN N19 [get_ports { gpio0[4] }]

set_property IOSTANDARD LVCMOS33 [get_ports {gpio0[4]}]

set_property PACKAGE_PIN N20 [get_ports { gpio0[5] }]

set_property IOSTANDARD LVCMOS33 [get_ports {gpio0[5]}]

set_property PACKAGE_PIN L18 [get_ports { gpio0[6] }]

set_property IOSTANDARD LVCMOS33 [get_ports {gpio0[6]}]

set_property PACKAGE_PIN L19 [get_ports { gpio0[7] }]

set_property IOSTANDARD LVCMOS33 [get_ports {gpio0[7]}]

set_property PACKAGE_PIN M15 [get_ports { uart_rx }]

set_property IOSTANDARD LVCMOS33 [get_ports { uart_rx }]

set_property PACKAGE_PIN M16 [get_ports { uart_tx }]

set_property IOSTANDARD LVCMOS33 [get_ports { uart_tx }]

set_property PACKAGE_PIN R20 [get_ports {io_pads_jtag_TCK_i_ival}]

set_property IOSTANDARD LVCMOS33 [get_ports {io_pads_jtag_TCK_i_ival}]

set_property PACKAGE_PIN R21 [get_ports {io_pads_jtag_TMS_i_ival}]

set_property IOSTANDARD LVCMOS33 [get_ports {io_pads_jtag_TMS_i_ival}]

set_property PACKAGE_PIN R19 [get_ports {io_pads_jtag_TDI_i_ival}]

set_property IOSTANDARD LVCMOS33 [get_ports {io_pads_jtag_TDI_i_ival}]

set_property PACKAGE_PIN T19 [get_ports {io_pads_jtag_TDO_o_oval}]

set_property IOSTANDARD LVCMOS33 [get_ports {io_pads_jtag_TDO_o_oval}]

(4)生成bit流,下载开发板